1. 實驗引言

在電子系統中,通常都需要有輸出設備來輸出或顯示一定的信息,以指示當前系統運行的狀態。在以單片機和 ARM 為主的電子系統中,液晶屏是理想的輸出設備。而 FPGA 則因為其獨特的硬件結構,如果用 RTL 級電路來驅動彩色液晶屏來顯示一定的數據,勢必是非常不劃算的選擇,而且驅動也極為復雜。數碼管作為一種能夠直觀顯示一定數據信息的輸出設備,具有驅動簡單、顯示直觀的特點,尤其適合作為 FPGA 系統的輸出設備。本節,我們就將和大家一起進行數碼管驅動的開發。

2. 實驗目的

實現 6 位 7 段數碼管的驅動,待顯示數據以 BCD 格式輸入。數碼管刷新時鐘為 1KHz。實驗使用了 4 個獨立按鍵作為輸入,通過按鍵來改變需要數碼管顯示的數據,以驗證數碼管驅動的正確性,同時也可檢驗獨立按鍵消抖模塊的可靠性。

3. 實驗內容

本實驗的內容是數碼管動態掃描驅動的設計,通過外部四位按鍵的不同操作來驅動數碼管顯示不同的值。

4. 實驗原理

數碼管所謂的動態掃描,就是利用人眼的視覺暫留特性,在人眼能分辨的變化速度以外,快速分時的點亮各個數碼管及其對應的段。因為分別點亮所有數碼管一次所用時間小于人眼的視覺暫留,因此,在人們眼里看來,這些數碼管都是同時持續點亮的,并不會有閃爍的感覺。

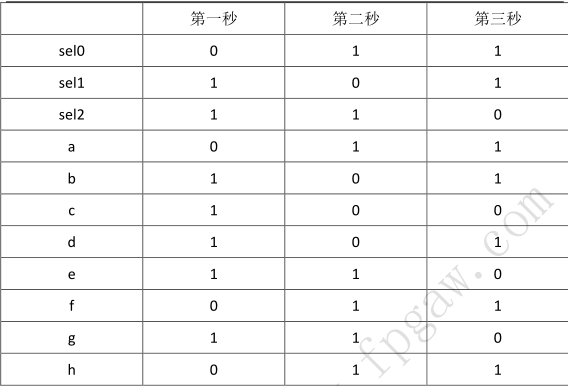

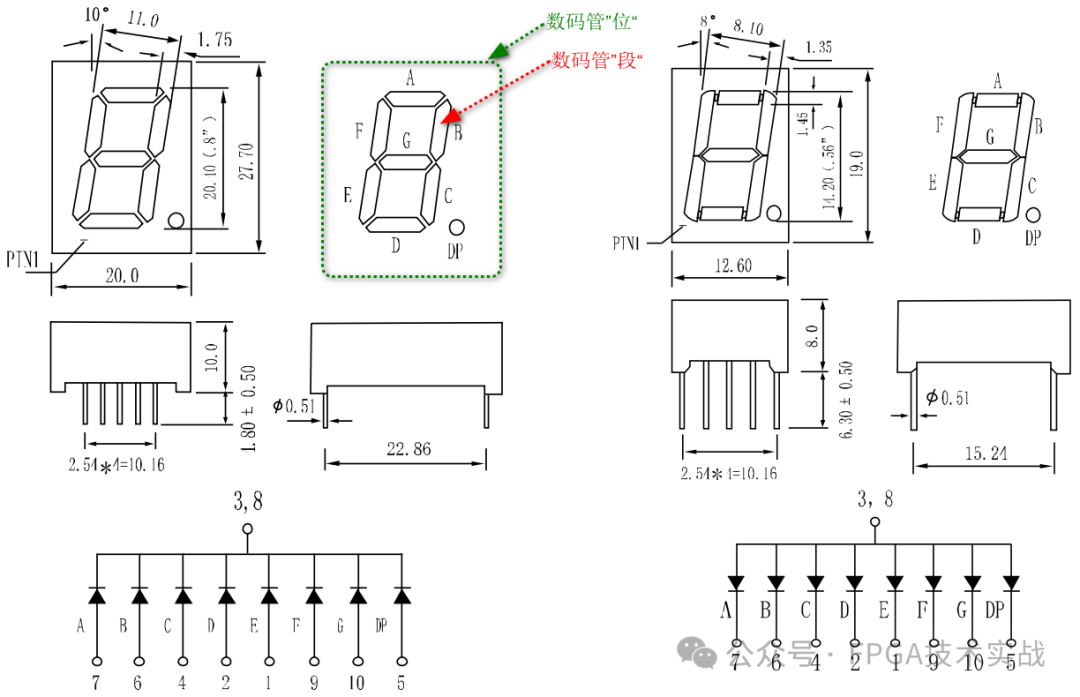

圖 1 為 3 位 7 段數碼管的等效電路圖,在這個圖中,可以明顯的看到 24個發光二極管被分為了三組,每一組的 8 個發光二極管正極被接在了一起,通過一個三極管與 VCC 相連。三極管的基極連接到了 FPGA 的 IO 上,因此,只需要 FPGA 對應的 IO 上給出低電平,三極管便會導通。而三組 LED 中所有的相同編號的 LED 的負極被連接在了一起,并接到了 FPGA 的 IO 上。如果我們希望將最左邊一組的 led0、led5、led7 三個編號的 led 燈點亮,其它 led 不亮,則只需要給 Q0 的基極(sel0)連接上低電平,并將 led0、led5、led7 的負極(a、f、h)連接上低電平,其它所有端口都輸出高電平,則最左邊一組的對應的三個 led 燈就會被點亮,而其它 led 則會處于熄滅狀態。 假如我們需要在三秒時間內,完成以下三次操作:第一次操作,點亮最左邊一組 led 燈的 led0、led5、led7;第二次操作,點亮中間一組 led 燈的 led1、led2、led3;第三次操作,點亮最右邊一組 led 燈的 led2、led4、led6;那么我們只需要按照如下表格中列出的真值表操作即可:

按照以上表格,我們就能知道該如何操作了,只需要在不同的時間給各個 IO 不同的電平,便能實現我們想要的亮滅組合。以上我們是以 1 秒為單位進行 led 組的切換的,假如我們將切換速度加快,變為 1 毫秒一切換,會是什么情況呢?在 1 毫秒一切換的速度下,完成所有操作所需時間為 3ms,遠遠超出了我們人眼所能辨識的變化速度范圍。如果我們讓以上三個操作永遠循環的進行下去,那么我們將看見三組 led 燈中,我們點亮的那幾個 led 是同時且一直處于亮著的狀態的,這便是動態掃描的原理,假如我們把每個 led做成一個長條型的,并按照如下形狀擺放,便就是我們常見的數碼管了。

5. 硬件設計

在這個圖中,共有 6 位數碼管,每個數碼管的正極被接在一個驅動三極管上,三極管的基極連接到三八譯碼器的 Y 端,則 FPGA 只需要三個引腳就可最多控制 8 個數碼管的位選。數碼管的段選在串接了 470 歐姆的電阻后與FPGA 的 IO 相連。這里 470 歐姆的電阻主要起到限流的作用,保證流過數碼管的電流在正常范圍內。

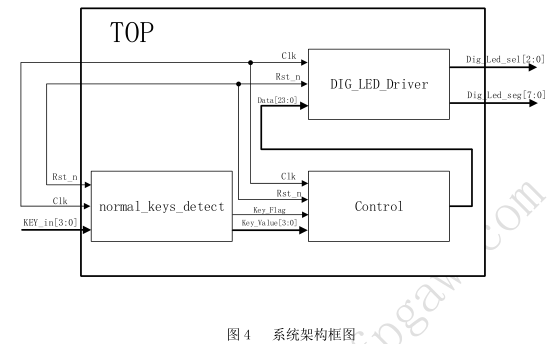

6. 系統結構框圖

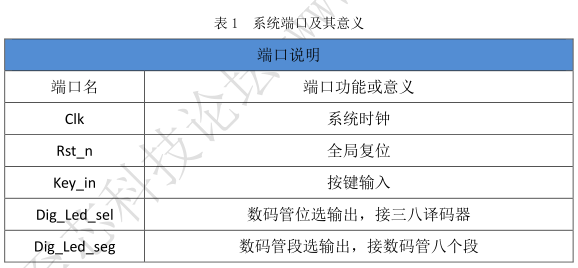

系統端口及其意義如下:

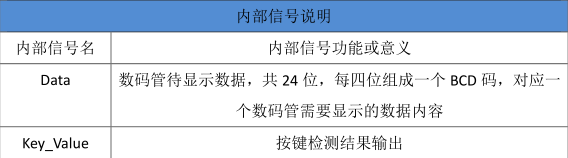

內部信號及其意義如下:

7. 代碼解釋

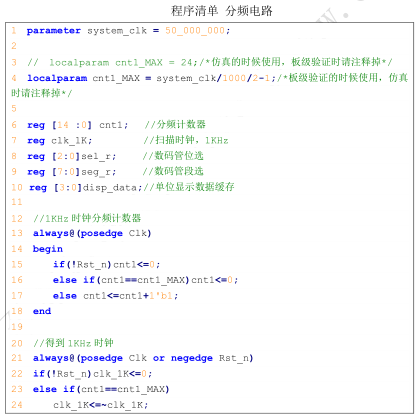

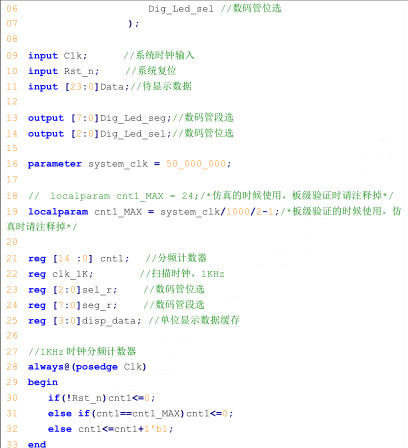

因為數碼管屬于低速設備,其正常的掃描頻率為 500~10KHz,掃描頻率太快,會導致系統功耗增加,顯示效果變暗。掃描頻率太慢,會有明顯的閃爍感。本實驗通過調試觀察,選擇以 1KHz 作為掃描頻率,實際顯示效果非常好。 因此本實驗首先就需要產生一個 1KHz 的掃描時鐘,該時鐘由系統時鐘分頻得到。產生 1KHz 掃描時鐘的代碼如下:

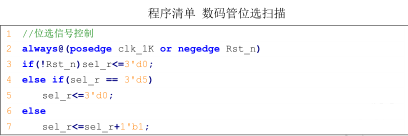

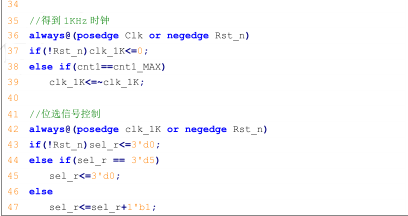

其中,定義了一個全局參數 system_clk,該參數為 Clk 的頻率,不同的時鐘頻率,只需要更改該參數,就可改變分頻計數器的最大計數值,以保證 1KHz分頻的精準性。 在驅動中,數碼管的位選以掃描時鐘的速率進行切換,因為只有 6 位數碼管,因此當位選計數到 6-1 后必須清零從頭開始計數。相關代碼如下:

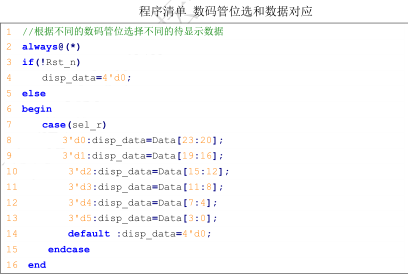

每個數碼管需要顯示的內容都不相同,由 Data 中相應的位指定,Data中各位與數碼管的位對應關系如下:

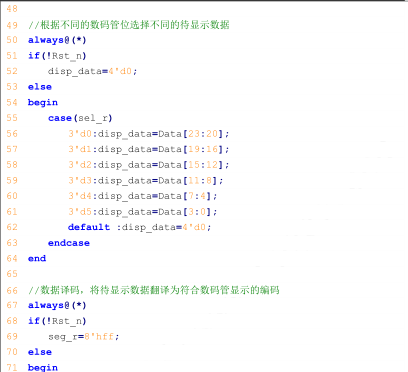

因此需要從 Data 中將每個數碼管被選中時需要顯示的數據提取出來,提取數據的代碼如下所示:

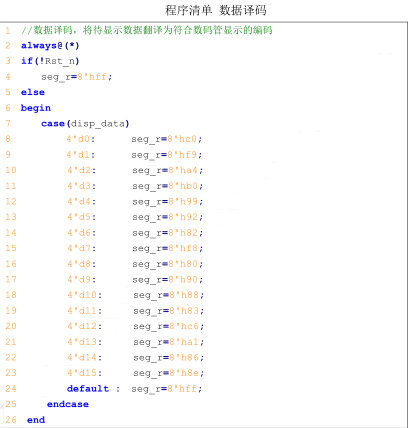

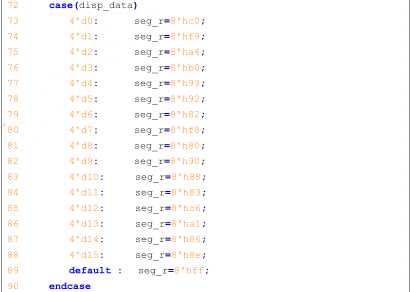

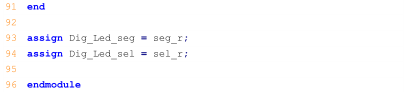

因為提取出來的數據還是 BCD 碼的形式,還需要將 BCD 碼對應的數據翻譯成為數碼管顯示對應字符時應該點亮或熄滅的對應的 LED 的控制信號,因此必須還有一個 BCD 碼譯碼的過程,該過程代碼如下所示:

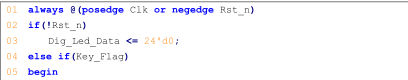

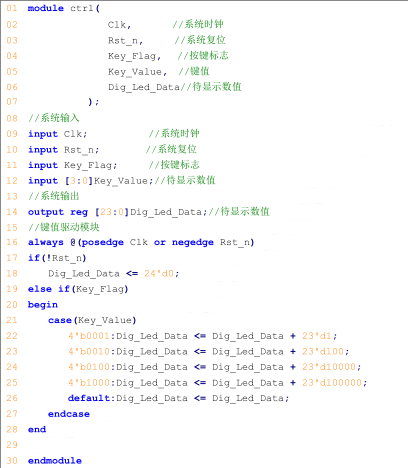

控制部分相對簡單,只需要根據對應的 按鍵信息,給待顯示的數據加上一個對應的值,該部分代碼如下所示:

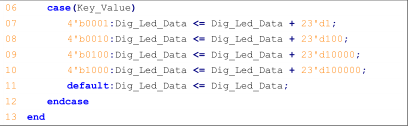

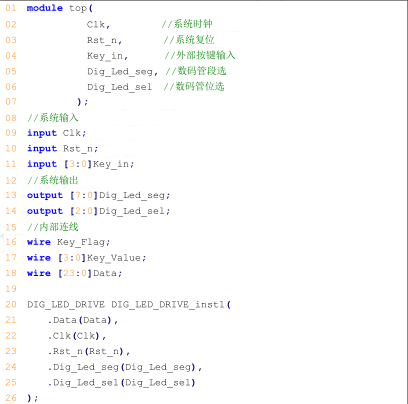

8. 程序清單

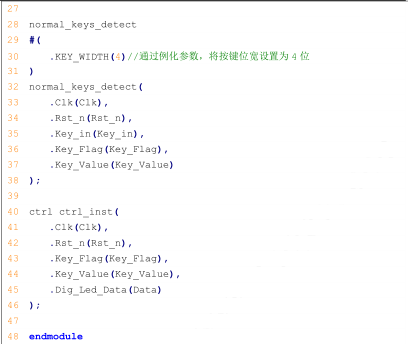

(1)工程頂層模塊(文件名 top.v) 該模塊為工程頂層模塊,負責將按鍵檢測模塊(normal_keys_detect.v)、顯示控制模塊(ctrl.v)、數碼管驅動模塊(DIG_LED_DRIVE.v)按照邏輯關系級聯。

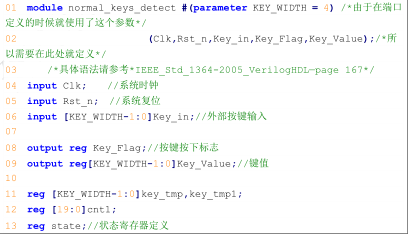

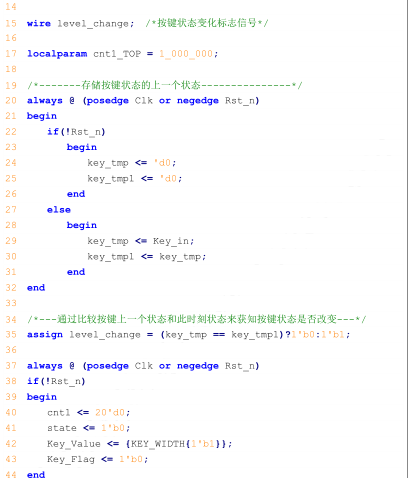

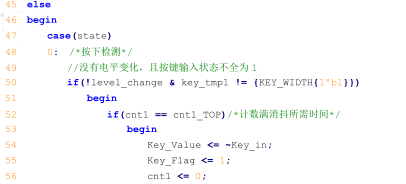

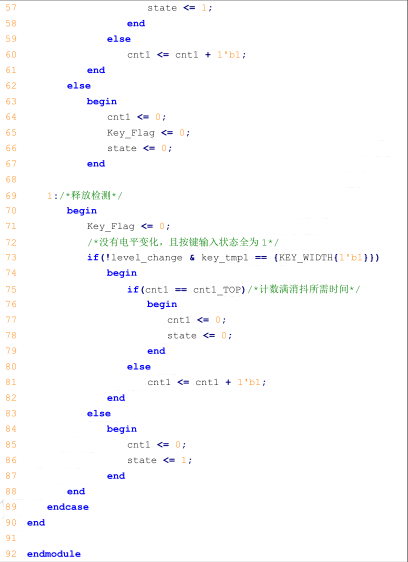

(2) 按鍵檢測模塊(文件名 normal_keys_detect.v) 該模塊為按鍵檢測模塊,負責檢測外部按鍵值,并完成按鍵消抖,輸出按鍵檢測標志。

(3) 控制模塊(文件名 ctrl.v) 該模塊為數碼管顯示控制模塊,通過檢測到的鍵值驅動數碼管顯示出不同的值。

(4) 數碼管顯示驅動模塊(文件名 DIG_LED_DRIVE.v) 該模塊為數碼管顯示驅動模塊,負責將輸入的數據正確顯示到數碼管對應位。

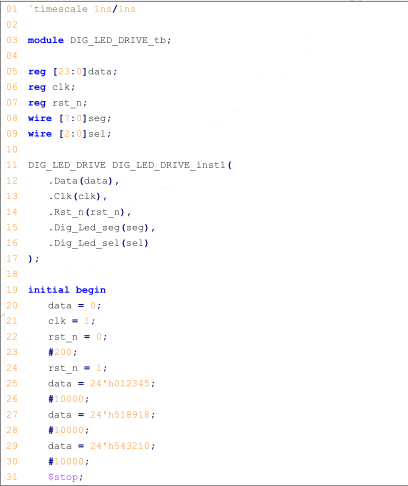

(5) 測試仿真模塊(文件名 DIG_LED_DRIVE_tb.v) 該模塊為數碼管顯示驅動測試模塊,用于仿真查看數碼管驅動邏輯是否正確。

責任編輯:lq6

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606065 -

單片機

+關注

關注

6043文章

44621瀏覽量

638628 -

ARM

+關注

關注

134文章

9169瀏覽量

369250 -

數碼管

+關注

關注

32文章

1887瀏覽量

91410

原文標題:至芯入門實驗| 基于 FPGA 的數碼管動態掃描驅動設計

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數碼管的結構與原理

共陽極數碼管的結構和功能

簡述led數碼管的類型和顯示原理

數碼管顯示屏的靜態顯示編程是什么

驅動器數碼管顯示不良原因

數碼管驅動芯片原理是什么

數碼管驅動芯片有哪幾種

LED數碼管的顯示方式和驅動方式

TM1617能驅動共陽數碼管嗎?

51單片機數碼管靜態顯示

深入學習基于FPGA的數碼管動態掃描驅動設計

深入學習基于FPGA的數碼管動態掃描驅動設計

評論