何為信號完整性?

信號完整性(SignalIntegrity)就是指電路系統中信號的質量,如果在要求的時間內,信號能不失真地從源端傳輸到接收端,我們就稱該信號是完整的。

從廣義上講,信號完整性指的是在高速電路設計中由互連線所引起的所有信號問題,包括噪聲、串擾、反射、地彈、時序和阻抗等。

信號具備信號完整性,是指接收端能夠收到符合邏輯電平要求、時序要求和相位要求的信號。在系統互連的設計中,需要研究互連線、傳輸的信號、過孔、連接器以及器件之間的互相影響。

對信號完整性的研究,可以歸納為以下四類:

單一網絡的信號完整性問題;

兩個或者多個網絡間的串擾;

電源和地分配網絡中的軌道塌陷;

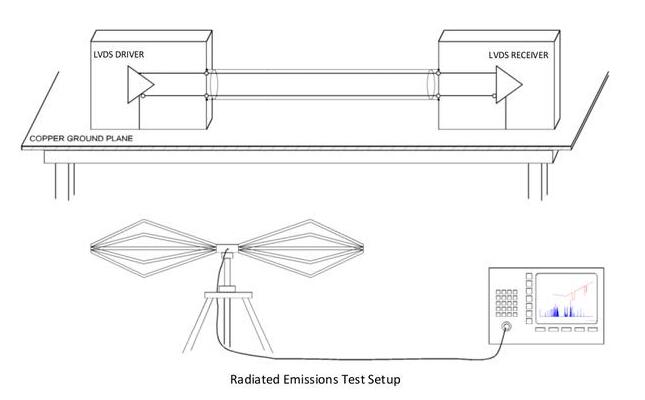

來自整個系統的電磁干擾和輻射。

2、信號完整性產生原因

從信號完整性的根源上考慮,可以將產生信號完整性的原因分為以下幾個:

1)信號上升時間變短。信號的上升時間變短,從頻域的角度看,信號的帶寬變寬,信號所對應的最高截止頻率就變高,過高的信號頻率在信號傳輸過程中主要變現為振鈴、反射、串擾、地彈和電磁輻射等。從能量守恒的角度來看,高頻部分的能量過多的消耗在信號傳輸路徑上,從而導致接收端接收到的能量達不到閾值,不能達到datasheet要求的正確邏輯電平,從而就會導致邏輯電平的傳輸錯誤。

2)芯片的工作電壓變低,噪聲容限變小。隨著半導體和封裝技術的迅速發展,芯片的速度和低功耗要求更高,使得芯片的供電電壓正在變得越來越低,從而導致其噪聲容限變得越來越小,噪聲容限變小,使得信號在遇到信號完整性的問題時,更容易出現電平值的錯誤翻轉。

3)PCB器件布局及布線密度越來越高,寄生效應增強,串擾加大。隨著現在集成電路的集成度越來越高,功能越來越復雜,相應地要求集成電路封裝密度也越來越大,引線數越來越多,而體積越來越小,就導致PCB布局和布線的密度就不斷加大。因為互連和器件的封裝所帶來的容性和感性的寄生效應越來越嚴重,加大了信號彼此之間的干擾,不僅同平面的信號和器件之間相互影響,相鄰層面的信號之間的影響也越來越嚴重。

4)電源和地噪聲所帶來的信號高低電平閾值范圍的縮小。在高頻PCB板中,較重要的一類干擾便是電源噪聲,電源和地平面的噪聲來源主要有VRM、CoreIO跳變帶來的噪聲、平面諧振噪聲、臨近電源耦合的噪聲和其他耦合的噪聲等。所以應該盡可能減小電源的阻抗,最好有專門的電源層和接地層,這樣回路總可以沿著阻抗最小的路徑走,這樣可以最小化信號回路,從而減小噪聲。

信號的傳輸需要一個參考平面,當參考平面上有波動的噪聲時,走線所參考的電動勢也相應會發生變化,即信號所呈現的電平值是一個波動的范圍。因為參考平面上噪聲的存在,所以高低電平的閾值范圍就會減小,甚至發生錯誤的翻轉。又因為電源噪聲的影響,使信號的噪聲容限和時序容限變小,并帶來一定的EMI干擾。

3、結語:

對信號完整性問題的研究,總的來說就是需要保證信號傳輸波形的完整和信號時序的完整。更進一步,如果對阻抗有更深入的理解,把器件之間互連線的物理設計和互連線的阻抗聯系起來,就可以在PCB設計的過程中,從根本上對信號完整性問題進行量化分析,就能夠消除很多潛在的信號完整性問題。

對于四類信號完整性問題,為了保證信號傳輸的質量,工程師在設計PCB走線時需要注意以下幾點要求:

PCB走線時使信號在整個互連線平面的阻抗相同,PCB走線中要盡量避免直角和銳角走線,防止由于阻抗不連續造成信號的反射,產生EMI;

為減少網絡之間的串擾,應盡量加大走線之間的距離(差分線除外),并使走線與其非理想的返回路徑之間的互感最小,可以有效的抑制串擾;

設計層疊時,在滿足阻抗要求的條件下,應盡量使信號層靠近參考面,使得傳輸線可以緊密的與參考面進行耦合,從而減少相鄰信號線間的串擾;

在布線空間允許的條件下,在串擾比較嚴重的兩條信號線之間插入一條地線,可以減少兩條信號線間的耦合,從而減小串擾;

為了減少軌道塌陷的幅度,需要使電源/地路徑的阻抗盡量減小,必要時電源與地平面之間可添加符合諧振特性的去耦電容,減小EMI噪聲;

為減小電磁干擾,應盡量減小傳輸信號的帶寬,并盡量使地阻抗達到最小。

在進行PCB設計時考慮到PCB設計的實際操作,在操作中需要考慮的因素主要有PCB的疊層架構、阻抗、器件互連的拓撲結構、延遲、串擾、反射、地彈、時序、電源完整性和電磁干擾分析(EMC和EMI)等。

責任編輯人:CC

-

信號完整性

+關注

關注

68文章

1417瀏覽量

95633

發布評論請先 登錄

相關推薦

信號完整性為什么寫電源完整性?

聽懂什么是信號完整性

信號完整性產生的原因是什么

信號完整性產生的原因是什么

評論