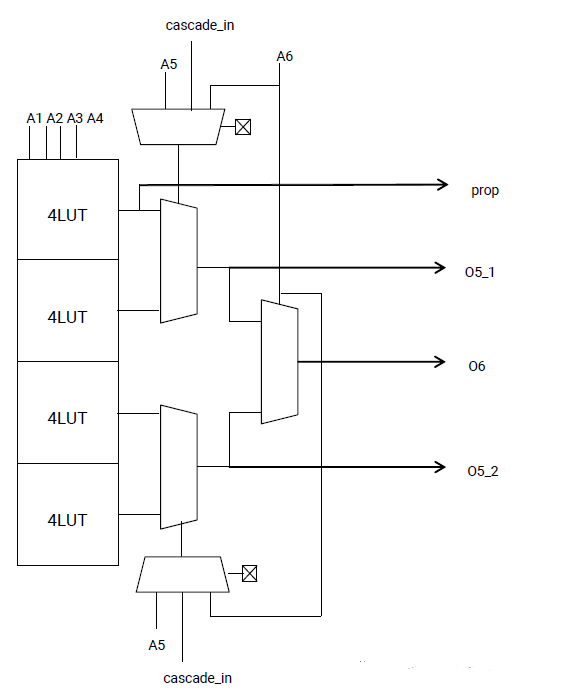

在Versal ACAP中,同一個CLB內(nèi)同一列的LUT是可以級聯(lián)的,這是與前一代FPGA UltraScale+系列的一個顯著不同點(diǎn)。這里我們先看看Versal中LUT的結(jié)構(gòu),如下圖所示(圖片來源:Figure4, am005)。

可以看到,一個LUT6(6輸入LUT)是由4個LUT4(4輸入LUT)外加一些MUX(數(shù)據(jù)選擇器)共同構(gòu)成。同時,LUT6有4個輸出端口。其中,prop端口只有在LUT用作進(jìn)位邏輯時使用,且在CLB外部不可見。用做6個輸入的邏輯函數(shù)發(fā)生器時,輸出在O6端口;雙LUT5模式時,輸出在O5_1和O5_2端口。同時還可以注意到,多了一個級聯(lián)端口cascade_in,該端口用于與前一級LUT的O6輸出相連接。級聯(lián)端口不需要手工連接,工具會自動判斷是否使用該端口。

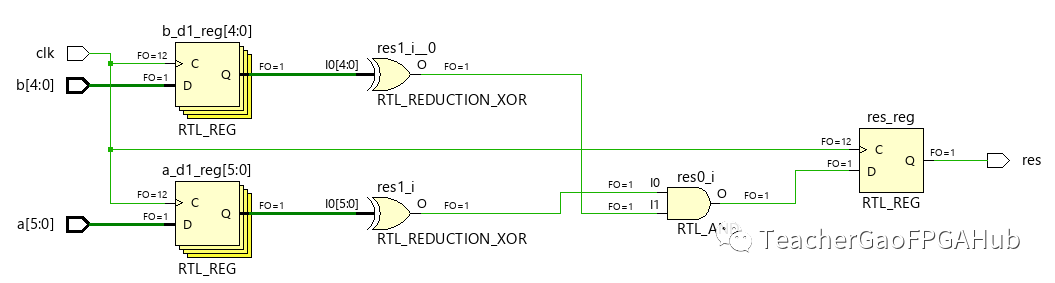

我們看一個具體的案例,如下圖所示。輸入a為6bits,b為5bits,a/b分別執(zhí)行異或位縮減運(yùn)算(^a,^b),然后再將兩者結(jié)果執(zhí)行邏輯與。顯然a的異或位縮減運(yùn)算會占用一個LUT6,b的異或位縮減運(yùn)算與后續(xù)的與門共同消耗一個LUT6。

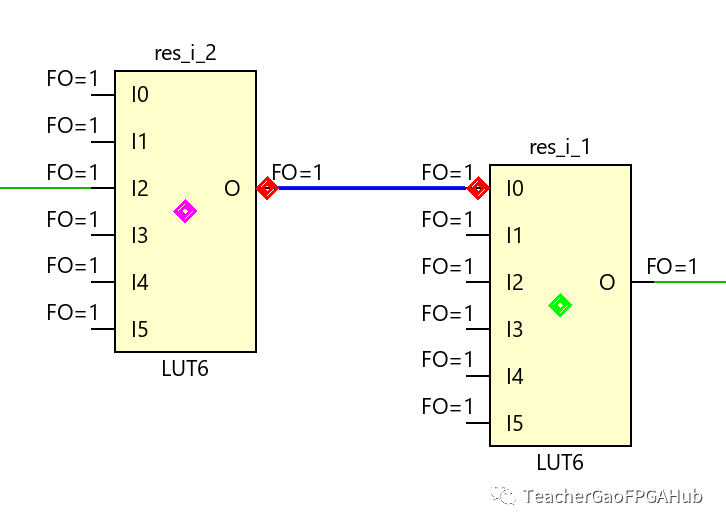

上述電路圖布線后打開Schematic視圖,鎖定其中的兩個LUT6,如下圖所示。

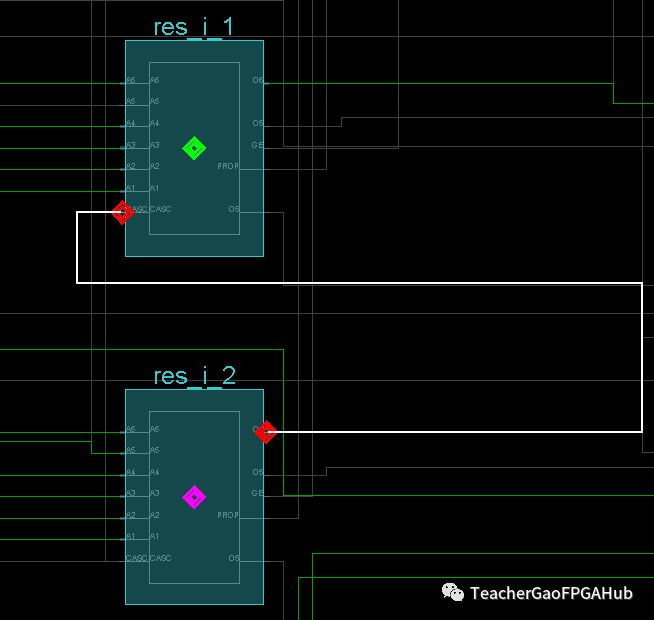

進(jìn)一步在Device視圖中可以看到具體的物理連接方式,如下圖所示。可以看到圖片下方的LUT由O6輸出,并連接到上方LUT的級聯(lián)端口。

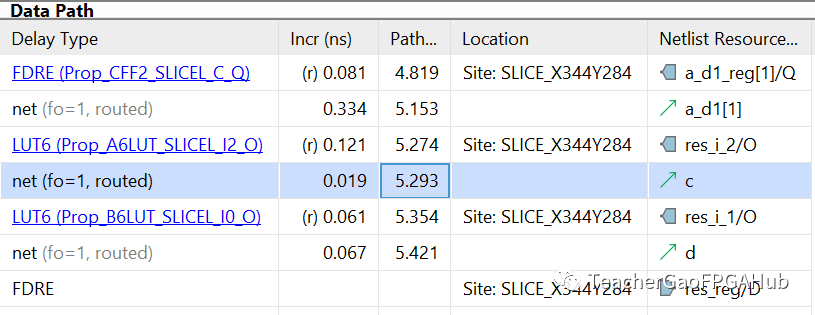

再從時序角度看,這里我們設(shè)定時鐘頻率為600M,在時序報告中,可以看到這部分的延遲(兩個LUT之間的布線延遲)為0.019ns。整個設(shè)計的WNS為0.923ns。

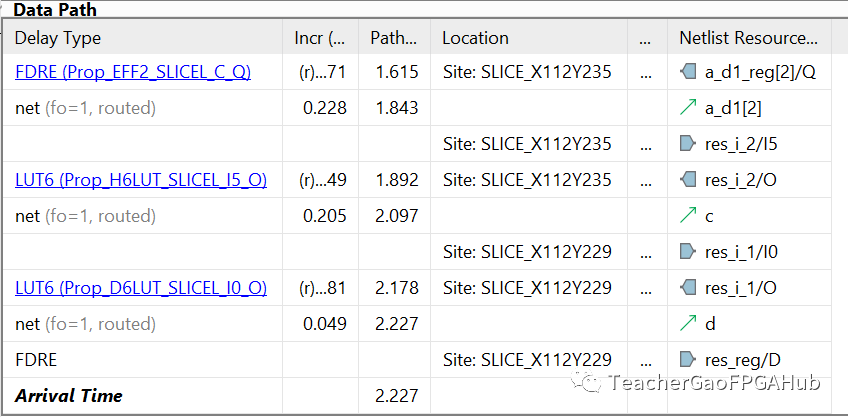

同樣的設(shè)計,如果在UltraScale+中執(zhí)行,結(jié)果如下圖所示,可以看到兩個LUT相距很遠(yuǎn),因為UltraScale+中的LUT是不支持級聯(lián)的,這就要消耗CLB外部的布線資源。

從時序角度看,這部分的延遲為0.205ns,顯然大了很多。

綜上所示,我們可以得出如下結(jié)論:

LUT的級聯(lián)可以有效降低關(guān)鍵路徑上的延遲,同時減少CLB外部布線資源的消耗。這對于緩解布線擁塞非常有利。還要注意的是這種級聯(lián)僅限于同一個CLB中的同一列LUT,且級聯(lián)方向由下至上,這意味著級聯(lián)所用到的布線資源都在CLB內(nèi)部,而不會消耗CLB外部布線資源。

編輯:jq

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606022 -

LUT

+關(guān)注

關(guān)注

0文章

50瀏覽量

12577 -

CLB

+關(guān)注

關(guān)注

0文章

29瀏覽量

5981

原文標(biāo)題:物理可級聯(lián)的LUT到底有什么優(yōu)勢?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

XILINX FPGA CLB單元之移位寄存器

ADS126x與ADS1256比較優(yōu)勢在哪里?

HD3SS6126用于USB3.0信號切換,是否可以級聯(lián)是用,最多可以級聯(lián)幾級?

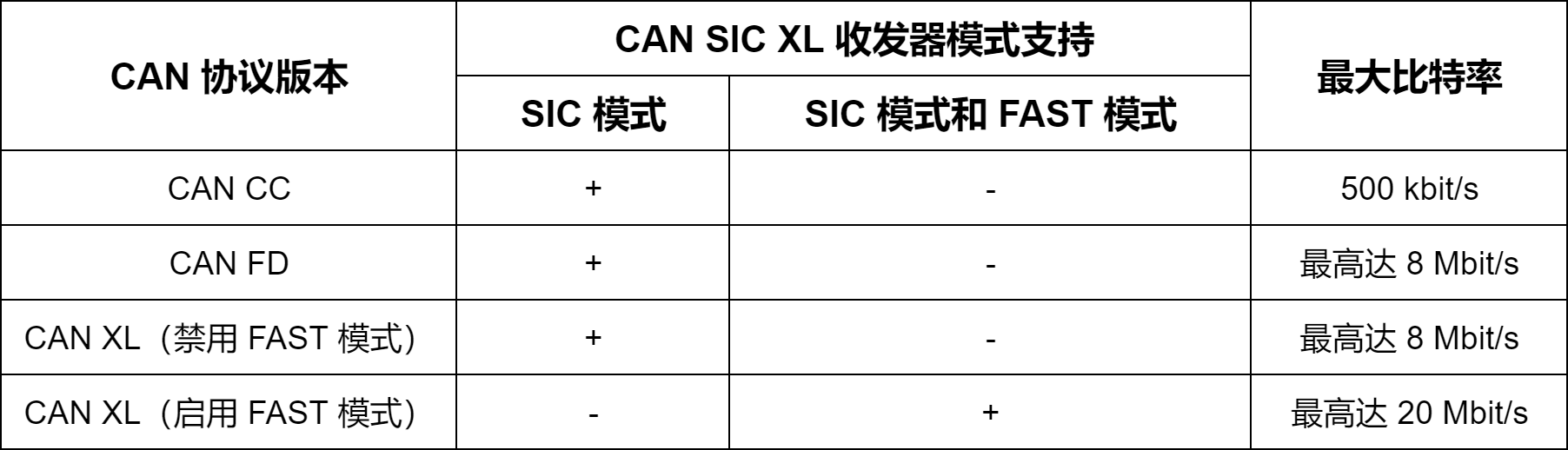

CAN XL物理層揭秘(下):物理層組合與兼容性

ADS1299的配套軟件不支持讀取級聯(lián)的其他芯片的數(shù)據(jù),如何實(shí)現(xiàn)讀取級聯(lián)的多個芯片的數(shù)據(jù)呢?

VCA810和其他運(yùn)放級聯(lián)的時候有什么參數(shù)要求啊?

級聯(lián) LMX1204 相位誤差分析

級聯(lián)一致性和移相器校準(zhǔn)應(yīng)用手冊

物理可級聯(lián)的LUT的優(yōu)勢在哪?

物理可級聯(lián)的LUT的優(yōu)勢在哪?

評論