引言:晶振是數字電路設計中非常重要的器件,時鐘的相位噪聲、頻率穩定性等特性對產品性能影響很大。本文基于可編程晶振SI570,就Xilinx FPGA收發器輸入參考時鐘的硬件設計及FPGA軟件設計給出設計案例,供大家參考。通過本文,可以了解到:

Xilinx FPGA收發器參考時鐘設計要點

可編程晶振SI570設計方法

1.Xilinx FPGA收發器參考時鐘設計要求

1.1參考時鐘接口要求

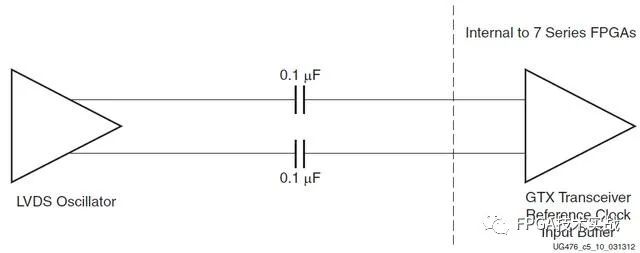

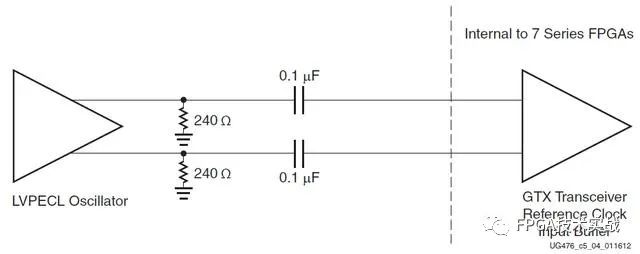

FPGA收發器GTX/GTH參考時鐘接口提供兩種連接方式:LVDS(如圖1所示)和LVPECL(如圖2所示)。我們在選擇晶振時,至少要支持其中一種接口輸出電平標準。圖2所示的電阻值為一般推薦值,實際偏置電阻值需要參考晶振手冊。圖1和圖2中交流AC耦合電容作用:1)阻斷外部晶振和GTX/GTH收發器Quad專用時鐘輸入管腳之間的DC電流,降低功耗;2)AC耦合電容和參考時鐘輸入端接構成高通濾波器,衰減參考時鐘偏移;3)保持耦合電容兩側共模電壓獨立,互不干擾。

圖1、LVDS晶振和7系列FPGA收發器參考時鐘輸入接口

圖2、LVPECL晶振和7系列FPGA收發器參考時鐘輸入接口

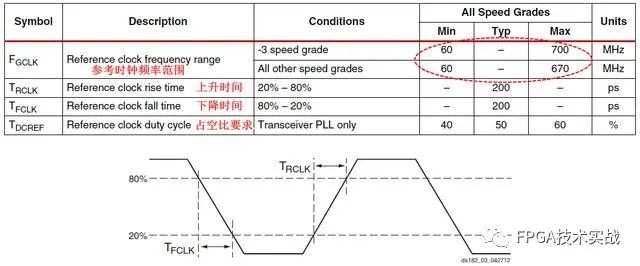

1.2參考時鐘電氣特性要求

FPGA收發器參考時鐘開關特性和DC特性要求分別如圖3和圖4所示。

圖3、FPGA收發器參考時鐘開關特性要求

圖4、FPGA收發器參考時鐘DC特性要求

2.硬件電路設計

2.1晶振選型

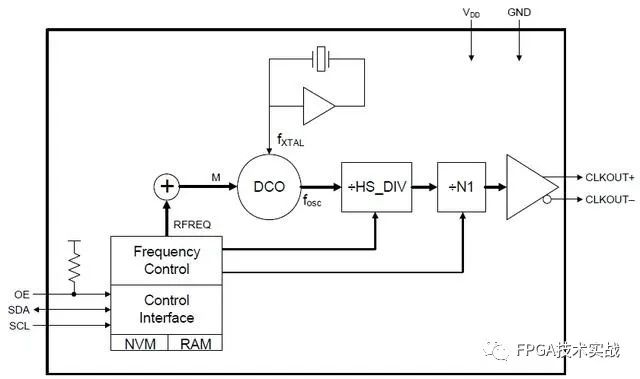

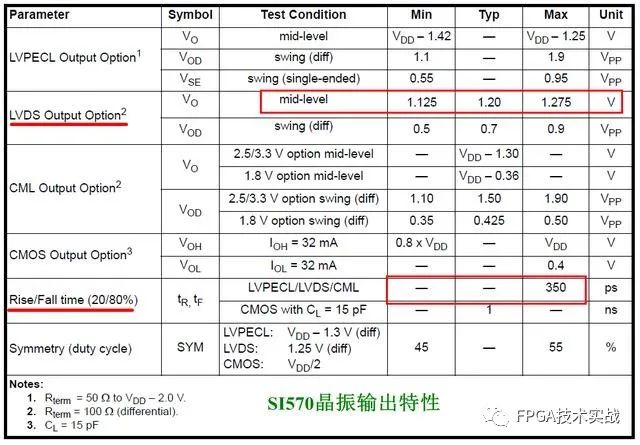

按照章節1中FPGA收發器參考時鐘要求,我們選擇Silicon labs公司的si570系列可編程晶振,該晶振典型應用SONET/SDH、10G以太網通信、時鐘恢復等場合。該晶振輸出特性如圖6所示。

圖5、SI570晶振內部功能框圖

圖6、SI570晶振輸出特性

2.2原理圖設計

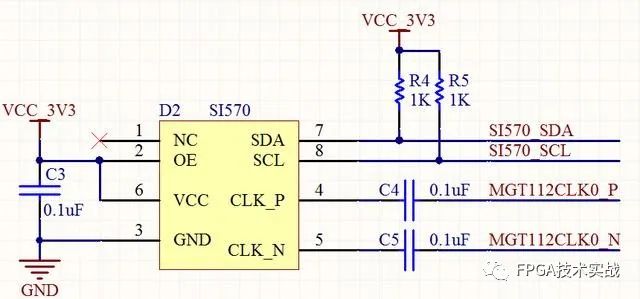

FPGA收發器參考時鐘晶振SI570原理圖設計如圖7所示。

圖7、SI570原理圖設計

3.SI570 FPGA軟件配置及結果測試

3.1 SI570晶振配置方法

從圖5中,可看到SI570控制接口采用I2C接口。我們在配置該晶振時要按照以下操作步驟進行:

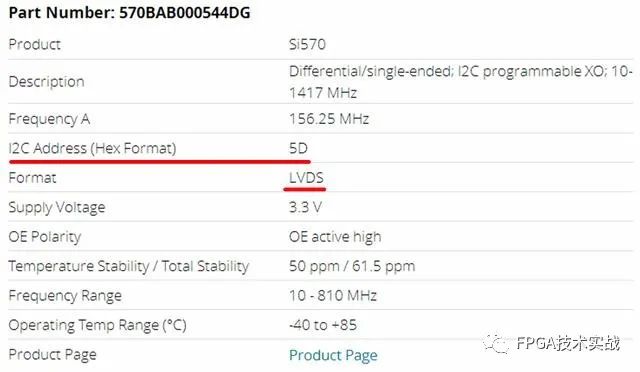

1.SI570根據家族類別,器件地址都不同,故首先需要去Silicon官網查找項目選型的晶振型號對應的器件地址。舉例SI570晶振型號:570BAB000544DG,該型號參數如圖8所示。在該圖中,我們可以得到可編程晶振的重要參數,如器件的I2C地址(0x5D),出廠默認輸出頻率(156.25MHz),頻率范圍等等。

圖8、SI570出廠參數信息

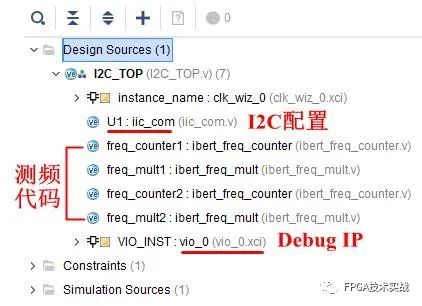

2.編寫FPGA軟件,讀出晶振SI570內部出廠默認寄存器配置字。FPGA實例工程如圖9所示。

圖9、SI570測試例程工程

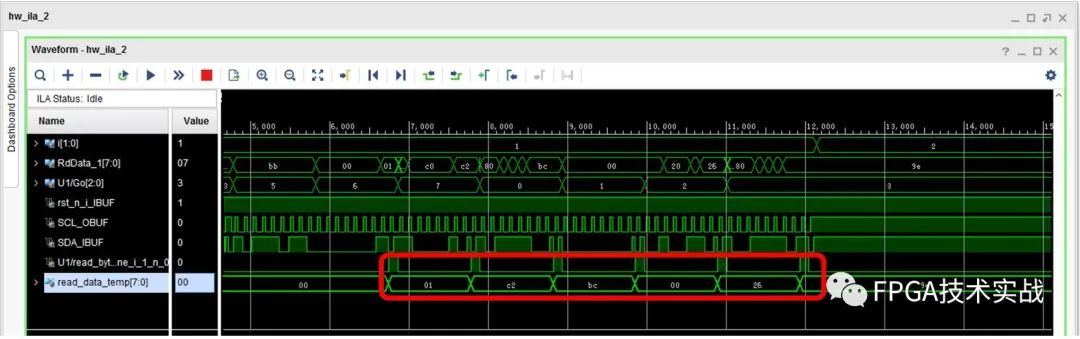

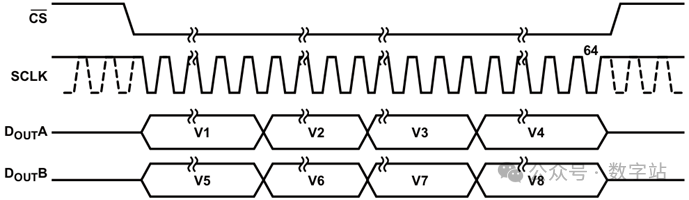

3.根據讀出的SI570內部寄存器默認配置值,FPGA I2C總線讀時序圖如圖10所示。

圖10、FPGA I2C總線讀時序圖

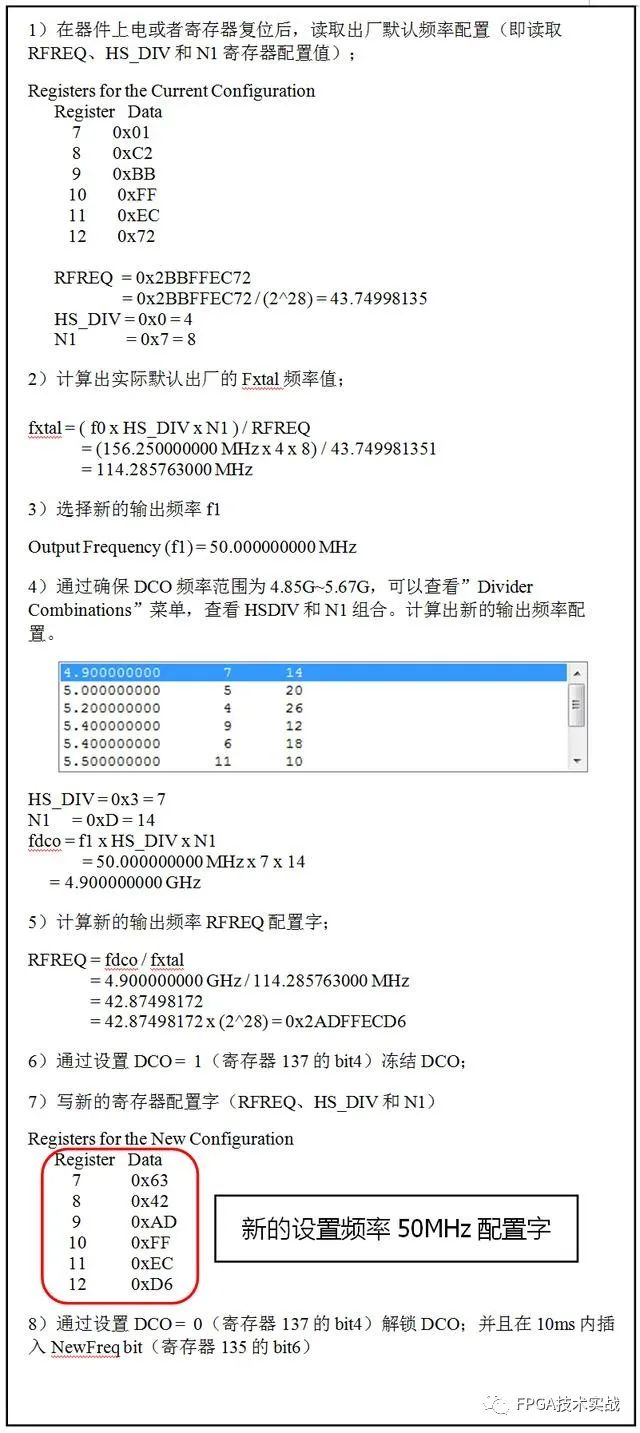

4.利用Silicon官方Programmable Oscillator Calculator軟件計算出要求出頻率所需的配置寄存器值。如圖11所示,本設計將SI570輸出頻率設置為50MHz。

圖11、計算SI570配置寄存器流程步驟

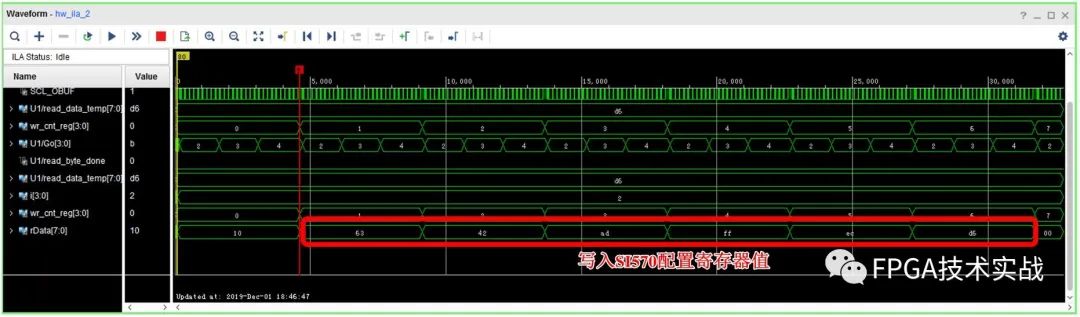

5.寫SI570寄存器配置值。FPGA I2C總線寫時序圖如圖12所示。

圖12、FPGA I2C總線寫時序圖

3.2 SI570配置結果測試

在圖5SI570測試例程工程中,我們還加入了SI570輸出頻率測試代碼,以通過FPGA在線邏輯分析儀測試SI570輸出頻率是否達到50MHz設計輸出要求。測試結果如圖13所示,可以看到晶振輸出結果符合設計要求。

圖13、SI570輸出頻率測試結果

編輯:lyn

-

收發器

+關注

關注

10文章

3454瀏覽量

106243 -

晶振

+關注

關注

34文章

2899瀏覽量

68312 -

數字電路

+關注

關注

193文章

1629瀏覽量

80822 -

Xilinx FPGA

+關注

關注

1文章

29瀏覽量

7211

原文標題:Xilinx FPGA收發器參考時鐘設計應用

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

無線收發器工作原理,無線收發器怎么使用

高速接口7系列收發器GTP介紹

【米爾-Xilinx XC7A100T FPGA開發板試用】+04.SFP之Aurora測試(zmj)

【米爾-Xilinx XC7A100T FPGA開發板試用】+03.SFP光口測試(zmj)

射頻收發器就是基帶嗎

光纖收發器pwr是什么意思

FPGA高速收發器的特點和應用

16位雙電源總線收發器此收發器具有可配置電壓轉換和3態輸出數據表

收發器的主要作用與種類詳解

如何配置使得ad9553輸出正確的GT收發器參考信號?

stm32f4xx的CAN對ID配置有要求嗎?CAN收發器是什么型號的?

AMD Xilinx 7系列FPGA的Multiboot多bit配置

Xilinx FPGA收發器參考時鐘設計要求與軟件配置及結果測試

Xilinx FPGA收發器參考時鐘設計要求與軟件配置及結果測試

評論