本原創(chuàng)教程由芯驛電子科技(上海)有限公司(ALINX)創(chuàng)作,版權(quán)歸本公司所有,如需轉(zhuǎn)載,需授權(quán)并注明出處(http://www.alinx.com)。

適用于板卡型號:

PGL22G

1. 簡介

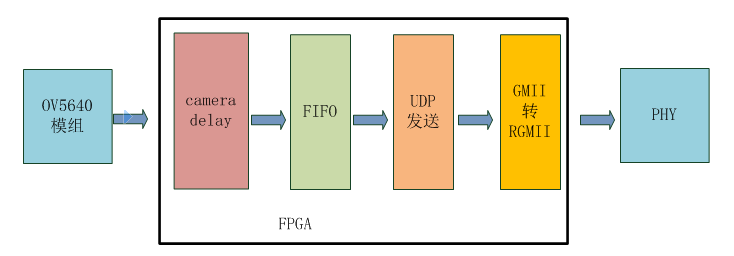

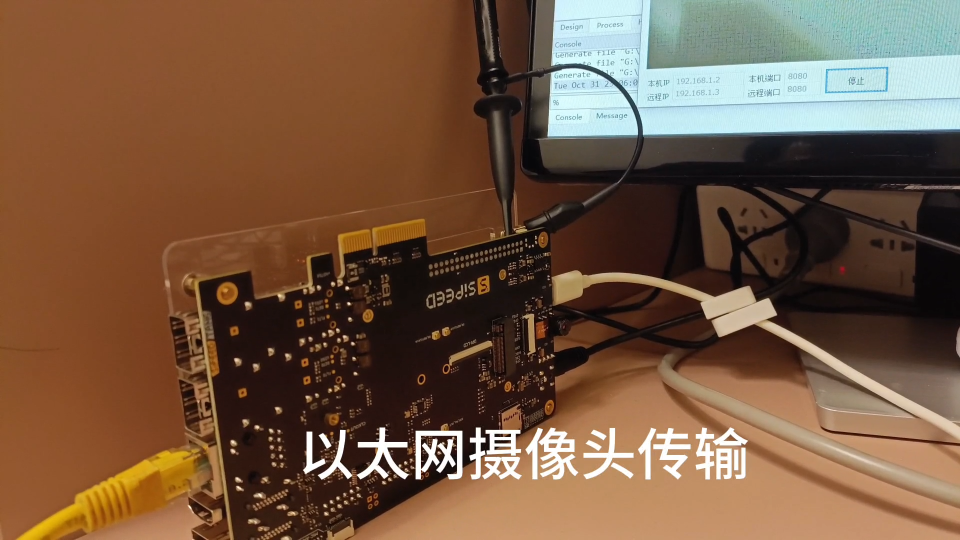

本實驗將實現(xiàn)視頻圖像的以太網(wǎng)傳輸,也相當(dāng)于用 FPGA 來實現(xiàn)網(wǎng)絡(luò)攝像頭的功能。這里采用黑金的 500 萬攝像頭 AN5642 模組,通過配置 OV5640 的寄存器實現(xiàn) JPEG 視頻壓縮的圖像輸出。以太網(wǎng)傳輸用 Ethernet UDP 通信協(xié)議,達到視頻圖像數(shù)據(jù)的快速傳輸。上位機通過接收網(wǎng)口的 UDP 數(shù)據(jù)包,提取 JPEG 的圖像數(shù)據(jù)顯示在電腦上。 在 FPGA 內(nèi)部,我們使用一個 FIFO 模塊用于存儲攝像頭 OV5640 采集的 JPG 圖像數(shù)據(jù),當(dāng) FIFO 數(shù)據(jù)的數(shù)量達到一個 UDP 數(shù)據(jù)包的長度時,觸發(fā)一次 UDP 的數(shù)據(jù)包發(fā)送。實現(xiàn)的邏輯框圖如下:

注意:在做此實驗之前,首先要學(xué)習(xí)之前的例程,OV5640的攝像頭顯示例程以及千兆以太網(wǎng)傳輸實驗。如果此實驗遇到問題,建議溫習(xí)前面的例程。

2. 程序設(shè)計

2.1 攝像頭參數(shù)設(shè)置

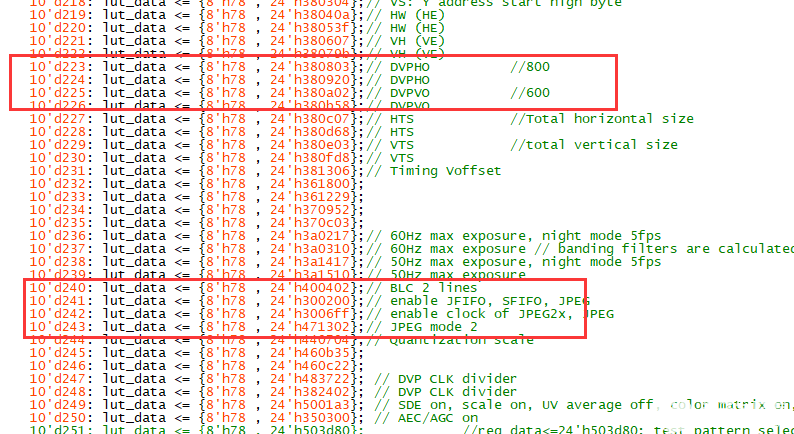

我們對ov5640寄存器配置做了修改,在寄存器表里,將分辨率改成了800*600。并且選擇了JPEG模式。

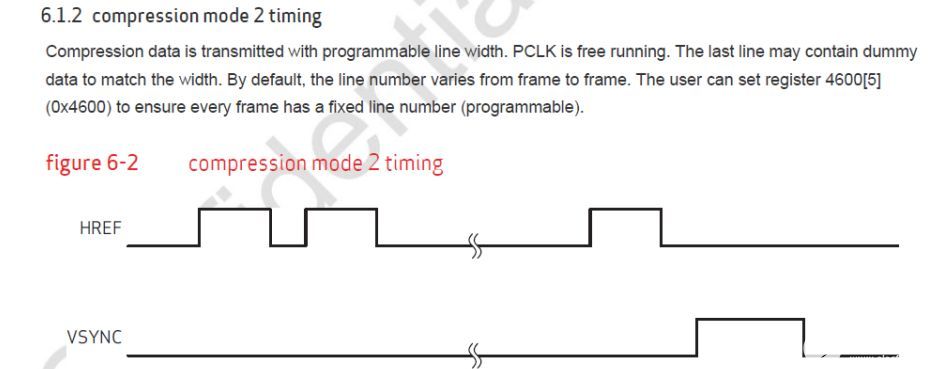

這里需要注意,JPEG 格式輸出的視頻圖像的每一幀的數(shù)據(jù)大小是不一樣的,JPEG 輸出的

數(shù)據(jù)模式有 6 種,我們程序中設(shè)置為 JPEG 模式 2,即每行的長度是固定的,每幀會有不同的

行數(shù),最后一行的數(shù)據(jù)沒有達到固定的長度的話,會補充 dummy 數(shù)據(jù)。具體大家看一下

OV5640 的 datasheet。

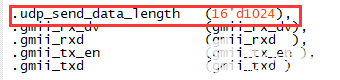

每行的長度由以下的寄存器配置,這里我們程序中并沒有設(shè)置,默認參數(shù)為 0x400,也就

是每行的數(shù)據(jù)長度為 1024.

2.2 以太網(wǎng)設(shè)置

在例化mac_test.v時,將UDP發(fā)送數(shù)據(jù)長度設(shè)置為1024字節(jié)。并對以太網(wǎng)做了上電復(fù)位處理,利用power_on_rst.v上電延遲100ms復(fù)位以太網(wǎng)模塊。在udp_tx.v文件中,去掉了UDP數(shù)據(jù)的校驗和計算,節(jié)省時間。在mac_test.v的狀態(tài)機中,加入了CHECK_FIFO狀態(tài),由于以太網(wǎng)首部發(fā)送也要一定時間,因此提前判斷fifo中的可讀數(shù)據(jù)數(shù)量是否大于1000,啟動UDP數(shù)據(jù)發(fā)送。

3. 下載和實驗

注意:在做實驗之前一定要確保OV5640攝像頭顯示沒有問題,可結(jié)合OV5640攝像頭顯示例程確認。

3.1 開發(fā)板連接

1)將AN5642攝像頭模組插入開發(fā)板,模塊依次接入AX7035/AX050的擴展口J9、J8。保證1腳對齊,1腳在焊盤形狀和其他引腳是有明顯區(qū)別的,是方形的;

2)使用網(wǎng)線連接PC和開發(fā)板的以太網(wǎng)口,這里的PC網(wǎng)卡需要千兆網(wǎng)卡和千兆網(wǎng)線,切換攝像頭視頻時需按KEY2鍵。

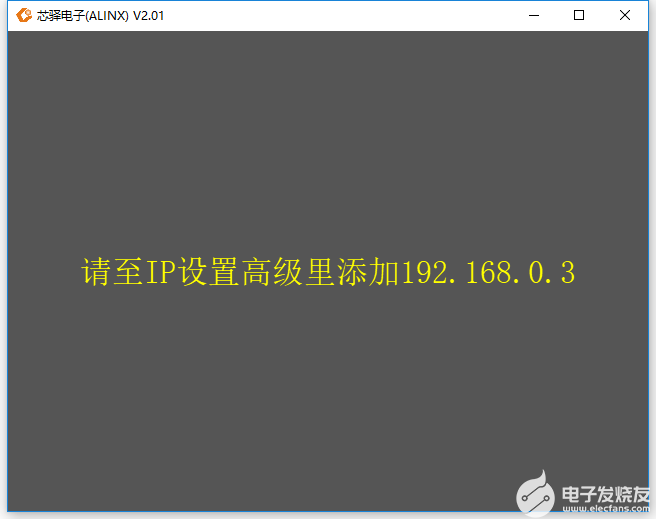

3.2 PC端IP設(shè)置

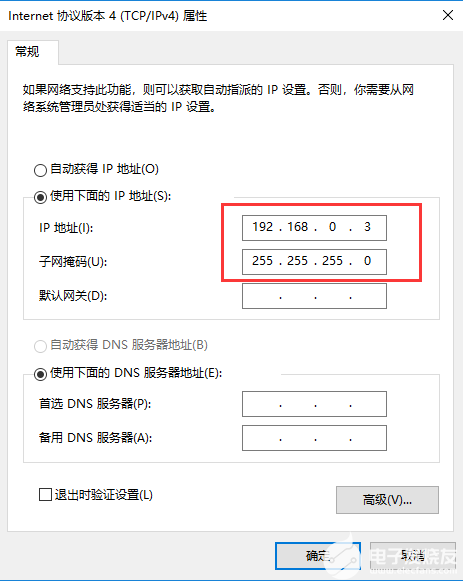

設(shè)置PC端的IP地址為192.168.0.3,如下圖:

3.3 程序下載

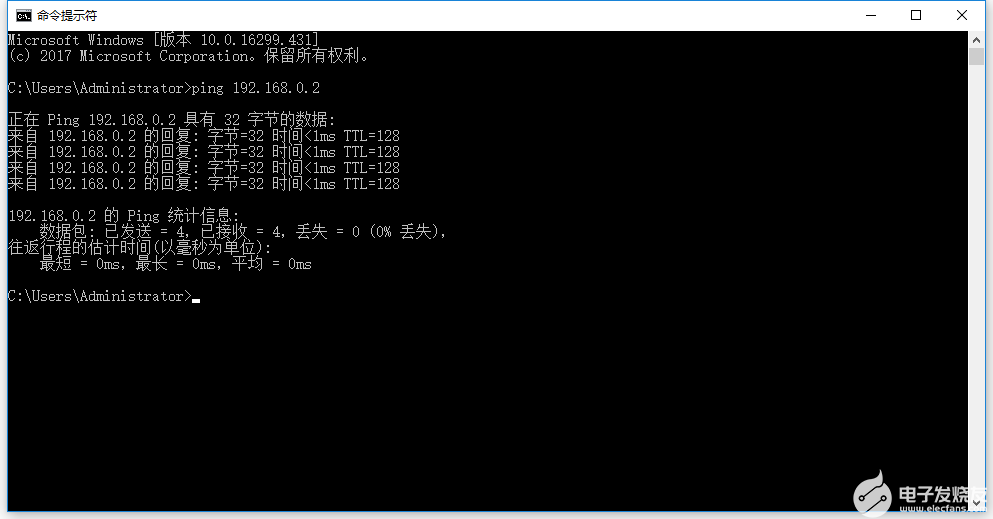

下載FPGA程序,在打開上位機軟件之前,首先檢查網(wǎng)絡(luò)是否連通,可在CMD窗口

ping 192.168.0.2查看連通情況。

3.4 上位機軟件

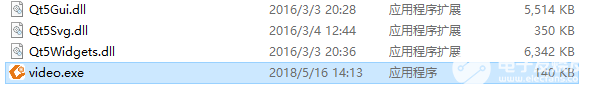

打開“CD\07_軟件工具及驅(qū)動\以太網(wǎng)視頻傳輸軟件”文件夾中的video.exe

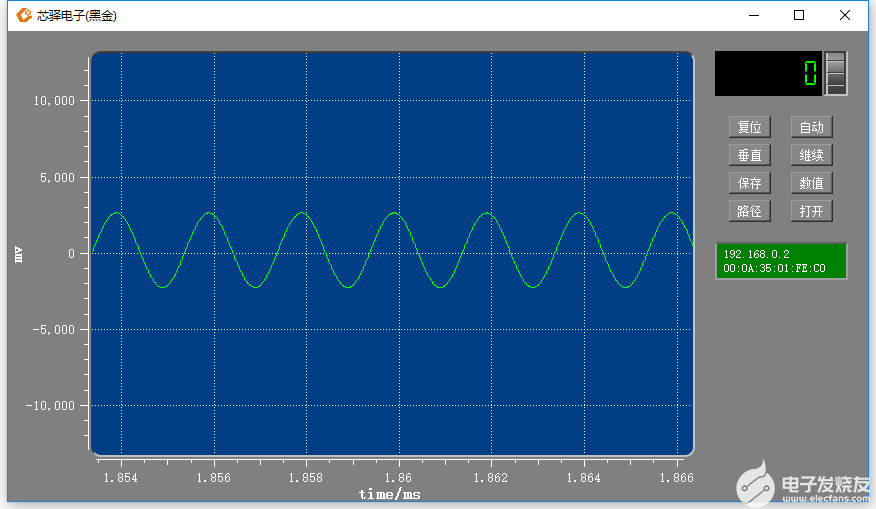

之后軟件就可以顯示圖像,效果如下:

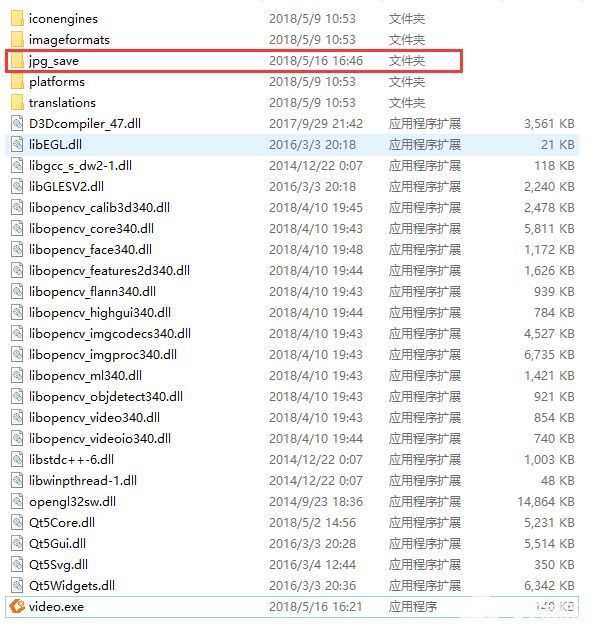

3.5 視頻截圖

在軟件顯示窗口,點擊鼠標(biāo)左鍵按住不放,可以保存圖片及視頻,松開即可停止保存。出現(xiàn)jpg_save文件,圖片和視頻保存在里面。

打開文件夾,可以看到保存的圖片和視頻,注意要控制保存的時間,否則會很占用磁盤空間。每一張圖片表示一幀圖像。

4. 常見問題

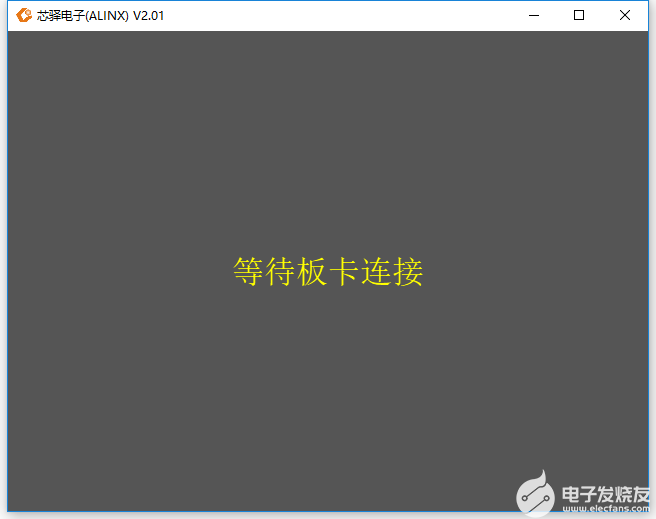

4.1 等待板卡連接

在打開軟件后,如果出現(xiàn)以下情況,可能原因是攝像頭或網(wǎng)線沒有插好,請檢查攝像頭及網(wǎng)線連接情況。之后重新打開軟件。

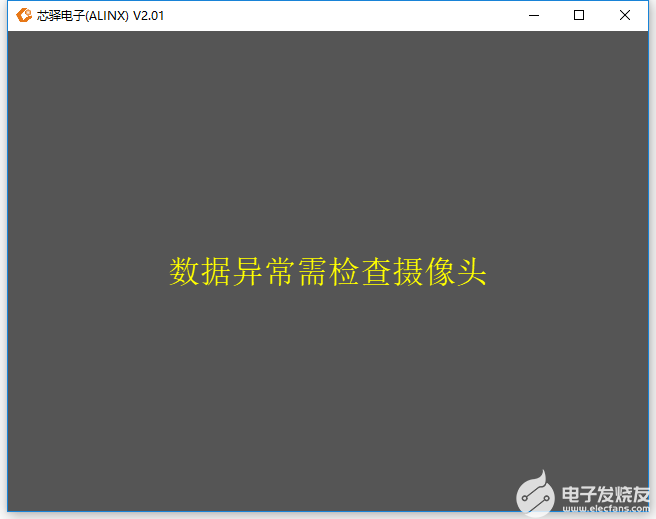

4.2 數(shù)據(jù)異常

如果出現(xiàn)以下情況,可能原因是攝像頭配置不正常,有數(shù)據(jù)發(fā)送,但上位機無法解析,建議先用攝像頭顯示例程檢查攝像頭是否能正常使用或者重新插好攝像頭。之后重新打開軟件。

4.3 IP地址未配置

如果出現(xiàn)以下情況,表示沒有設(shè)置IP地址,請確認設(shè)置好IP后重新打開軟件。

5. 總結(jié)

到此為止,以太網(wǎng)傳輸視頻的實驗就做完了,程序比較簡單,僅在原有的實驗基礎(chǔ)上做了擴展,理解起來相對容易些。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606065 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5460瀏覽量

172752 -

攝像頭

+關(guān)注

關(guān)注

60文章

4865瀏覽量

96322 -

fifo

+關(guān)注

關(guān)注

3文章

389瀏覽量

43865 -

紫光同創(chuàng)

+關(guān)注

關(guān)注

5文章

88瀏覽量

27563

發(fā)布評論請先 登錄

相關(guān)推薦

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第二十三章】千兆以太網(wǎng)傳輸實驗

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第二十四章】AD9238以太網(wǎng)傳輸

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第二十五章】AD7606以太網(wǎng)傳輸

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第二十六章】AD9280以太網(wǎng)傳輸

國產(chǎn)FPGA介紹-紫光同創(chuàng)

【正點原子FPGA連載】第二十七章gpio子系統(tǒng)下的LED驅(qū)動實驗-領(lǐng)航者ZYNQ之linux開發(fā)指南

基于FPGA的以太網(wǎng)視頻廣播接收系統(tǒng)的設(shè)計

第二十七講 同步時序邏輯電路的設(shè)計

模擬電路網(wǎng)絡(luò)課件 第二十七節(jié):集成電路運算放大器

【正點原子FPGA連載】第二十五章HDMI方塊移動實驗 -摘自【正點原子】新起點之FPGA開發(fā)指南_V2.1

【正點原子FPGA連載】第二十七章DS18B20數(shù)字溫度傳感器實驗 -摘自【正點原子】新起點之FPGA開發(fā)指南_V2.1

【正點原子FPGA連載】第三十七章雙路高速AD實驗 -摘自【正點原子】新起點之FPGA開發(fā)指南_V2.1

晶能光電亮相第二十七屆廣州國際照明展覽會

姍姍來遲!第二十七屆電壓敏學(xué)術(shù)年會在成都成功召開

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第二十七章】千兆以太網(wǎng)視頻傳輸實驗

【紫光同創(chuàng)國產(chǎn)FPGA教程】【第二十七章】千兆以太網(wǎng)視頻傳輸實驗

評論