同步控制信號

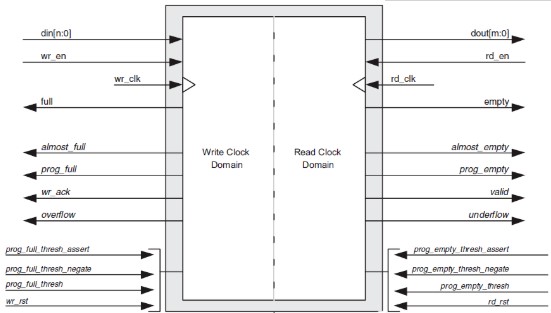

對于讀/寫時鐘相互獨立的FIFO(讀/寫時鐘獨立意味著這兩個時鐘是異步的,例如來自于不同的MMCM),要確保相應的控制信號只在與之對應的時鐘域內被使用。如下圖所示,除了rst對整個FIFO進行異步復位外,其余信號都與各自的時鐘同步。例如:寫使能wr_en、寫數據din都與寫時鐘wr_clk同步;讀使能rd_en、讀數據dout都與讀時鐘rd_clk同步。和“滿”相關的狀態信號如full/almost_full等都與wr_clk同步;和“空”相關的狀態信號如empty/almost_empty等都與rd_clk同步。

復位信號 對于讀/寫時鐘獨立的FIFO,FIFO Generator提供了復位信號,用于對所有的狀態輸出信號進行復位,如下圖所示。這里復位信號是可選的。如果下圖選項1不勾選,那么選項2和選項3則不可見,此時FIFO沒有復位信號。如果勾選1,此時選項2和選項3可見,且默認均被勾選,這意味著rst盡管是異步的,但在使用時會被wr_clk和rd_clk先同步到各自的時鐘域。如果勾選1,但不勾選2,此時讀/寫時鐘域會分別有各自的復位信號wr_rst和rd_rst。當wr_rst有效時(高有效),寫時鐘域處于復位狀態;當rd_rst有效時,讀時鐘域處于復位狀態。由此可見,對于讀/寫時鐘獨立的FIFO,異步復位rst和同步wr_rst/rd_rst是可選的。這意味著FIFO可以沒有復位信號,也可以只用一個異步復位信號rst,或者用同步復位wr_rst/rd_rst。

原文標題:你的FIFO為什么不能正常工作

文章出處:【微信公眾號:Lauren的FPGA】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

fifo

+關注

關注

3文章

389瀏覽量

43858 -

同步控制

+關注

關注

0文章

35瀏覽量

12459

原文標題:你的FIFO為什么不能正常工作

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

為什么有時候FIF不能正常工作?

為什么有時候FIF不能正常工作?

評論