擴(kuò)頻技術(shù)是一種信息傳輸處理技術(shù)。通過擴(kuò)頻使信號功率相當(dāng)均勻的分布在很寬的頻率范圍內(nèi),具有類似于白噪聲的統(tǒng)計特性,使得該系統(tǒng)有很強(qiáng)的抗干擾性能、高保密性、低截獲概率性及良好的碼分多址通信性能。擴(kuò)頻系統(tǒng)的這些優(yōu)良性能,使得它在很多對信道帶寬利用率要求不高的場合得到廣泛的應(yīng)用,本文就是一個關(guān)于深井通信的實現(xiàn)系統(tǒng)。

設(shè)計背景

根據(jù)擴(kuò)頻碼控制的調(diào)制參數(shù)不同,擴(kuò)頻方式可分為:直接序列擴(kuò)頻(DS-SS),跳頻擴(kuò)頻(FH-SS)和跳時擴(kuò)頻(TH-SS)。本文介紹的系統(tǒng)采用的就是直接擴(kuò)頻,直接序列擴(kuò)頻通信是通過在發(fā)送端將數(shù)據(jù)信號和更高數(shù)據(jù)速率的位序列或填充碼組合而實現(xiàn)的。填充碼是冗余位組合,其可根據(jù)擴(kuò)展率將用戶數(shù)據(jù)分段。當(dāng)該位信號發(fā)送時,可以增加信號抗干擾的能力。如果在這種組合中有一個或多個位在傳輸過程中發(fā)生錯誤,那么由于發(fā)送的冗余性,原始數(shù)據(jù)也可以被恢復(fù)出來。圖1為直擴(kuò)系統(tǒng)的組成原理框圖。由信源輸出的信號a(t)是碼元持續(xù)時間為Ta的信息流,偽隨機(jī)碼產(chǎn)生器產(chǎn)生的偽隨機(jī)碼為c(t),每一偽隨機(jī)碼寬度或者切普(Chip)寬度為Tc。將信碼a(t)與偽隨機(jī)碼c(t) 進(jìn)行模二加,產(chǎn)生一速率與偽隨機(jī)碼速率相同的擴(kuò)頻序列,然后再用擴(kuò)頻序列去調(diào)制載波,這樣就得到已擴(kuò)頻調(diào)制的射頻信號。

在接收端,接收到的擴(kuò)頻信號經(jīng)高放和混頻后,用于發(fā)端同步的偽隨機(jī)序列對中頻的擴(kuò)頻調(diào)制信號進(jìn)行相關(guān)解擴(kuò),將信號的頻帶恢復(fù)為信息序列a(t)的頻帶,為中頻調(diào)制信號。然后再進(jìn)行解調(diào),恢復(fù)出所傳輸?shù)男畔(t),從而完成信息的傳輸。對于干擾信號和噪聲而言,由于與偽隨機(jī)序列不相關(guān),在相關(guān)解擴(kuò)器的作用下,相當(dāng)于進(jìn)行了一次擴(kuò)頻。干擾信號和噪聲頻譜被擴(kuò)展后,其譜密度減低,這樣就大大降低了進(jìn)入信號通頻帶內(nèi)的干擾功率,使解調(diào)器的輸入信噪比和輸出信噪比提高,從而提高了系統(tǒng)的抗干擾能力。

本文介紹的是一個井下通信系統(tǒng)。煤礦井下巷道和采掘工作面空間狹窄,大都呈隧道狀,采煤工作面長可達(dá)幾百米,而礦井巷道長可達(dá)數(shù)千米甚至十幾千米,寬、高僅為幾米。作業(yè)點分散,人員流動性大,環(huán)境中存在著大量的有爆炸危險的一氧化碳,瓦斯及煤塵等空氣混合體,事故隱患極大。因此,建立完善的煤礦井下無線和移動通信系統(tǒng)對于提高礦井現(xiàn)代化生產(chǎn)、安全和管理水平有著非常重要的意義。

目前我國煤礦井下移動通信的主要方式有動力線載波通信、感應(yīng)通信、漏泄通信以及中低頻無線電。動力線載波通信在傳輸距離,通話清晰度和抗干擾能力上都無法適應(yīng)現(xiàn)代化礦井的需要。感應(yīng)通信目前在我國部分煤礦得到使用,但通話質(zhì)量和通信距離都不夠理想。漏泄通信不能覆蓋到井下的每個地方。

為了減少地質(zhì)條件對無線通信信號的衰減,通常采用低頻通信直至超低頻通信。中低頻通信穿透能力強(qiáng),如用超低頻信號可穿透巖層幾百米,可在大面積范圍內(nèi)對深處的坑道實施指揮與控制,加上它對電離層擾動不敏感,即使發(fā)生大爆炸也不會嚴(yán)重干擾它,這使它在極端惡劣環(huán)境條件下成為提供大面積應(yīng)急指揮控制通信的一種重要手段,在緊急情況發(fā)生時,能夠迅速有效地與井下的工作人員進(jìn)行通訊。所以本系統(tǒng)就是采用這種通信方式,中頻信號僅22Hz。

系統(tǒng)原理框圖

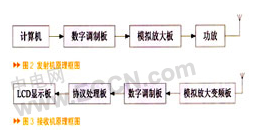

圖2和圖3分別為發(fā)射機(jī)原理框圖和接收機(jī)原理框圖,信號首先從計算機(jī)發(fā)出,通過數(shù)字調(diào)制板擴(kuò)頻編碼后轉(zhuǎn)換為模擬信號,模擬信號放大后送到天線發(fā)射出去。接收機(jī)是發(fā)射機(jī)的逆過程,模擬信號從天線接收下來后先進(jìn)行放大,然后送入數(shù)字解調(diào)板轉(zhuǎn)換為數(shù)字信號后解擴(kuò),解擴(kuò)后的信號送入?yún)f(xié)議處理板,協(xié)議處理板用于實現(xiàn)選呼,群呼及廣播協(xié)議的實現(xiàn),圖中LCD顯示板用于信息的顯示。數(shù)字調(diào)制板和數(shù)字解調(diào)板是整個系統(tǒng)的核心,分別進(jìn)行擴(kuò)頻調(diào)制和解調(diào),解調(diào)是調(diào)制的逆過程,二者結(jié)構(gòu)相似,硬件電路也大同小異,只是輸入和輸出互換,所以本文主要介紹數(shù)字調(diào)制板。

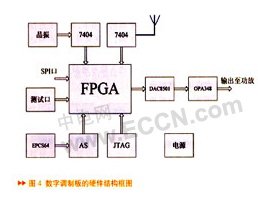

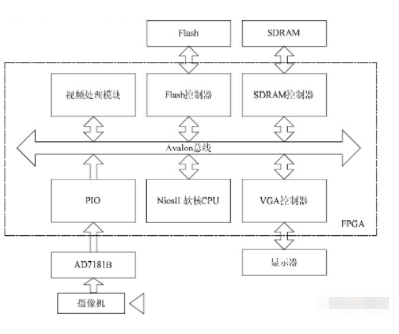

數(shù)字調(diào)制板的硬件結(jié)構(gòu)框圖 數(shù)字調(diào)制板的硬件結(jié)構(gòu)框圖如圖4所示。

數(shù)字調(diào)制板從計算機(jī)接收數(shù)據(jù)并接收來自天線的狀態(tài)信息,主要完成對信號的擴(kuò)頻編碼調(diào)制,調(diào)制后的信號經(jīng)數(shù)模轉(zhuǎn)換和放大濾波后送入下一級功放電路。計算機(jī)和調(diào)制器間采用SPI口進(jìn)行數(shù)據(jù)傳輸,擴(kuò)頻編碼調(diào)制采用turbo碼,來自天線的狀態(tài)信息用于指示天線的短路或斷路等通信狀態(tài)。 該模塊的核心部分是FPGA,對數(shù)據(jù)的處理都是在此芯片內(nèi)完成。數(shù)據(jù)從計算機(jī)的SPI口輸入,處理后經(jīng)DAC8501變?yōu)槟M信號,再經(jīng)OPA348放大后輸出。FPGA配置了JTAG下載口,用于調(diào)試程序時使用。AS下載口是在程序調(diào)試完成后,通過該口將程序?qū)懭隖PGA的專用配置芯片EPCS64中,EPCS64中的內(nèi)容掉電后不會丟失,以后上電后程序就會自動下載進(jìn)FPGA中。晶振提供系統(tǒng)時鐘,為了增強(qiáng)驅(qū)動能力,所以加了片7404。

主要模塊的電路設(shè)計

系統(tǒng)的核心芯片F(xiàn)PGA依據(jù)編寫程序所需資源適當(dāng)選取,本系統(tǒng)選用EP2C35,EP2C35是ALTERA公司cyclone‖系列FPGA。CycloneII FPGA采用TSMC 90nm Low-K工藝,1.2V內(nèi)核電壓,比cyclone系列成本降低30%,邏輯容量多三倍,成本大約是相競爭的低成本FPGA的一半,而速度快50%以上。EP2C35的邏輯單元為33216個,M4K RAM塊105個,RAM480K,嵌入式18×18乘法器35個,鎖相環(huán)4個,可以滿足設(shè)計需要。

SPI是串行外圍設(shè)備接口,是一種高速的、全雙工、同步串行外設(shè)接口。它可以使MCU與各種外圍設(shè)備以串行方式進(jìn)行通信以交換信息。該接口一般使用4條線:串行時鐘線SCK,主機(jī)輸入/從機(jī)輸出數(shù)據(jù)線MISO,主機(jī)輸出/從機(jī)輸入數(shù)據(jù)線MOSI和低電平有效的從機(jī)選擇線SS。由于SPI系統(tǒng)總線接口簡單,可以節(jié)省很多常規(guī)電路中的接口器件和I/O口線,提高設(shè)計的可靠性。所以當(dāng)傳輸速度要求不是太高時,使用SPI總線可以簡化電路設(shè)計,提高系統(tǒng)的性能。圖5 給出了SPI接口電路原理圖。

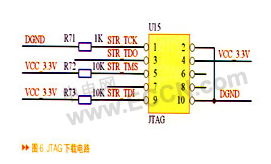

JTAG是一種國際標(biāo)準(zhǔn)測試協(xié)議(IEEE 1149.1兼容),主要用于芯片內(nèi)部測試。現(xiàn)在多數(shù)的高級器件如DSP、FPGA器件等都支持JTAG協(xié)議。標(biāo)準(zhǔn)的JTAG接口是4線:TMS、TCK、TDI、TDO,分別為模式選擇、時鐘、數(shù)據(jù)輸入和數(shù)據(jù)輸出線。JTAG編程方式是在線編程,方便調(diào)試,從而大大加快工程進(jìn)度。JTAG下載電路如圖6所示。

AS是主動串行編程模式,在AS模式下,POF數(shù)據(jù)流直接下載到基于Flash的串行設(shè)備中。因為FPGA是基于SRAM架構(gòu)的,掉電以后,所有存儲在SRAM中的配置數(shù)據(jù)都會丟失,所以每次上電必須重新加載,很不方便。EPCS64本質(zhì)上是一塊專用flash,用于保存FPGA的配置信息,它在掉電后,里面內(nèi)容不會丟失,在FPGA上電的時候,自動從配置芯片 里面讀出配置內(nèi)容,這樣上電后即可使用。所以當(dāng)設(shè)計完成后通常將程序通過AS口固化到片外配置芯片,以后每次上電后程序就會自動下載進(jìn)FPGA中,圖7給出了連接電路。

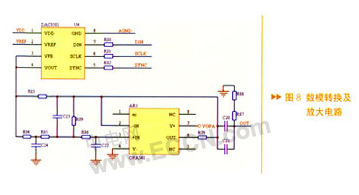

數(shù)模轉(zhuǎn)換器和運算放大器分別選 用TI公司的DAC8501和OPA348。DAC8501是16比特串行輸入數(shù)模轉(zhuǎn)換器,帶寬350KHZ,工作電壓2.7V~5.5V,只有8 個管腳,體積很小,非常適合本次 設(shè)計要求。OPA348是一種具有極低功耗的放大器,供電電流只有45 A,帶寬1MHZ,工作電壓2.1V~5.5V,SOT23-8封裝,外圍電路簡單,調(diào)試方便。電路原理圖如圖8所示。

總結(jié)

本文介紹了一個采用擴(kuò)頻編碼技術(shù)的井下通信系統(tǒng),并對其調(diào)制器部分的硬件電路做了簡單介紹。其實這可以看作是一個簡單的通信系統(tǒng)模型,發(fā)送端進(jìn)行編碼調(diào)制,接收端進(jìn)行譯碼,利用編碼來擴(kuò)展待傳輸?shù)男盘枎挘該Q取信噪比上的好處,從而可以在較低的信噪比下正確地傳送信息。該系統(tǒng)模型完全可以移植到其它設(shè)計上去,基本結(jié)構(gòu)不變,只是數(shù)模轉(zhuǎn)換器和模數(shù)轉(zhuǎn)換器及放大器要依據(jù)新系統(tǒng)的帶寬等要求來選擇,F(xiàn)PGA也應(yīng)依據(jù)新系統(tǒng)所需資源來選擇合適的型號,編碼也可以選用BCH碼或LDPC碼等其它碼,還可以視系統(tǒng)需要而加入RS232接口或USB接口等其它接口電路。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605998 -

移動通信

+關(guān)注

關(guān)注

10文章

2617瀏覽量

70073 -

通信系統(tǒng)

+關(guān)注

關(guān)注

6文章

1204瀏覽量

53459

發(fā)布評論請先 登錄

相關(guān)推薦

基于EP2c35 FPGA和NiosII 軟核實現(xiàn)視頻監(jiān)控系統(tǒng)的設(shè)計

基于FPGA的擴(kuò)頻系統(tǒng)設(shè)計

擴(kuò)頻通信技術(shù)教程

基于FPGA實現(xiàn)CDMA擴(kuò)頻通信中的同步系統(tǒng)畢業(yè)設(shè)計

基于FPGA的擴(kuò)頻系統(tǒng)設(shè)計(附代碼)

基FPGA Cyclone II_EP2C5 EP2C8的頻

FPGA在多進(jìn)制正交擴(kuò)頻通信系統(tǒng)中的應(yīng)用

基于FPGA的CMI編碼系統(tǒng)設(shè)計

基于FPGA的高爐TRT頂壓控制系統(tǒng)的研究

直接擴(kuò)頻通信同步系統(tǒng)的xilinx FPGA設(shè)計原理分析

基于FPGA解決方案的SOPC技術(shù)實現(xiàn)二維條碼識別系統(tǒng)的設(shè)計

基于FPGA的直接序列擴(kuò)頻和差錯控制碼編碼系統(tǒng)的實現(xiàn)

基于EP2C35 FPGA和擴(kuò)頻編碼技術(shù)實現(xiàn)井下通信系統(tǒng)的應(yīng)用方案

基于EP2C35 FPGA和擴(kuò)頻編碼技術(shù)實現(xiàn)井下通信系統(tǒng)的應(yīng)用方案

評論