本文在分析軟件無線電的寬帶數字中頻和數字下變頻的基本模型基礎上,結合ADI公司推出的接收信號處理器芯片AD6624的工作原理,提出CDMA基站反向鏈路中基帶信號處理的設計方案,并詳細討論了基帶濾波器的設計方法,同時給出了仿真結果。

軟件無線電( Software DefineDRadio,SDR)的宗旨就是盡可能地簡化射頻模擬前端,使A/D轉換盡可能靠近天線去完成模擬信號的數字化,而且數字化后的信號要盡可能多地用軟件來處理,實現各種功能和指標。模擬信號進行數字化后的處理任務全由DSP軟件來承擔。

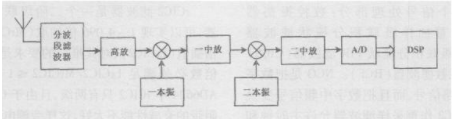

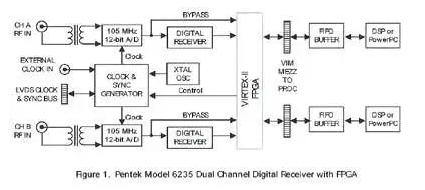

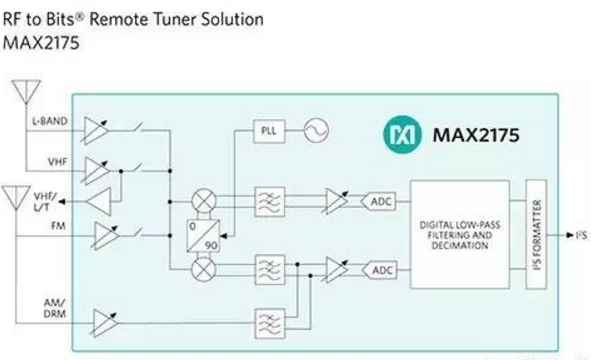

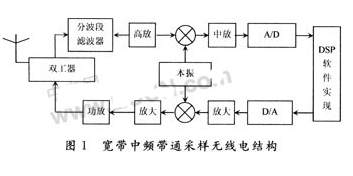

在目前的軟件無線電研究中,由于受硬件發展水平的限制,接收機的結構大多數都是將射頻信號經模擬下變頻至中頻( Intermediate Frequency,IF),在中頻通過高速、高精度A/D轉換器對寬帶中頻信號進行欠采樣,即對射頻模擬信號的采樣數字化采用寬帶中頻帶通信號軟件無線電結構,如圖1所示。

圖1寬帶中頻帶通信號軟件無線電結構

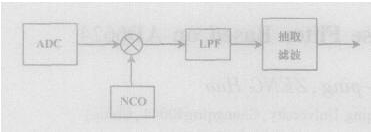

但是中頻采樣后的數據量非常大,如果直接用軟件進行處理,將占用大量的DSP計算資源。尤其對CDMA系統來說,其寬帶性更增加了DSP的處理難度。為了減輕DSP的處理壓力,現在通常的做法是把A/D轉換器傳來的數字信號,經過專用數字信號處理器件如數字下變頻器(Digtal DownConverter,DDC)處理,降低數據流速率,并把信號變至基帶后,再把數據送給通用DSP進行處理。數字下變頻的組成主要包括一個數字控制振蕩器(Numerically ControlleD Oscillator,NCO)、一個數字混頻器和低通濾波器,如圖2所示。NCO產生的本振信號與ADC后的輸入信號進行混頻。數字混頻器就是乘法器。信號經混頻后輸出到低通濾波器以濾除倍頻分量和帶外信號,然后進行抽取處理。

圖2數字下變頻器的組成

系統模型設計

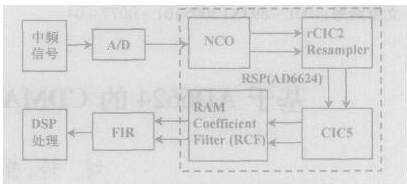

基于軟件無線電的CDMA基站接收單元對有用信號進行下變頻處理,將信號移至基帶,并把高速基帶信號做速率轉換處理,即對信號進行抽取和插值濾波,最后進行基帶濾波處理。在我們的設計中,RSP(Receive Signal Processor)芯片采用AD公司AD6624。它的主要特征是:80MSPS寬帶輸入,兩路高速數據輸入端口和4個獨立的數字下變頻通道,可編程抽取FIR 濾波器。將它運用到基站軟件無線電接收機中可以多信道同時進行數字下變頻。AD6624包含4個信號處理部分:數控振蕩器(NCO)、二階的重抽樣級聯積分梳狀濾波器( rCIC2)、五階的級聯積分梳狀FIR濾波器(CIC5)以及一個RAM系數濾波器(RCF)。NCO是把數字信號分成I、Q兩路信號,而且把數字中頻信號變換到數字基帶。rCIC2作重采樣濾波器允許主時鐘和輸出速率有非整數倍關系。CIC5是一個比rCIC2濾波特性更陡峭的抽取濾波器。RAM是乘積求和可編程系數抽取濾波器。基于AD6624的反向鏈路中頻到基帶的信號處理過程如圖3所示。

圖3CDMA反向基帶濾波處理框圖

反向中頻信號經A/D采用后輸入RSP進行數字下變頻和濾波處理,首先對信號進行數字正交變換,把輸入的數字中頻信號變成數字基帶信號,變換后的I/Q數據送入rCIC2進行重采樣(抽取和插值濾波處理),然后送入CIC5進行抽取濾波,經過兩次抽取后的低速數據送入RCF進行基帶濾波處理,同時也可以進行抽取處理。考慮到RCF的基帶濾波處理能力不夠,所以在邏輯中又增加了一級FIR濾波器進行基帶濾波處理。

參照前向基帶濾波器和系統對抗單音阻塞性能的要求,初步提出基帶濾波器的指標如下:通帶為590kHz,帶內波動為±1. 5dB,阻帶- 40dB@740kHz、- 80dB@900kHz。

濾波器設計與仿真

抽取系數的確定

根據目前的設計,A/D采樣率為48 Chip,基帶信號的采樣率為2Chip,所以在RSP內可以實現24倍抽取,RCF內濾波器的階數最高為24階。為了避免信號混疊,保持最佳的濾波性能,并降低對邏輯( FPGA)內的FIR 濾波器性能的要求,需要在rCIC2、CIC5和RCF之間合理的分配抽取率。

(1)rCIC2抽取率的確定

rCIC2濾波器是一個二階級聯積分梳狀濾波器,可以實現1~4096倍抽取(MrCIC2)和1~512倍插值(L rCIC2),對其唯一的要求是抽取和插值的倍數必須滿足LrCIC2/MrCIC2≤1的關系。由于AD6624中rCIC2只有兩級,且由于CIC的過渡帶和阻帶的衰減性能不太好,這樣旁瓣電平比較高,當Mm1時,旁瓣電平最多只比主瓣電平低27dB,由于阻帶衰減很差,無法滿足抗混疊要求,一般不做高階抽取。在本設計中,考慮到采樣率(48 ChiP)遠大于信號帶寬(0. 59450MHz),則只要保證抽取后無混疊信號帶寬大于信號的帶寬,就不會引起混疊,于是取MrCIC2= 2,L rCIC2= 1,則抽取后的采樣率變為24Chip,無混疊信號帶寬為12ChiP( 14. 7456MHz),大于信號帶寬。

(2)CIC5抽取率的確定

CIC5的可編程抽取率(MCIC5)大小為2~32。對CIC5抽取率的選取主要從以下3個方面考慮。

1)處理增益

由Q級CIC濾波器頻率響應的表達式HQ ( ejω)=DQ.SaQ (ωD/2).Sa- Q (ω/2)可知,CIC抽取濾波器有一個處理增益DQ。隨著濾波器級數Q和抽取因子D的增大,處理增益也越大,但是因為CIC5的運算精度有限,所以增益不能過大,否則容易引起溢出或降低運算精度。

2)抗混疊性能

為了降低混疊影響,獲得足夠大的阻帶衰減,在輸入采樣速率一定的前提下,盡可能的采用小的抽取因子。

3)帶內平坦度考慮

隨著抽取率的增高,通帶內的信號衰減也增大,不過帶內衰減可以在后級濾波器中進行補償。鑒于以上幾個因素的綜合考慮,選取MCIC5= 6。

(3)RCF抽取率的確定

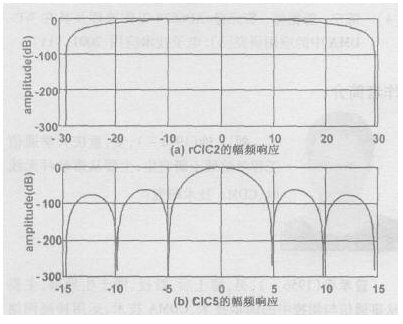

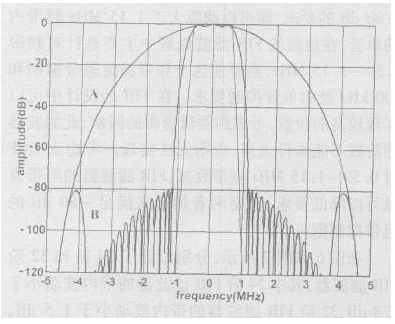

圖4rCIC2和CIC5的幅頻響應

因為整個基帶信號處理要實現24階抽取,已確定MrCIC2= 2、MCIC5= 6,所以MRCF= 2。在RCF的處理中,經過rCIC2和CIC5的高倍抽取,此時數據的采樣率已經變得很低,所以對RCF的抗混疊性能要求較高,同時還要考慮對單音信號的抑制。經過上面的分析,確定如下系數:MrCIC2= 2、LrCIC2= 1、MCIC5= 6、MRCF= 2。RCIC2和CIC5的幅頻響應見圖4。由圖可見,帶內(0~0. 59MHz)衰減小于1dB,CIC5的阻帶衰減約為62dB。通常CIC濾波器會引起信號混疊,但如果抽取的信號帶寬很窄,則在其信號帶寬內這種混疊可以忽略不計,因為CIC濾波器可以對混疊部分提供有效的抑制這里CIC5可以對混疊到帶內( 0~0. 59 MHz)的信號抑制82dB。

RCF和FIR設計

在確定了各級濾波器的抽取率之后,接下來就對RCF和FIR的設計了。最終的濾波結果要滿足通帶為590kHz,帶內波動為±1. 5dB,阻帶- 40dB@740kHz、- 80dB@900kHz的基帶濾波要求。

對于一個24階的FIR濾波器無法實現上述要求,而RCF的階數已經確定,無法做得更高,解決的方法有2種,一是采用多通道處理,二是在邏輯內部增加一級FIR濾波器來滿足濾波要求。本文主要討論第二種方案。

因為在RCF中要實現2倍抽取,為了使邏輯內的濾波有效,則RCF中濾波主要起到抗混疊作用,阻帶抑制指標可以放在后級濾波中實現,實際上在RCF(24階)中無法達到阻帶抑制的要求,也無法完全抑制900kHz處單音。折衷的設計是增加濾波器的過渡帶,在滿足抗混疊和單音抑制的條件下,使阻帶抑制達到80dB。這樣設計的結果是過渡帶加寬,后級的FIR濾波器需要更高的階數進行阻帶抑制和單音抑制。基于這樣的考慮,設計的濾波器結果如圖5、圖6和圖7所示。

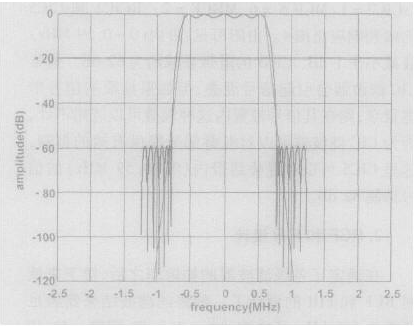

圖5RCF濾波器的幅頻響應

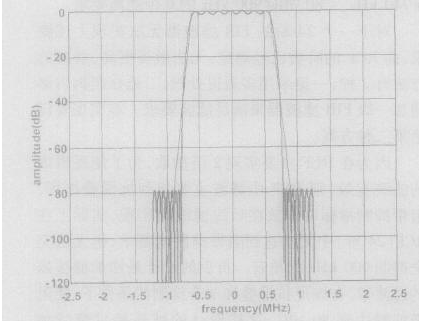

圖624階FIR濾波器的幅頻響應

圖732階FIR濾波器的幅頻響應

圖5中的A線為CIC5的響應,B線為CIC5和RCF的組合響應。帶內波動小于1dB。從圖中可以看出濾波的結果滿足抗混疊要求,阻帶抑制滿足- 80dB的要求,即可以濾除大于1. 15MHz頻帶內的單音,在后面的FIR濾波處理中主要是針對頻帶0. 59~1. 15MHz,需要使這個頻帶滿足阻帶抑制和900kHz處的單音抑制要求。在FIR的設計中可以實現較高的階數,考慮到邏輯資源的因素,此濾波器的階數不能做得太高,否則無法實現。考慮到RCF對0. 59~1. 15MHz頻帶衰減,FIR濾波器的阻帶衰減可以降低要求,只要兩者加起來滿足- 80dB的阻帶抑制則可。

如圖6和圖7所示,分別設計了24階和32階FIR濾波器,其中24階FIR濾波器的帶內波動小于1. 8 dB,32階FIR濾波器的帶內波動小于1. 5dB,阻帶抑制分別為- 60dB和- 80dB。由于該濾波器在FPGA內實現,只要邏輯資源夠用,可以根據實際需要滿足不同濾波要求。

結束語

經過上面的討論,初步完成基帶濾波器的設計過程,因為沒有進行篩選,所以上面的提到的一些系數和指標的確定也許不是最優化的。系數的優化和篩選,以及各個指標的確定需要大量工作,更需要在實際的硬件調試中進行驗證和優化。

事實上,反向基帶濾波器的指標是比較模糊的一個問題,究竟定為多少,標準中沒有規定。因此主要參考前向基帶濾波器的指標進行設計,是否合理還有待驗證。在實現上,主要是在資源允許的條件下,盡量將指標提得高一些。另一個問題是匹配濾波,即是否需要進行匹配濾波,以及如何進行匹配濾波,還需要進一步考慮。

責任編輯:gt

-

處理器

+關注

關注

68文章

19407瀏覽量

231180 -

芯片

+關注

關注

456文章

51170瀏覽量

427235 -

無線電

+關注

關注

60文章

2148瀏覽量

116808

發布評論請先 登錄

相關推薦

基于CPCI架構的軟件無線電處理最佳解決方案

軟件定義無線電技術的發展歷史

軟件無線電設計中有哪些主要環節?

基于DSP的軟件無線電直擴接收機的設計與實現

如何測量SDR軟件無線電

將FPGA嵌入DSP驅動的軟件無線電應用中

基于軟件無線電和接收信號處理器芯片AD6624實現基帶濾波器的設計

基于軟件無線電和接收信號處理器芯片AD6624實現基帶濾波器的設計

評論