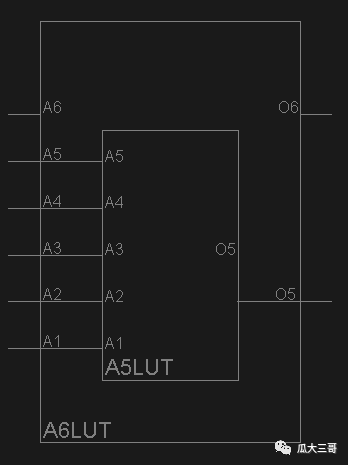

在 7 系列中實(shí)現(xiàn)數(shù)字電路的與、或、非等邏輯是通過(guò) 6 輸入的查找表實(shí)現(xiàn)的。LUT 有 6 個(gè)輸入(A1~A6)和 2 個(gè)輸出(O5~O6)。在一個(gè) Slice 中,四個(gè) LUT 分別是 A,B,C,D。

一個(gè) 6 輸入 LUT 使用:

A1~A6 輸入

O6 輸出

兩個(gè) 5 輸入或者更少使用:

A1~A5 輸入

A6 輸入為高

O5 和 O6 輸出

這里小編需要說(shuō)明的是,這些 LUT 輸出相當(dāng)于真值表值,所以學(xué)會(huì)數(shù)字電路這里理解起來(lái)就很方便。

在芯片上表現(xiàn)如下圖

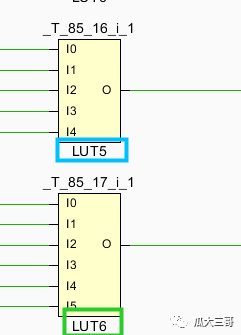

實(shí)際工程中綜合后網(wǎng)表中表現(xiàn)如下圖

當(dāng) LUT6 作為兩個(gè) 5 輸入 2 位輸出時(shí),A6 被強(qiáng)行寫(xiě)為1,MUX 選擇一個(gè) LUT5 的輸出結(jié)果到 O5,另一個(gè) LUT5 的輸出結(jié)果到 O6。

當(dāng) LUT6 作為 6 輸入,1位輸出時(shí)。一個(gè) LUT5 存放 A6 = 0 時(shí)的結(jié)果,另外一個(gè) LUT5 存放 A6 = 1 時(shí)的結(jié)果,通過(guò) MUX 可以組成 LUT6 輸出 O6。

除了基本的 LUT 之外, Slice 還包含三個(gè)選擇器:F7AMUX, F7BMUX, 和 F8MUX。

F7AMUX 用來(lái)產(chǎn)生 7 輸入的功能,它的輸入來(lái)源于 LUT A 和 LUT B。

F7BMUX 用來(lái)產(chǎn)生 7 輸入的功能,它的輸入來(lái)源于 LUT C 和 LUT D。

F8MUX 用來(lái)產(chǎn)生 8 輸入的功能,它的輸入來(lái)源于 F7AMUX 和 F7BMUX 。

編輯:jq

-

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1629瀏覽量

80823 -

LUT

+關(guān)注

關(guān)注

0文章

50瀏覽量

12577 -

Mux

+關(guān)注

關(guān)注

0文章

38瀏覽量

23458

原文標(biāo)題:Look-Up Table(LUT)

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字電路與控制系統(tǒng)關(guān)系

如何使用 Verilog 進(jìn)行數(shù)字電路設(shè)計(jì)

邏輯異或在數(shù)字電路中的作用

觸發(fā)器在數(shù)字電路中的作用是什么

時(shí)序邏輯電路的功能表示方法有哪些

數(shù)字電路中的基本邏輯關(guān)系有哪三種

數(shù)字電路中基本邏輯關(guān)系有哪三種

數(shù)字電路可以處理模擬信號(hào)嗎

數(shù)字電路是對(duì)什么信號(hào)進(jìn)行傳輸?shù)?/a>

輸入電流幾乎為零的門(mén)電路特點(diǎn)

組合邏輯電路邏輯功能的測(cè)試方法

數(shù)字電路和模擬電路的區(qū)別與聯(lián)系

數(shù)字電路仿真元件符號(hào)是什么

數(shù)字電路與邏輯設(shè)計(jì)

TTL電路是什么意思?TTL邏輯電平 TTL電路如何工作?

解析數(shù)字電路的與、或、非等邏輯是通過(guò) 6 輸入的查找表實(shí)現(xiàn)

解析數(shù)字電路的與、或、非等邏輯是通過(guò) 6 輸入的查找表實(shí)現(xiàn)

評(píng)論