參考:UG892 UG835

Vivado集成開發工具為設計者提供了非工程模式下的FPGA設計流程。在Vivado非工程模式下,FPGA開發人員可以更加靈活地對設計過程的每個階段進行控制,從而進一步提高FPGA的設計效率。

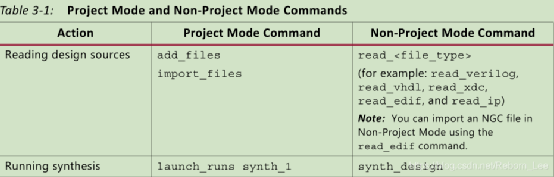

非工程模式下基本命令列表

| 命令 | 功能 |

| read_edif | 將EDIF或者NGC網表導入當前工程的設計源文件集合中 |

| read_verilog | 讀入用于非工程模式會話的Verilog(.v)和SystemVerilog(.sv)源文件 |

| read_vhdl | 讀入用于非工程模式會話的VHDL(.vhd或vhdl)源文件 |

| read_ip | 讀入用于非工程模式會話的已經存在的IP(.xco或者.xci)工程文件。使用來自.xco IP工程的.ngc網表。對于.xci IP,使用RTL用于編譯;或者如果存在網表,則使用網表 |

| read_xdc | 讀入用于非工程模式會話的.sdc或者.xdc文件 |

| set_param set_property | 用于多個目的。例如,它可以定義設計配置和工具設置等 |

| link_design | 如果會話中使用網表文件,則對設計進行編譯,用于綜合目的 |

| synth_design | 啟動Vivado綜合,包含設計的頂層模塊名字和目標器件參數 |

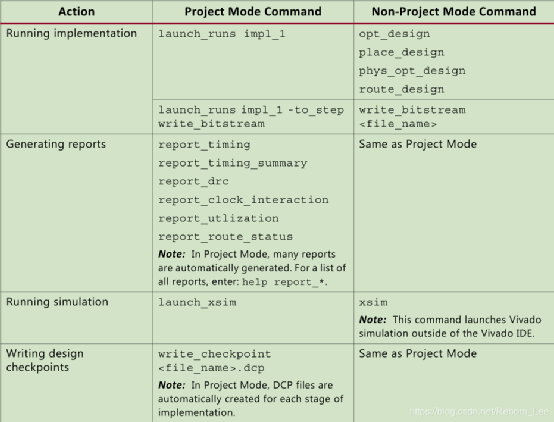

| opt_design | 執行高層次設計優化 |

| power_opt_design | 執行智能時鐘門控,用于降低系統的整體功耗(可選) |

| place_design | 對設計進行布局 |

| phys_opt_design | 執行物理邏輯優化,以改善時序和布線能力(可選) |

| route_design | 對設計進行布線 |

| report* | 運行多個標準的報告,可以在設計過程的任何一個階段運行它 |

| write_bitstream | 生成一個比特流文件,并且運行DRC |

| write_checkpoint read_checkpoint | 在設計流程的任何點保存設計。一個設計檢査點由網表和約束構成,它們在設計流程的該點進行了優化,以及包含實現的結果 |

| start_gui stop_gui | 調用在存儲器中當前設計的Vivado集成開發環境 |

典型TCL腳本

為了方便讀者從整體上了解在Vivado非工程模式下的基本命令的功能,下面將給出用于Vivado設計套件示例的非工程模式TCL腳本,該腳本可以說明使用設計檢查點、用于保存設計流程中各個階段的數據庫狀態和手工生成各種報告的方法。 通過下面的命令運行該Tcl腳本文件: vivado -mode tcl –source create_bft_batch.tcl

|

Following is an example of a Non-Project Mode script, which reads in various source files: # create_bft_batch.tcl # bft sample design # A Vivado script that demonstrates a very simple RTL-to-bitstream batch flow # # NOTE: typical usage would be "vivado -mode tcl -source create_bft_batch.tcl" # # STEP#0: define output directory area. # set outputDir ./Tutorial_Created_Data/bft_output file mkdir $outputDir # # STEP#1: setup design sources and constraints # read_vhdl -library bftLib [ glob ./Sources/hdl/bftLib/*.vhdl ] read_vhdl ./Sources/hdl/bft.vhdl read_verilog [ glob ./Sources/hdl/*.v ] read_xdc ./Sources/bft_full.xdc # # STEP#2: run synthesis, report utilization and timing estimates, write checkpoint design # synth_design -top bft -part xc7k70tfbg484-2 -flatten rebuilt write_checkpoint -force $outputDir/post_synth report_timing_summary -file $outputDir/post_synth_timing_summary.rpt report_power -file $outputDir/post_synth_power.rpt # # STEP#3: run placement and logic optimzation, report utilization and timing estimates, write checkpoint design # opt_design place_design phys_opt_design write_checkpoint -force $outputDir/post_place report_timing_summary -file $outputDir/post_place_timing_summary.rpt # # STEP#4: run router, report actual utilization and timing, write checkpoint design, run drc, write verilog and xdc out # route_design write_checkpoint -force $outputDir/post_route report_timing_summary -file $outputDir/post_route_timing_summary.rpt report_timing -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt report_clock_utilization -file $outputDir/clock_util.rpt report_utilization -file $outputDir/post_route_util.rpt report_power -file $outputDir/post_route_power.rpt report_drc -file $outputDir/post_imp_drc.rpt write_verilog -force $outputDir/bft_impl_netlist.v write_xdc -no_fixed_only -force $outputDir/bft_impl.xdc # # STEP#5: generate a bitstream # write_bitstream -force $outputDir/bft.bit |

Vivado集成開發環境分析

3.1 啟 動 Vivado集 成 開 發 環 境 當工作在非工程模式時,對于存儲器中活動的設計來說,使用下面的命令打開/關閉Vivado集成開發環境。

(l)start_gui,打開Vivado集成開發環境,用于存儲器中活動的設計。

(2)stop_gui,關閉Vivado集成開發環境,并且返回“Vivado Design Suite Tcl shell”界面。 在設計過程的每個階段,設計者均可以打開Vivado集成開發環境,對存儲器中保存的當前設計進行分析和操作。

在非工程模式下,在Vivado集成開發環境中,一些工程的特性是不可用的,如Flow Navigator、Project Summary,以及源文件的訪問、管理和運行。

然而,通過Vivado集成開發環境的Tools菜單,可以使用分析及修改約束等很多特性。 需要知道的是,在Vivado集成開發環境中,對存儲器中的設計所做的任何變化都會自動應用到下游工具中,這里沒有保存的功能。如果設計者想要將約束的變化用于后續的運行,則在Vivado集成幵發的環境的主菜單下,執行菜單命令【File】—【Export】—【Export Constraints】,寫到一個新的包含所有XDC文件的文件中。

3.2 打開設計檢查點的方法 通過Vivado集成設計環境,設計者可以在保存的設計點上對設計進行分析。

通過使用Tcl命令(synth_design、opt_design、power_opt_design、place_design、phys_opt_design和route_deSign),設計者可以在非工程模式下運行一個設計,并且可以在任何階段保存一個設計。這樣,就可以在Vivado集成設計環境中讀取設計。

設計者可以從一個布線后的設計開始,分析時序,僅通過布局來解決時序問題。然后保存剛才的工作,甚至設計中還沒有進行的布線操作。Vivado集成設計環境顯示打開設計點的名字。 設計者可以打開、分析和保存設計檢查點,也可以將變化保存到新的設計點。

(1)在Vivado集成開發環境下,執行菜單命令【File】->【Save Checkpoint】,保存對當前設計檢查點的修改。

(2)在Vivado集成開發環境下,執行菜單命令【File】—【Write Checkpoint】,將設計檢查點的當前狀態保存到一個新的設計檢查點中。

關于具體的每個命令的使用下一節將細致分析。

編輯:jq

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606060 -

vhdl

+關注

關注

30文章

817瀏覽量

128345 -

DRC

+關注

關注

2文章

150瀏覽量

36363 -

Vivado

+關注

關注

19文章

815瀏覽量

66895

原文標題:無招勝有招-Vivado非工程模式下的FPGA設計流程

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【米爾-Xilinx XC7A100T FPGA開發板試用】Key-test

Vivado之實現布局布線流程介紹

如何在服務器上調試本地FPGA板卡

FPGA無芯片HDMI接入方案及源碼

一個更適合工程師和研究僧的FPGA提升課程

在不重新安裝Vivado的情況下,是否能夠安裝線纜驅動器?

AMD FPGA中MicroBlaze的固化流程詳解

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

深入探索Vivado非工程模式FPGA設計流程

詳解Vivado非工程模式的精細設計過程

淺析Vivado在非工程模式下的FPGA設計流程

淺析Vivado在非工程模式下的FPGA設計流程

評論