雷達系統在研制過程中,各部分往往是并行的,在調試信號處理分系統時,如果天線沒做好,就得不到陣面送下來的回波數據,這時調試就無法正常進行。為了解決這一問題,往往先設計一個模目信號,把信號處理分系統調試好,待其他分系統也調試好后,再切換為正常接收模式,進行系統聯試。

本文介紹了一種模目信號設計方法,利用FPGA產生時序及控制,DSP實時計算所需要的回波,從而實現對雷達目標回波的模擬,這樣可以在沒有陣面數據的情況下,使信號處理分系統調試能夠正常進行,從而不影響科研進度,做到有問題早發現。

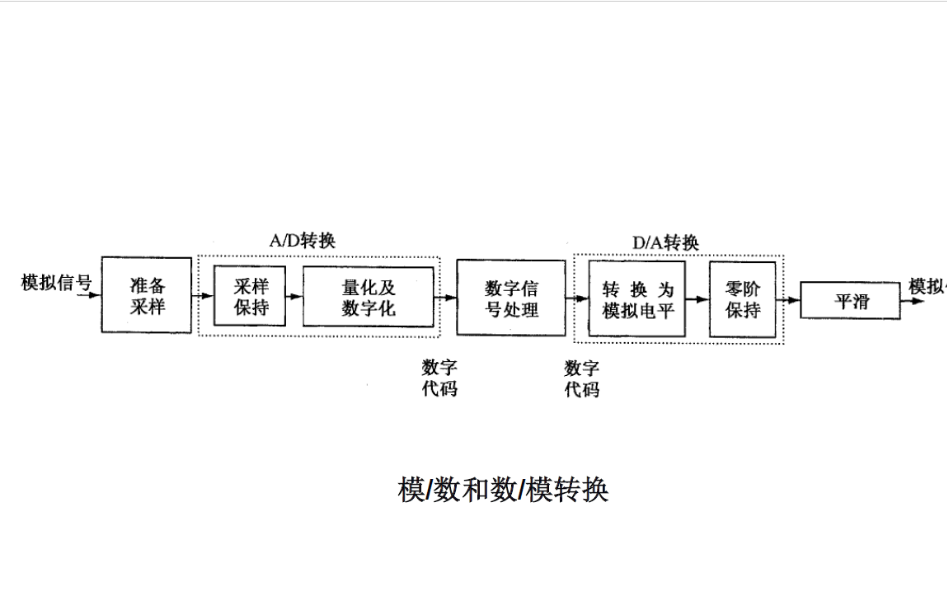

1系統原理

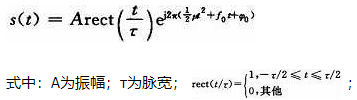

由于要調試的是PD體制雷達,所以要模擬的信號是帶有多普勒頻移的雷達目標回波。這里雷達發射波形為線性調頻信號,其時域表達式為:μ為調頻斜率;fo為載頻;φo為初相。那么當雷達對空照射時,如果遇到目標,就會產生回波,回波是受目標調制了的發射信號,所以通過和發射信號相比較,就可獲得目標的相關信息,在此僅考慮目標相對雷達勻速徑向飛行的情況。當回波被雷達接收后,經過解調,得到的將是帶有多普勒頻移的線性調頻信號,由于已假設目標沿徑向勻速飛行,所以回波信號相對于發射信號來說,在相位上僅時間的一次項改變,即發生了多普勒頻移。回波的時延反映目標的遠近,幅度反映目標的散射截面積。

通過以上分析可知,要產生模目信號,可以通過改變發射信號(未調制至載波)的頻率中心、時延和幅度這三個參數來實現,通過對這三個變量的控制,就可模擬出目標的徑向速度、徑向距離以及雷達散射截面積。

2系統方案

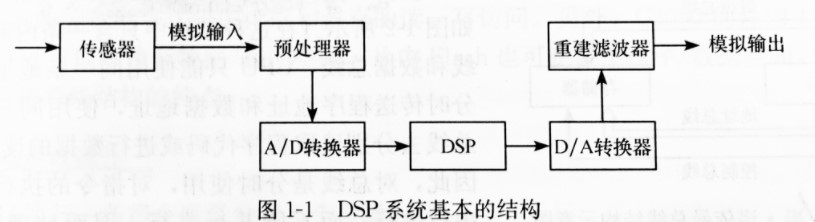

由于模目信號可以通過改變發射信號得到,又發射信號的波形已知,所以可以通過對發射信號進行實時變換,來模擬所期望的回波。系統實現如下:為了解距離和速度二維模糊,雷達設置了N種重頻,每種重頻的脈寬不同,在系統帶寬(其決定雷達的距離分辨率)一定的情況下,每種重頻發射信號的點數為:脈沖時寬×系統帶寬,此點數也就是目標回波的點數,這樣就可以預先把發射波形存于DSP內存,然后根據系統控制字,取出需要的波形,再在DSP中實時計算出所需要的模目信號。模目信號需要系統時序來同步,系統時序如圖1所示。

圖1系統時序

圖1中BW為雷達波位脈沖,CPI為相干脈沖導前,FR為單個脈沖信號。系統會在每個CPI到來時打入系統控制字,告訴信號處理分系統陣面ID、工作模式、CPI代碼等信息,信號處理分系統會根據收到的控制字來進行相應的工作,模目距離和模目多普勒也會在系統控制字中給出,這樣就可在系統時序同步下,根據所收到的控制字產生模目信號。

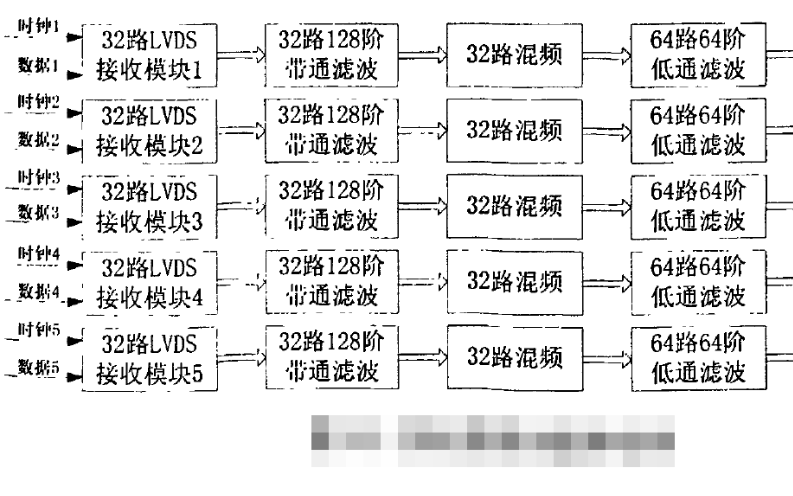

模目信號屬于系統內部的測試信號,所以不需要單獨的插件產生,可以考慮做在信號處理流程比較靠前的插件上,比如DBF插件或者脈壓插件。由于本系統脈壓插件資源有剩余,且對于產生模目信號足夠,所以將模目產生模塊放在脈壓插件上,用到的器件是一片FPGA和一片DS-P,其中FPGA的作用是接收光纖送來的控制字,對DSP發起中斷并緩存DSP產生的模擬回波,然后在系統時序的同步下將模擬回波送后續處理;DSP的作用是根據系統控制字信息,在一個FR時間間隔內產生所需要的多波束目標回波,系統實現框圖如圖2所示。

圖2系統實現框圖

系統工作流程為:DBF分機提供系統控制字、時序和外時鐘,其中系統控制字通過光纖送出,每個CPI送一次,時序和外時鐘通過射頻電纜送出。當FPGA收到控制字后,將其緩存于雙口RAM,等到第二個FR,給DSP發起中斷,通知DSP取走控制字。DSP從控制字中提取CPI代碼、FR代碼、模目距離和模目多普勒等信息。通過CPI代碼可以知道雷達當前發射的是哪種波形,即哪種線形調頻信號,通過FR代碼可以知道當前脈沖是該相干處理脈沖組中第幾個脈沖,通過模目距離和模目多普勒可以知道系統要求模擬目標所處的距離和相對徑向速度。由于系統控制字已在第二個FR得到,所以在接下來的FR中,DSP只需讀進FR序列號,就不需要再讀控制字。讀FR序列號的目的是為了計算模目由于存在徑向速度而產生的相位,即φd=fd(n-1)Tr,其中:n即為FR序列號;Tr為脈沖重復周期,一旦獲得這些信息,就可以計算模目。在計算模目的過程中,采用了乒乓存儲方式,即當前FR產生下一FR的數據,并存于FPGA的雙口RAM中,等下一FR到來時,延遲到系統控制字所給的模目距離單元所對應的時刻,讀出模目數據即可。為了使目標回波與實際情況一致,要求模目信號在距離和多普勒上都要模糊,由于系統控制字送來的參數是非模糊的,那么轉換方法為:模糊距離=真實距離mod本相干處理脈沖組對應的距離,模糊多普勒一真實多普勒mod本相干處理脈沖組對應的重頻,其中mod為求模,這一過程在DSP中完成。

3調試過程

調試所用到的分機有:綜合電子分機,送時序和控制字;DBF分機,完成控制字中CPI代碼和FR代碼的填充,并通過光纖將控制字送至DSP分機,本模目信號產生模塊就在DSP分機的脈壓插件上;頻率源,給每個分機提供時鐘;除此之外,還需要一臺直流穩壓電源。

系統加電后,DSP初始化完成就處于等待狀態,當有時序和系統控制字送來,DSP就根據控制字的要求產生模目信號,并在時序的同步下將信號送往FPGA,然后再由FPGA送后續處理。系統設置三個信號采集和觀察點,第一個在DSP上,通過仿真器采集系統控制字以及產生的模目數據,并將該數據和Matlab計算的數據做比較,看是否正確;第二個在FPGA上,通過Quartus自帶的SignalTap工具,觀察產生的模目信號波形,以及該信號經脈壓后的波形,看波形是否為線性調頻信號,點數是否正確,脈壓能否出結果;第三個在DSP插件上,通過在DSP上采集脈壓后的信號,對同一距離單元做FFT,看結果是否在期望的距離單元及期望的頻道上。

下面給出其中一種模擬波束在各信號采集和觀察點的圖形:圖3為DSP計算的模目數據(實部),圖4為SignalTap采集的模目信號(I,Q雙通道),圖5為模目信號經脈壓后的波形,圖6為對脈壓后同一距離單元信號做FFT。

圖6對脈壓后同一距離單元信號做FFT

可見系統正確模擬了目標回波,達到了預期效果。

4結語

本文介紹了一種雷達模目信號產生方法,該方法能夠通過FPGA和DSP實時產生具有多普勒頻移的多波束雷達目標回波,其意義在于可以為雷達信號處理分系統單獨調試提供數據來源,從而不必等待天線陣面的真實數據,這樣可以加快科研進度,也方便整機聯試時查找問題。

責任編輯:gt

-

dsp

+關注

關注

554文章

8059瀏覽量

350417 -

FPGA

+關注

關注

1630文章

21796瀏覽量

605998 -

雷達

+關注

關注

50文章

2966瀏覽量

118017

發布評論請先 登錄

相關推薦

基于FPGA和DSP的雷達模目信號設計

數字信號處理器的特點

數字信號處理器(DSP)

基于雙數字信號處理器(DSP)的實時相關圖像處理系統的設計

基于數字信號處理器實現雷達信號處理系統的設計

如何使用FPGA實現數字信號處理算法的研究

基于可編輯邏輯和數字信號處理器實現雷達模目信號的應用設計

基于可編輯邏輯和數字信號處理器實現雷達模目信號的應用設計

評論