在Vitis 統一軟件平臺中使用v++ -link命令,可以把各種類型Kernel(C, C++, OpenCL C, 以及 RTL)的對象文件(.XO)整合到目標平臺中,最終生成器件的二進制文件XCLBIN

在Vitis完成這個過程的底層,實際調用的是Vivado。Vitis會指定默認的Vivado策略來執行綜合和實現的步驟。當默認的Vivado策略無法達到預期的時序要求時,我們需要在Vivado中分析時序問題的原因(不在本篇中詳細討論), 并根據時序失敗的原因調整Vivado各個步驟的選項。有時我們也需要調整Vivado各個步驟的選項做不同方向的優化。

在Vitis中提供了“--vivado” 選項來精細控制Vivado各個步驟的選項,幾乎所有期望加在Vivado中的選項都可以通過這個選項傳遞給Vivado。以下操作如何選擇合適的選項需要對于Vivado的運行機制有一定的了解,對于Vivado不熟悉的用戶,建議先閱讀UG901以及UG904,兩者分別是綜合和實現的使用手冊

1. 對于應用于Vivado的參數使用選項:

--vivado.param 《object》《parameter》=《value》

舉例:

--vivado.param project.writeIntermediateCheckpoints=1

對應Vivado中參數設置的命令:

set_param project.writeIntermediateCheckpoints

這個命令也可以放在Vivado各個階段的TCL.PRE/TCL.POST所指定的腳本中用--vivado.prop 執行(參考“Vivado工程的屬性設置”的內容)

對應configure文件的內容:

[vivado]

param=project.writeIntermediateCheckpoints=1

2. 對于Vivado工程的屬性設置:

--vivado.prop 《object_type》。《object_name》。《prop_name》

這里的Object_type是可以是run, fileset, file 或者 project

舉例:

v++ --link --vivado.prop run.impl_1.STEPS.PHYS_OPT_DESIGN.IS_ENABLED=true

--vivado.prop run.impl_1.STEPS.PHYS_OPT_DESIGN.ARGS.DIRECTIVE=Explore

--vivado.prop run.impl_1.STEPS.PLACE_DESIGN.TCL.PRE=/…/xxx.tcl

《1》 指定了在Vivado 實現階段執行PHYS_OPT_DESIGN步驟

(注:Vivado中PHYS_OPT_DESIGN步驟默認并不執行)

《2》 指定了在PHYS_OPT_DESIGN步驟采用的directive 是 Explore

《3》 指定了在Place_design之前需要先執行一個tcl腳本。

對應configure文件的內容:

[vivado]

prop=run.impl_1.steps.phys_opt_design.is_enabled=1

prop=run.impl_1.STEPS.PHYS_OPT_DESIGN.ARGS.DIRECTIVE=Explore

prop=run.impl_1.STEPS.PLACE_DESIGN.TCL.PRE=/…/xxx.tcl

不少Vivado實現階段的選項無法直接在Vivado工程模式的各個階段的既有選項中直接體現,例如在opt_design 階段,我只想執行 -sweep 選項,這時我們可以用到這些步驟的“More Option”

opt_design -sweep 相當于在在工程模式中設置opt_design的More option 為 -sweep

由于“More Option” 這個選項中含有空格,使用起來要相當小心。一旦用錯,這個選項在v++中可能和其他的選項混淆,導致工具報一些看似無關的錯誤

示例:

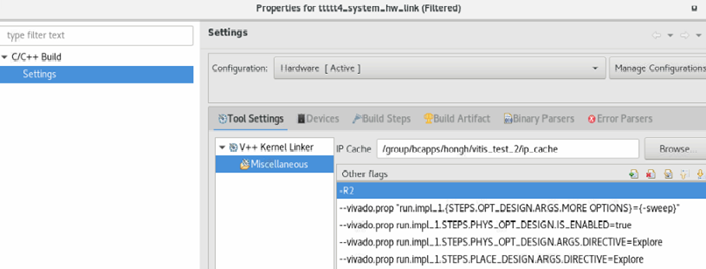

--vivado.prop “run.impl_1.{STEPS.OPT_DESIGN.ARGS.MORE OPTIONS}={-sweep}”

我們先將Vivado的相關屬性加到Vitis link的選項中

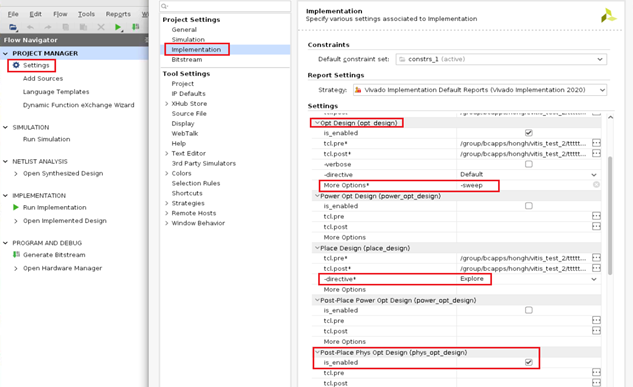

完成Vitis platform link之后,打開生成的Vivado 工程,我們可以看到之前設置的Vivado 屬性都能體現在底層Vivado工程中:

(Vivado工程文件所在目錄(不同版本可能有所差異):

XX/XX_system_hw_link/Hardware/binary_container_1.build/link/vivado/vpl/prj/prj.xpr)

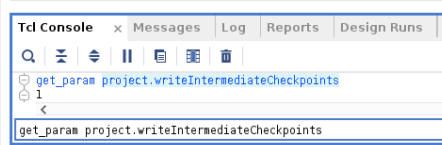

在Vivado 的TCL CONSOLE中可以執行get _param命令查看parameter是否已經設置成功:

編輯:jq

-

Vitis

+關注

關注

0文章

147瀏覽量

7497

原文標題:開發者分享 | 如何在Vitis中把設置信息傳遞到底層的Vivado (上)

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AMD Vitis Unified Software Platform 2024.2發布

U50的AMD Vivado Design Tool flow設置

CDCE949如何使用Clock Pro 1.21來計算寄存器的值,并導出配置信息呢?

使用Python腳本備份華為交換機的配置信息

神經元的信息傳遞方式是什么

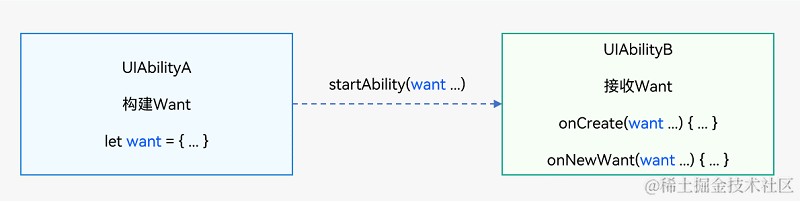

鴻蒙開發:信息傳遞載體Want

abb機器人怎么設置原點位置信號

在Windows 10上創建并運行AMD Vitis?視覺庫示例

如何基于Vitis中把設置信息傳遞到底層的Vivado

如何基于Vitis中把設置信息傳遞到底層的Vivado

評論