1.1早期的PROM技術(shù)實(shí)現(xiàn)

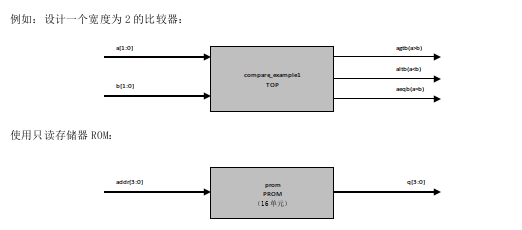

在上世紀(jì)60年代以后,小規(guī)模集成電路出現(xiàn),需要實(shí)現(xiàn)一個(gè)組合邏輯的方法,是一種基于PROM(Programable ROM Based)的技術(shù),其原理是將組合電路的真值表寫入ROM中,用PROM設(shè)備實(shí)現(xiàn)定制邏輯的真值表,等效于實(shí)現(xiàn)定制邏輯。

這里控制信號(hào)從略。

首先,將比較器的真值表填寫:

| 索引號(hào) | a[1] | a[0] | b[1] | b[0] | agtb(a>b) |

altb(a|

aeqb(a=b) |

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 4 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 8 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 10 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| 11 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 12 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 13 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 14 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 15 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

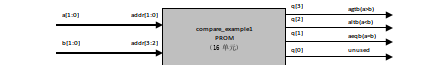

將真值表寫入PROM中,使用PROM設(shè)備實(shí)現(xiàn)比較器:

等效的實(shí)現(xiàn)定制邏輯。

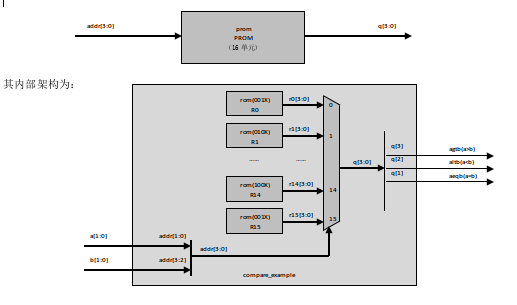

為了進(jìn)一步了解PROM技術(shù)的本質(zhì),需要知道ROM設(shè)備的架構(gòu)和原理:

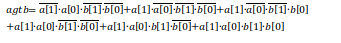

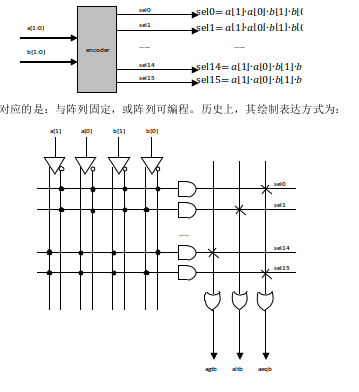

1.2基于PROM技術(shù)的SOP(積之和最小項(xiàng))

數(shù)字電路中,將真值表用邏輯門實(shí)現(xiàn)的常用方法為SOP(Sum Of Products):

| 索引號(hào) | a[1] | a[0] | b[1] | b[0] | agtb(a>b) |

altb(a|

aeqb(a=b) |

|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 4 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 5 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 8 | 1 | 0 | 0 | 0 | 1 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| 10 | 1 | 0 | 1 | 0 | 0 | 0 | 1 |

| 11 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 12 | 1 | 1 | 0 | 0 | 1 | 0 | 0 |

| 13 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 14 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 15 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

PROM設(shè)備中,多路器的選擇信號(hào)對(duì)應(yīng)地址的譯碼邏輯

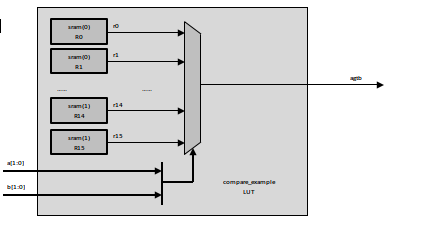

1.3基于查找表技術(shù)的定制邏輯

上世紀(jì)80年代,CPLD的出現(xiàn),以及之后的FPGA,為了解決輸入端和存儲(chǔ)單元的2的n次方問題,出現(xiàn)了查找表LUT技術(shù)。查找表LUT其原理同樣是用固定的(硬核)多路器,基于SRAM技術(shù),實(shí)現(xiàn)定制邏輯的真值表,從而等效的實(shí)現(xiàn)定制邏輯。其中一個(gè)重要的變化,是將真值表項(xiàng)寫入SRAM(靜態(tài)存儲(chǔ)器)中,而不是用反溶絲技術(shù)(OTP),從而實(shí)現(xiàn)在線編程(沿用至今)。同樣用上面的二輸入比較器為例:

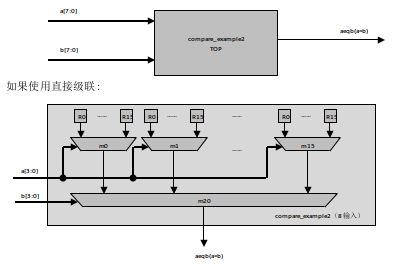

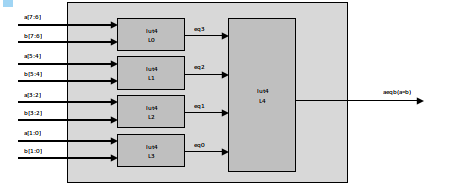

以上例子中,所需要的存儲(chǔ)器單元仍然是16個(gè)單元,為2的4次方。為了清楚LUT的減輸入法過程,我們將輸入端增加到16(與或陣列,需要65536單元):

這里使用的存儲(chǔ)器為:16*16=65536。并沒有解決存儲(chǔ)器數(shù)量增加的問題。但使用四輸入LUT的實(shí)際架構(gòu)(含減輸入法)為:

這里,僅僅使用了5*16=80個(gè)存儲(chǔ)器單元。

1.4在線編程技術(shù)

CPLD出現(xiàn)之前,PLD設(shè)備大多采用反熔絲技術(shù)(Anti-Fuse),交叉編程位置在編程前為高阻抗,編程后為很低的阻抗,為導(dǎo)通態(tài)。反熔絲技術(shù)為一次性編程(OTP),實(shí)際使用并不方便,但其好處是便于保護(hù)知識(shí)產(chǎn)權(quán)。在LUT技術(shù)出現(xiàn)以后,設(shè)計(jì)者的定制邏輯真值表和整個(gè)設(shè)計(jì)的網(wǎng)表(含路由),是寫入靜態(tài)存儲(chǔ)器SRAM中,具有速度快,支持在線編程(可反復(fù)擦除),但其缺點(diǎn)是揮發(fā)性(掉電即失),F(xiàn)PGA每次上電以后,需要重新裝入(有一個(gè)比較復(fù)雜的配置過程)。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606046 -

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164348 -

硬件

+關(guān)注

關(guān)注

11文章

3382瀏覽量

66457

原文標(biāo)題:FPGA學(xué)習(xí)——FPGA的硬件架構(gòu)和工作原理

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Verilog vhdl fpga

FPGA基礎(chǔ)知識(shí)及設(shè)計(jì)和執(zhí)行FPGA應(yīng)用所需的工具

FPGA芯片架構(gòu)和資源有深入的理解,精通Verilog HDL、VHDL

# FPGA 編程如何工作?

FPGA芯片的工作原理和使用

fpga是硬件還是軟件

fpga封裝技術(shù)和arm架構(gòu)的優(yōu)缺點(diǎn)

交換芯片架構(gòu)是什么意思 交換芯片架構(gòu)怎么工作

fpga芯片架構(gòu)介紹

fpga全稱是什么?fpga的工作原理是什么?

fpga芯片工作原理 fpga芯片有哪些型號(hào)

fpga是硬件還是軟件

fpga是什么架構(gòu)

數(shù)字繼電器的工作原理及硬件架構(gòu)分析

FPGA的硬件架構(gòu)和工作原理

FPGA的硬件架構(gòu)和工作原理

評(píng)論