門控時鐘的設計初衷是實現FPGA的低功耗設計,本文從什么是門控時鐘、門控時鐘實現低功耗的原理、推薦的FPGA門控時鐘實現這三個角度來分析門控時鐘。

一、什么是門控時鐘

門控時鐘技術(gating clock) 是通過在時鐘路徑上增加邏輯門對時鐘進行控制,使電路的部分邏輯在不需要工作時停止時鐘樹的翻轉,而并不影響原本的邏輯狀態。在ASIC和FPGA設計中都存在門控時鐘的概念(前者應用更廣)。

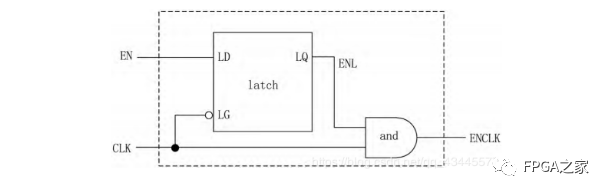

典型的門控時鐘邏輯如下圖所示:

二、門控時鐘降低功耗的原理

1. FPGA功耗分類

靜態功耗:靜態功耗又叫泄漏功耗,它是指電路處于等待或不激活狀態時-泄漏電流所產生的功耗。通常由FPGA制造工藝的優化而提升。同一代的FPGA產品中,也有專門的低功耗版本(譬如Intel開發的Cyclone10 GX與Cyclone 10 LP,后者為低功耗版本low power但前者性能更強)。可以在FPGA選型時加以考慮。

動態功耗:是指電容充放電功耗和短路功耗,是由電路的翻轉造成的。FPGA中的動態功耗主要體現在元件的電平翻轉時對負載電容的充放電及時鐘的翻轉。

2. 為什么門控時鐘可以降低功耗

當系統中某模塊電路完成既定任務后(譬如TDC中對BIN的標定等初始化類任務),通過門控時鐘使能信號的控制,使得驅動該模塊的時鐘停止翻轉,相應的時序元件不再更新,那么其間的組合邏輯也恢復到靜態。此時該模塊的功耗相當于靜態功耗,從而降低了整個系統的功耗。

三、不合理的門控時鐘設計

1.偽門控時鐘

如下圖所示,設計中有意識地使用使能信號,意圖維持寄存器的數據。但是僅對寄存器組的數據輸入端添加選擇器和使能信號,并不妨礙寄存器組時鐘輸入端的翻轉,輸出維持不變只是因為存在反饋回路在不斷的進行使能判斷、輸出、使能判斷、輸出的循環。實則并沒有起到低功耗的作用。

當然某些情況下確實需要用到這種設計,此處僅用來和門控時鐘做區分,避免混淆。

2.直接門控時鐘

將使能信號直接連接在AND門,結構簡單。不足之處在于產生使能信號的組合邏輯的毛刺將完全地反應到AND門,造成門控時鐘輸出質量變差(clk_en將會有占空比不良和毛刺等情況)。

四、推薦的門控時鐘設計

1.基于鎖存器的門控時鐘

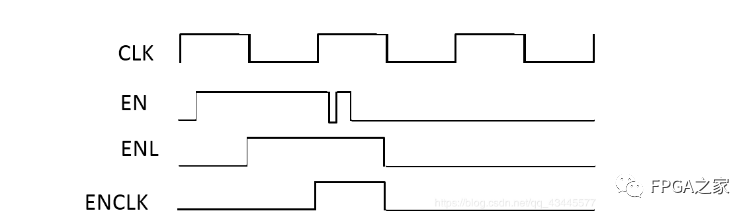

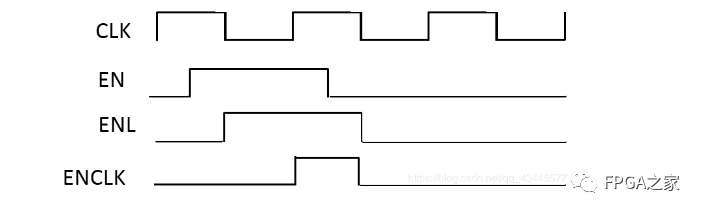

鎖存器是電平敏感的元件,此圖中當CLK信號為低電平時,鎖存器透明,EN端數據直接傳輸至AND門的一端(ENL),AND門另一端連接CLK。

當產生使能信號的組合邏輯不復雜時,產生使能信號的時間小于半個時鐘周期。在CLK高電平時,鎖存器的引入有效地過濾了前段組合邏輯競爭冒險產生的毛刺;在時鐘低電平時,前段組合邏輯的毛刺將受到AND門控制將無法輸出。較好地實現了門控時鐘的要求。

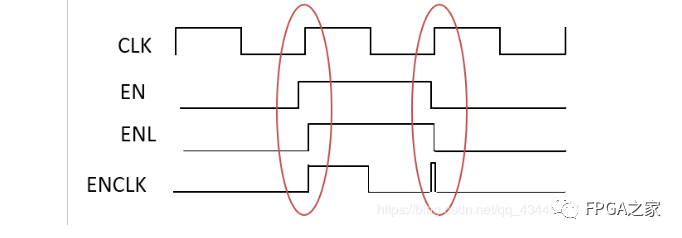

當產生使能信號的組合邏輯復雜時,產生使能信號的時間大于半個時鐘周期。考慮鎖存器的延時,那么對于首個ENCLK周期而言,占空比將被削減;當EN信號拉低時,則有可能產生毛刺。均不利于后續寄存器組的時序過程。

這種情況難以通過在鎖存器前端加同步寄存器避免,因為此時的使能信號是不滿足寄存器的建立時間的,大概率會產生亞穩態現象。因此產生門控使能信號的組合邏輯應當盡可能簡化,保證在半個時鐘周期之內得到穩定電平。

保險起見,一方面,保證使能信號半周期確定;另一方面,在鎖存器之前加一級上升沿觸發的寄存器,過濾輸入鎖存器的信號。

2.基于寄存器的門控時鐘

上面介紹的基于鎖存器的門控時鐘實際上更適合在ASIC中實現,一方面FPGA中沒有專門的鎖存器資源,需要利用其中的組合邏輯資源外加寄存器來等效地實現,不經濟;另一方面,鎖存器本身的特性沒法進行靜態時序分析,出問題了不易排查。

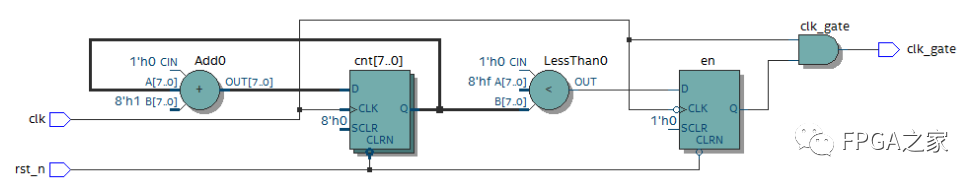

真正適合在FPGA中實現的是基于寄存器的門控時鐘,如下圖所示。

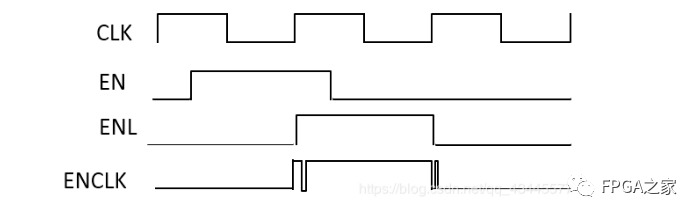

前段使用加法器產生計數值,通過比較器產生使能信號,送入使能寄存器。值得注意的是,前端產生使能邏輯時序元件是上升沿觸發,而使能寄存器是下降沿觸發。如此一來,同樣需要滿足產生使能信號的組合邏輯簡單這一前提要求(半周期內達到en寄存器的建立時間)。好處在于,AND門時時刻刻都只有一個輸入在變,不容易產生毛刺。時序圖如下:

為了便于理解,此處給出若使能寄存器也是上升沿觸發的時序圖:

可見,AND門變化時兩個個輸入在變,容易產生毛刺。

五、討論

只有當FPGA工程需要大量降低功耗時才有必要引入門控時鐘,若必須引入門控時鐘,則推薦使用基于寄存器的門控時鐘設計。

在時鐘樹的枝干處使用門控,而不是在枝丫處使用門控。

使用門控時,應該注意時鐘的質量(使用專用時鐘網絡),畢竟好的時鐘才能產生好的使能信號和門控時鐘信號。同時,產生使能信號的邏輯不能太復雜,確保可以滿足使能寄存器的建立時間和保持時間。

與或門控輸出的時鐘信號,需要在timeanalyzer中設置為base clock。否則將會引入人為的時鐘偏斜。如下,將會以沒有使能寄存器的門控路徑作為最短分析路徑,以有寄存器的路徑作為最長路徑分析。

In certain cases, converting the gated clocks to clock enables may help reduce glitch and clock skew, and eventually produce a more accurate timing analysis. You can set the Quartus II software to automatically convert gated clocks to clock enables by turning on the Auto Gated Clock Conversion (在綜合的設置里面)option. The conversion applies to two types of gated clocking schemes: single-gated clock and cascaded-gated clock

類似地,產生門控時鐘信號最好只有一個兩輸入AND門(OR門)。附加邏輯越多,產生毛刺可能性越大。

編輯:jq

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605998 -

門控時鐘

+關注

關注

0文章

27瀏覽量

8972 -

CLK

+關注

關注

0文章

127瀏覽量

17236

原文標題:FPGA設計之門控時鐘

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

EE-244:門控時鐘與ADSP-21065L SHARC處理器接口

門控rs鎖存器和觸發器的區別是什么

用于電源門控應用的TPL5111毫微功耗系統計時器數據表

CDCE(L)949:支持SSC以降低EMI的靈活低功耗LVCMOS時鐘發生器數據表

LMH0366 3Gbps HD/SD SDI低功耗時鐘數據表

什么是門控時鐘 門控時鐘降低功耗的原理

什么是門控時鐘 門控時鐘降低功耗的原理

評論