1、什么是Setup 和Holdup時間?

答:Setup/hold time 是測試芯片對輸入信號和時鐘信號之間的時間要求。 建立時間是指觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間。輸入信號應提前時鐘上升沿(如上升沿有效)T時間到達芯片,這個T就是建立時間-Setup time。如不滿足setup time,這個數據就不能被這一時鐘打入觸發器,只有在下一個時鐘上升沿,數據才能被打入觸發器。 保持時間是指觸發器的時鐘信號上升沿到來以后,數據穩定不變的時間。如果holdtime不夠,數據同樣不能被打入觸發器。

2、什么是競爭與冒險現象?解決辦法?

答:在組合邏輯中,由于門的輸入信號通路中經過了不同的延時,導致到達該門的時間不一致叫競爭。產生毛刺叫冒險。如果布爾式中有相反的信號則可能產生競爭和冒險現象。 解決方法:一是添加布爾式的消去項,二是在芯片外部加電容。三加選通信號。用D觸發器,格雷碼計數器,同步電路等優秀的設計方案可以消除。

3、如何解決亞穩態?Metastability

答:亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。當一個觸發器進入亞穩態時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。在這個穩定期間,觸發器輸出一些中間級電平,或者可能處于振蕩狀態,并且這種無用的輸出電平可以沿信號通道上的各個觸發器級聯式傳播下去。 解決方法: 1 、降低系統時鐘頻率 2 、用反應更快的Flip-Flop 3 、引入同步機制,防止亞穩態傳播 4 、改善時鐘質量,用邊沿變化快速的時鐘信號 關鍵是器件使用比較好的工藝和時鐘周期的裕量要大。

4、說說靜態、動態時序模擬的優缺點

靜態時序分析是采用窮盡分析方法來提取出整個電路存在的所有時序路徑,計算信號在這些路徑上的傳播延時,檢查信號的建立和保持時間是否滿足時序要求,通過對最大路徑延時和最小路徑延時的分析,找出違背時序約束的錯誤。它不需要輸入向量就能窮盡所有的路徑,且運行速度很快、占用內存較少,不僅可以對芯片設計進行全面的時序功能檢查,而且還可利用時序分析的結果來優化設計,因此靜態時序分析已經越來越多地被用到數字集成電路設計的驗證中。

動態時序模擬就是通常的仿真,因為不可能產生完備的測試向量,覆蓋門級網表中的每一條路徑。因此在動態時序分析中,無法暴露一些路徑上可能存在的時序問題; 靜態時序分析缺點: 1、無法識別偽路徑 2、不適合異步電路 3、不能驗證功能

5、用VERILOG寫一段代碼,實現消除一個glitch。verilog代碼實現如下:

module digital_filter_(clk_in,rst,host_rst,host_rst_filter);input clk_in;input rst;input host_rst;output host_rst_filter;reg host_rst_d1;reg host_rst_d2;clk_in or negedge rst)beginif(~rst)beginhost_rst_d1 <= 1'b1;host_rst_d2 <= 1'b1;endelsebeginhost_rst_d1 <= host_rst;host_rst_d2 <= host_rst_d1;endendassign host_rst_filter = host_rst_d1 | host_rst_d2;endmodule

verilog代碼實現如下:

module digital_filter_(clk_in,rst,host_rst,host_rst_filter);input clk_in;input rst;input host_rst;output host_rst_filter;reg host_rst_d1;reg host_rst_d2;reg host_rst_d3;clk_in or negedge rst)beginif(~rst)beginhost_rst_d1 <= 1'b1;host_rst_d2 <= 1'b1;host_rst_d3 <= 1'b1;endelsebeginhost_rst_d1 <= host_rst;host_rst_d2 <= host_rst_d1;host_rst_d3 <= host_rst_d2;endendassign host_rst_filter = host_rst_d1 | host_rst_d2 | host_rst_d3;endmodule

責任編輯:haq

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606041 -

測試

+關注

關注

8文章

5382瀏覽量

127073

原文標題:面試中經常遇到的5個FPGA基本概念

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

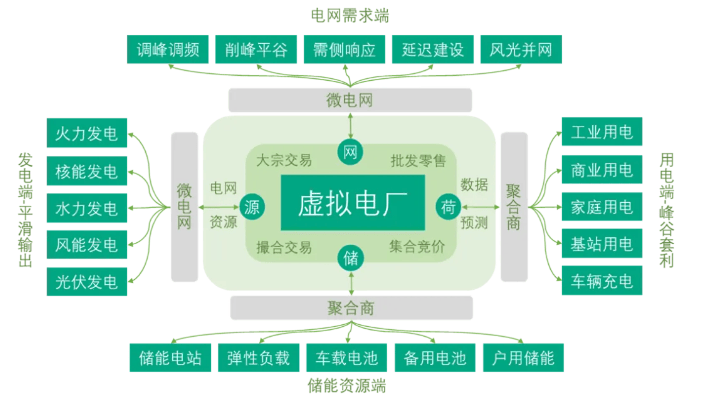

了解虛擬電廠的基本概念

X電容和Y電容的基本概念

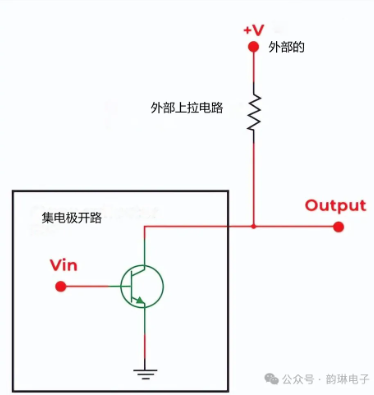

集電極開路的基本概念與原理

5個FPGA基本概念問答

5個FPGA基本概念問答

評論