簡(jiǎn)介

數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)人員—特別是需要在過(guò)程控制或自動(dòng)化系統(tǒng)中進(jìn)行精密測(cè)量的設(shè)計(jì)人員—已經(jīng)習(xí)慣地將他們的系統(tǒng)設(shè)計(jì)為在第一那奎斯特區(qū)域內(nèi)運(yùn)行,這只意味著最大輸入頻率必須被限制在少于一半采樣頻率的范圍內(nèi)。所以,如果你搭建了一個(gè)系統(tǒng),用于捕捉最大頻率為20KHz的音頻,那么你必須在40KHz頻率以上進(jìn)行采樣,以確保捕獲到最高頻分量。

混疊

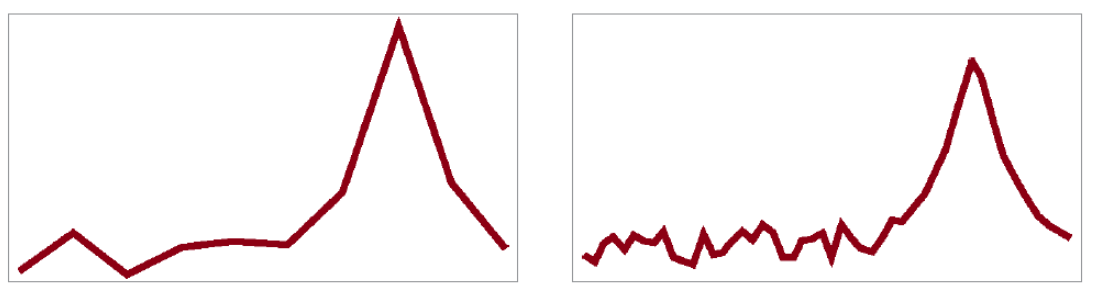

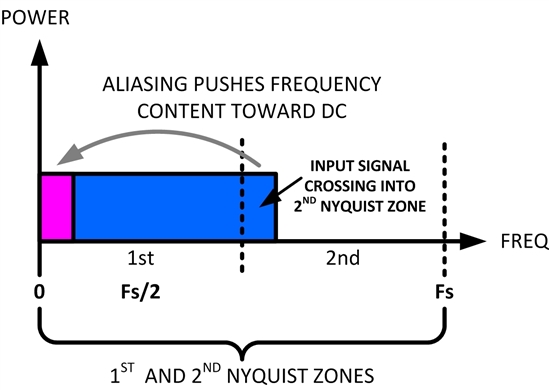

那么,當(dāng)你不遵循這個(gè)規(guī)則時(shí),系統(tǒng)會(huì)發(fā)生什么情況呢?我們假定,你在15kHz上對(duì)模擬信號(hào)進(jìn)行采樣,此時(shí)的頻率分量高達(dá)20kHz—你將最終遇到“混疊”問(wèn)題,或者將上部分量折疊進(jìn)入輸入信號(hào)的工作頻段(請(qǐng)見(jiàn)圖1)。這些混疊信號(hào)將增加到原始信號(hào)上,并且將無(wú)法把已混疊頻率分量與原始信號(hào)區(qū)分開(kāi)來(lái)。

圖1:輸入信號(hào)與第二那奎斯特區(qū)域產(chǎn)生交叉,并被混疊進(jìn)入信號(hào)的工作頻段

在大多數(shù)情況下,捕捉模擬信號(hào),并且不遵守那奎斯特采樣規(guī)則的系統(tǒng)被認(rèn)為是“不良系統(tǒng)”,并且需要在模數(shù)轉(zhuǎn)換器 (ADC) 的輸入前放置一個(gè)抗混疊濾波器,以防止頻率分量交叉進(jìn)入上部那奎斯特區(qū)域。然而,有時(shí)候這是一個(gè)好事情。

在運(yùn)行于超高頻模式下的射頻 (RF) 系統(tǒng)中,處理器(或者一個(gè)現(xiàn)場(chǎng)可編程門(mén)陣列 [FPGA])與數(shù)據(jù)轉(zhuǎn)換器之間移動(dòng)的數(shù)據(jù)量會(huì)是十分可觀的—特別是在系統(tǒng)運(yùn)行在第一那奎斯特區(qū)域內(nèi)更是如此(或者只簡(jiǎn)單稱(chēng)為“第一那奎斯特”)。例如,運(yùn)行在第一那奎斯特區(qū)域內(nèi),輸出頻率為1GHz的數(shù)模轉(zhuǎn)換器 (DAC),為了實(shí)現(xiàn)所需的頻率內(nèi)容,它需要將輸出設(shè)定在2GHz以上。

這對(duì)于ADC也用樣適用—如果RF子系統(tǒng)的輸入的工作頻段在900MHz與1GHz之間,那么ADC必須在2GHz以上采樣,以便將所有的頻率內(nèi)容置于第一那奎斯特區(qū)域內(nèi)。

將那奎斯特混疊變?yōu)閮?yōu)勢(shì)

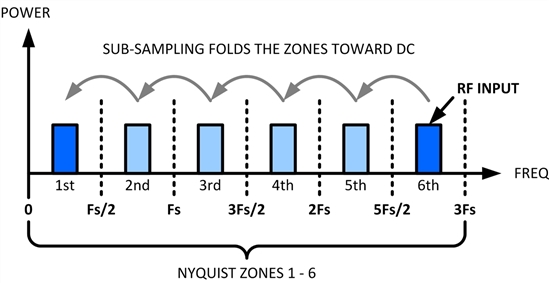

技巧在于將混疊(或者稱(chēng)為頻率折疊)為你所用。通過(guò)對(duì)數(shù)據(jù)轉(zhuǎn)換器進(jìn)行欠采樣,更高頻率內(nèi)容將混疊進(jìn)入所有的較低那奎斯特區(qū)域(請(qǐng)見(jiàn)圖2)。你需要絕對(duì)確保沒(méi)有任何內(nèi)容在較低頻段內(nèi)終止—較低區(qū)域內(nèi)的任何噪聲或頻率分量也將被混疊進(jìn)入第一那奎斯特區(qū)域。好消息是,如果這是一個(gè)第一那奎斯特系統(tǒng),那么數(shù)據(jù)轉(zhuǎn)換器的數(shù)據(jù)速率只是所需RF輸入采樣率的幾分之一。欠采樣極大地減少了被提供給數(shù)字信號(hào)處理器 (DSP) 或FPGA的采樣數(shù)據(jù)速率。

圖2:欠采樣時(shí),較高階頻率分量被折疊進(jìn)入較低那奎斯特區(qū)域

ADC唯一一個(gè)主要要求就是輸入帶寬對(duì)于輸入頻率來(lái)說(shuō)必須是充足的,否則的話,信號(hào)將失真。例如,ADC12J2700可以采樣高達(dá)2.7GSPS,但是它具有一個(gè)大于3GHz的輸入帶寬,從而使得輸入信號(hào)超出最大采樣率,因此將它們折疊進(jìn)入較低區(qū)域。還有一些其它注意事項(xiàng)已經(jīng)超出了本篇博文的范圍,不過(guò),總的說(shuō)來(lái),這個(gè)技巧使你不用對(duì)付極高數(shù)據(jù)速率,以及處理要求。

如果你正在設(shè)計(jì)一個(gè)高性能數(shù)字RF系統(tǒng),你也許想使用這個(gè)方法,連同合適的DAC或ADC來(lái)開(kāi)展設(shè)計(jì)工作。在設(shè)計(jì)正確時(shí),這個(gè)方法可以極大地簡(jiǎn)化這些系統(tǒng)的處理和數(shù)據(jù)流要求。

其它資源

- 閱讀模擬接線 (Analog Wires) 博文,“ADC中的混疊:并不是所有的信號(hào)都與它們看起來(lái)一樣。”

- 在這篇博文中進(jìn)一步了解RF采樣,以及混疊如何成為你的好朋友。

- 在我們的數(shù)據(jù)轉(zhuǎn)換器學(xué)習(xí)中內(nèi)尋找超過(guò)100個(gè)數(shù)據(jù)轉(zhuǎn)換器技術(shù)資源。

- 閱讀TI的白皮書(shū),“為什么在欠采樣夠用的時(shí)候使用過(guò)采樣?”

- 進(jìn)一步了解ADC12J2700。

審核編輯:符乾江

-

數(shù)據(jù)采集

+關(guān)注

關(guān)注

39文章

6251瀏覽量

114042 -

模擬信號(hào)

+關(guān)注

關(guān)注

8文章

1143瀏覽量

52641

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

使用50偶輸出阻抗的波形發(fā)生器產(chǎn)生一個(gè)80Mhz的正弦信號(hào),ADS5474采樣的數(shù)值就出現(xiàn)了飽和削頂?shù)默F(xiàn)象,為什么?

DFT的常見(jiàn)誤區(qū)與解決方案

AD5474如何配成50歐呢?

為什么DAC5674在external 2×的情況下datarange在直流到200HZ之間?

DAC的高次諧波為什么都會(huì)折疊回第一奈奎斯特區(qū)間?

請(qǐng)問(wèn)ADC的采樣率和提供的工作頻率是什么關(guān)系?

路特斯發(fā)布“路遙”超級(jí)混電技術(shù),續(xù)航超1100公里

常見(jiàn)傅里葉變換錯(cuò)誤及解決方法

采樣頻率和信號(hào)頻率之間的關(guān)系

奈奎斯特圖分析怎么判斷穩(wěn)定性啊?

使用單通道ADC+模擬開(kāi)關(guān)結(jié)構(gòu)采樣多路信號(hào)時(shí),ADC采樣率如何選擇呢?

求助,關(guān)于OPA2828設(shè)計(jì)抗混疊濾波器的疑惑求解

DAC39RF10、DAC39RFS10 10.24、20.48GSPS 16位雙通道和單通道多奈奎斯特數(shù)模轉(zhuǎn)換器(DAC)數(shù)據(jù)表

環(huán)路增益的穩(wěn)定性

取樣檢波器使用方法及工作原理

超越第一奈奎斯特區(qū)域,將那奎斯特混疊變?yōu)閮?yōu)勢(shì)

超越第一奈奎斯特區(qū)域,將那奎斯特混疊變?yōu)閮?yōu)勢(shì)

評(píng)論