為了可靠地捕獲高頻信號和快速瞬態脈沖,示波器和有源探頭等寬帶數據采集系統需要高性能模擬前端 (AFE) 信號鏈,該信號鏈必須能夠:

- (至少)支持 1 V PP信號,以確保高信噪比。

- 支持 DC 至 500 MHz 的高輸入阻抗 (Hi-Z),以防止被測設備負載。

- 提供低噪聲和失真以保持高信號保真度。

- 提供高直流精度。

克服這些設計挑戰的一種方法是創建一種基于復合環路的方法,該方法將低頻和高頻信號鏈交錯,以獲得直流精度和寬大的信號帶寬。

使用 BUF802 實現 ASIC 級性能

|

在視頻“ BUF802:寬帶、高輸入阻抗 JFET 緩沖器”中了解如何更可靠地捕獲寬帶采集系統中的高頻信號和快速瞬態脈沖。 |

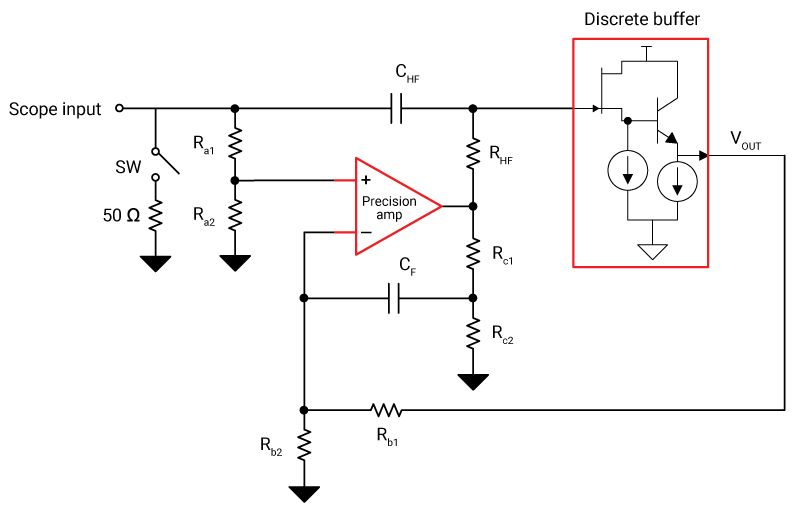

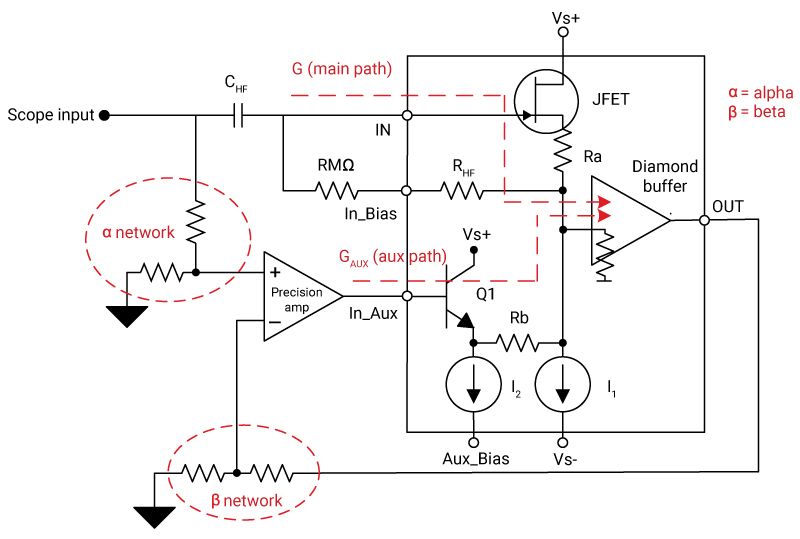

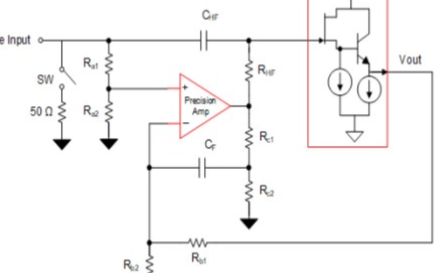

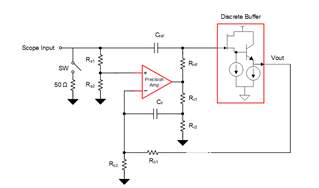

鑒于實現滿足系統要求的基于復合環路的電路的復雜性,工程師通常必須設計定制的專用集成電路 (ASIC) 或使用多個分立元件,如圖 1 所示。這兩種選擇都有缺點,包括需要 ASIC 的專業知識和額外的設計復雜性。這兩種方法在性能和成本方面也有權衡:離散實現比 ASIC 便宜,但無法與它們的性能水平相匹配。

圖 1:帶有精密放大器 AFE 的分立緩沖器復合環路

在本文中,我將探討離散緩沖器復合環路實現與使用BUF802 Hi-Z 緩沖器的單芯片實現的設計挑戰。

離散緩沖器復合循環架構

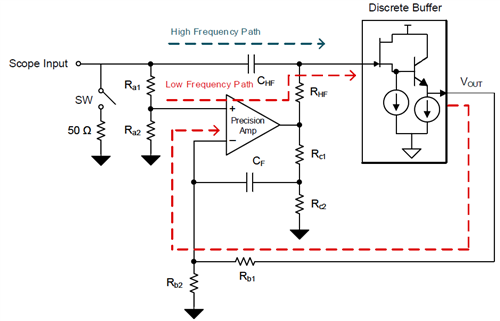

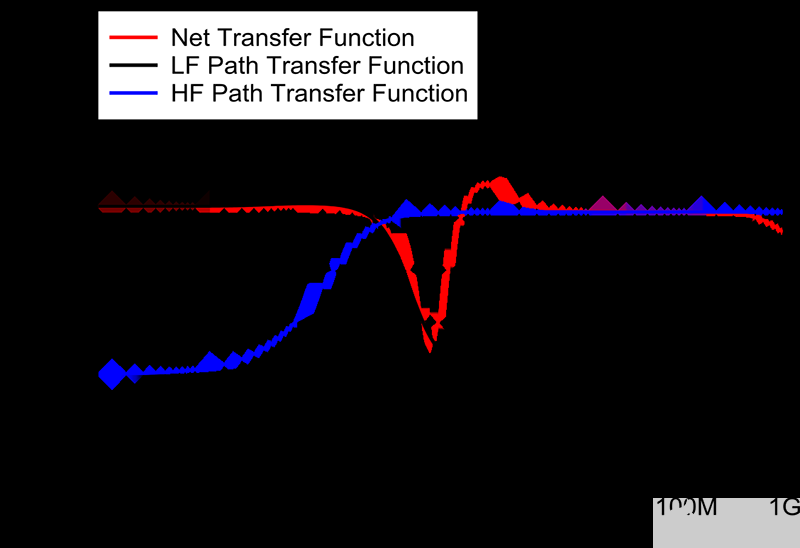

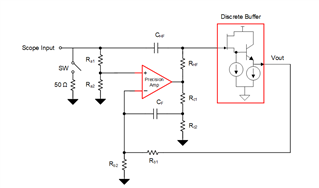

圖 1 中 Hi-Z AFE 的分立式實現使用精密放大器和基于分立結場效應晶體管 (JFET) 的源極跟隨器電路,配置在復合環路中。環路將輸入信號分成低頻和高頻分量,通過兩個不同的電路(傳遞函數)將這兩個分量帶到輸出端,并將它們重新組合以再現凈輸出信號,如圖 2 所示。

圖 2:離散復合環路低頻和高頻路徑

低頻路徑為凈傳遞函數提供了良好的直流精度,而基于 JFET 源極跟隨器的高頻路徑使凈傳遞函數具有寬大的信號帶寬,以及低噪聲和低失真。圖 2 所示電路的主要挑戰之一是實現兩條路徑的平滑交錯,以確保平坦的頻率響應。兩條路徑的傳遞函數的任何不匹配都會導致凈傳遞函數頻率響應的不連續性,從而導致信號保真度的損失。

復合循環架構的目標

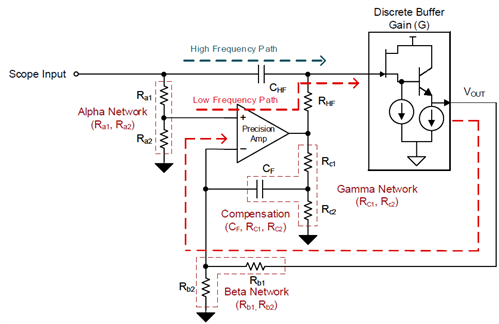

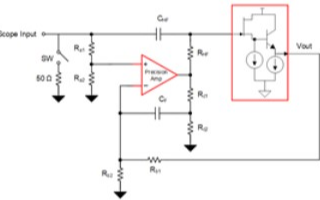

在直流或低頻時,C HF(高頻電容器)開路,電壓輸出(V OUT)由低頻路徑中的精密放大器控制。阿爾法和貝塔電阻網絡的比率控制直流或低頻增益。

在高頻下,C HF短路,精密放大器在有限的增益帶寬積下耗盡帶寬。分立緩沖器用作 JFET 源極,負正負射極跟隨器決定 V OUT。圖 3 中稱為增益 (G) 的離散緩沖級決定了高頻路徑增益。

圖 3:離散緩沖器復合循環架構

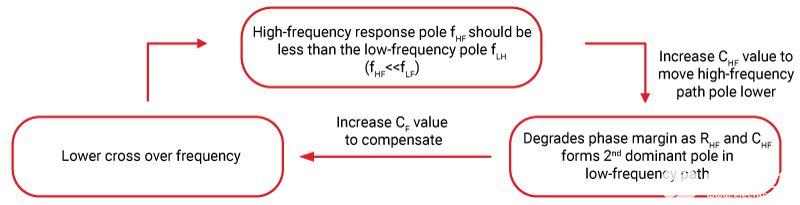

在中頻,由于低頻和高頻路徑都決定了輸出,因此仔細調整各個增益以及極點和零點的相互作用對于確保平坦的頻率響應非常重要。實現中頻增益均衡具有挑戰性,因為相同的組件 C HF和 R HF(高頻電阻)決定了低頻和高頻路徑的極點,如圖 4 所示。

圖 4:離散緩沖器頻率響應

復合環路應具有平坦的頻率響應和高交叉頻率區域,以實現低 1/f 噪聲和快速過驅動恢復。

離散實現的復雜性

鑒于低頻和高頻路徑的相互依賴性,如圖 5 所示,C HF和 C F(補償電容器)的值以數十納法為單位,以實現平坦的頻率響應。但這些值會導致數十至數百赫茲的交叉頻率范圍,這會限制信號鏈的直流噪聲性能。

圖 5:低頻和高頻路徑的相互依賴性

離散實現復合環路的另一個挑戰是精密放大器開環增益的極點和 R HF和 C HF的電阻電容網絡的極點對低頻路徑中的雙極點網絡有貢獻,從而導致在不穩定。在精密放大器上實施一個額外的網絡(在圖 3 中標記為伽馬網絡)將補償這種不穩定性,但需要調整以實現更平坦的頻率響應,進一步增加了創建平滑頻率響應的復雜性。操作范圍。

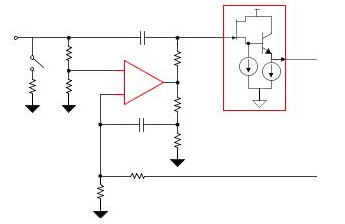

使用 BUF802 實現復合循環

由于實現分立復合環路的主要限制之一是低頻和高頻路徑之間的相互依賴性以及需要額外的伽馬網絡進行補償,因此 BUF802 在器件內部具有輔助路徑。將精密放大器的輸出連接到輔助路徑會創建一個復合環路,同時確保低頻和高頻路徑之間的隔離。隔離不同的頻率路徑會創建更高的交叉頻率區域并消除伽馬網絡和補償電路。低頻和高頻信號分量在 BUF802 內部重新組合,并在 OUT 引腳處再現,如圖 6 所示。

圖 6:具有內部 BUF802 的復合環路精密放大器

結論

諸如 BUF802 之類的集成 Hi-Z 緩沖器有助于解決基于復合循環實現的復雜挑戰。BUF802 的輸入/輸出鉗位等集成保護功能有助于保護信號鏈中的后續階段,減少過驅動恢復時間和輸入電容,并提高系統可靠性。

在為當今的應用考慮 AFE 時,您還必須牢記未來的測量需求,這通常需要額外的帶寬。這種帶寬可以大大提高測量精度,并確保系統設計投資與未來的測試要求保持相關。

審核編輯:符乾江

-

集成電路

+關注

關注

5392文章

11622瀏覽量

363177 -

緩沖器

+關注

關注

6文章

1930瀏覽量

45645 -

模擬前端

+關注

關注

3文章

196瀏覽量

29841

發布評論請先 登錄

相關推薦

如何使用 Hi-Z 緩沖器簡化AFE設計

引導時的兩用配置引腳保持在hi-z嗎?

單輸入邏輯門(數字緩沖器)這些特性你知道嗎?

使用Hi-Z緩沖器簡化AFE設計的教程

有什么辦法可以在reset的時候把DP&DN的狀態改成Hi-Z嗎?

緩沖器,緩沖器是什么?

利用Hi-Z緩沖器緩沖簡化高性能模擬前端信號鏈設計

什么是時鐘緩沖器(Buffer)?時鐘緩沖器(Buffer)參數解析

如何使用Hi-Z緩沖器簡化AFE設計

使用Hi-Z緩沖器簡化模擬前端

使用Hi-Z緩沖器簡化模擬前端

評論