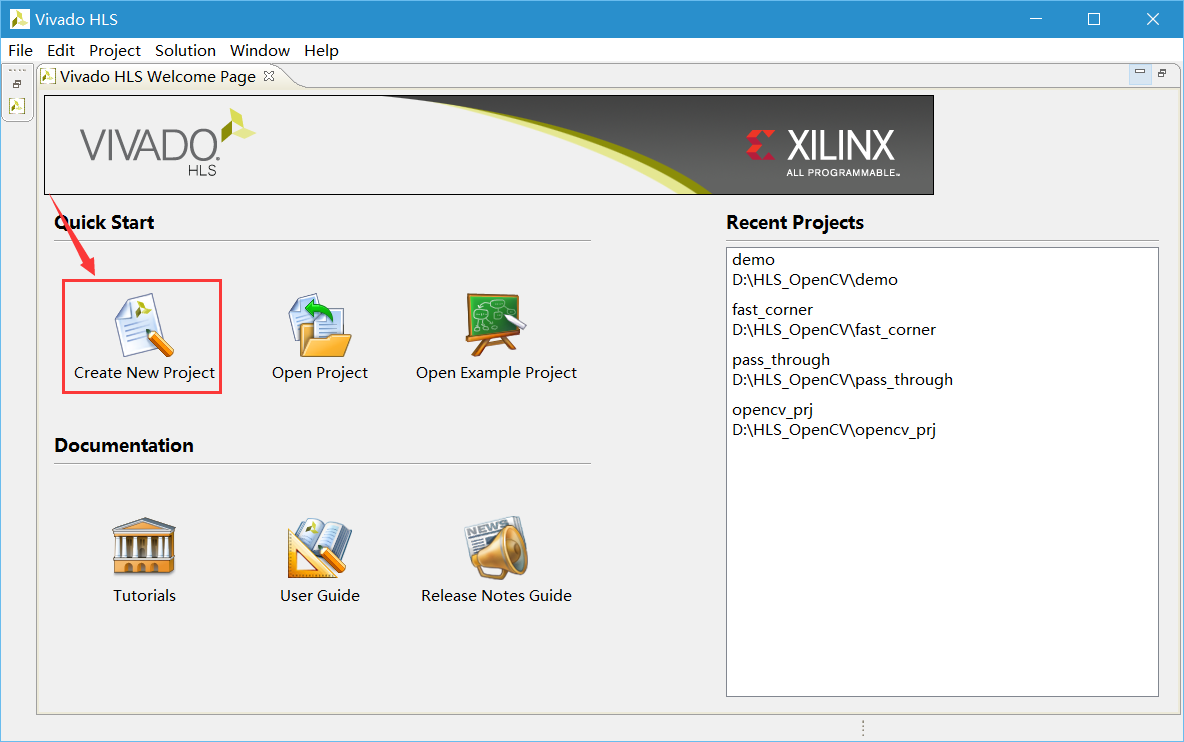

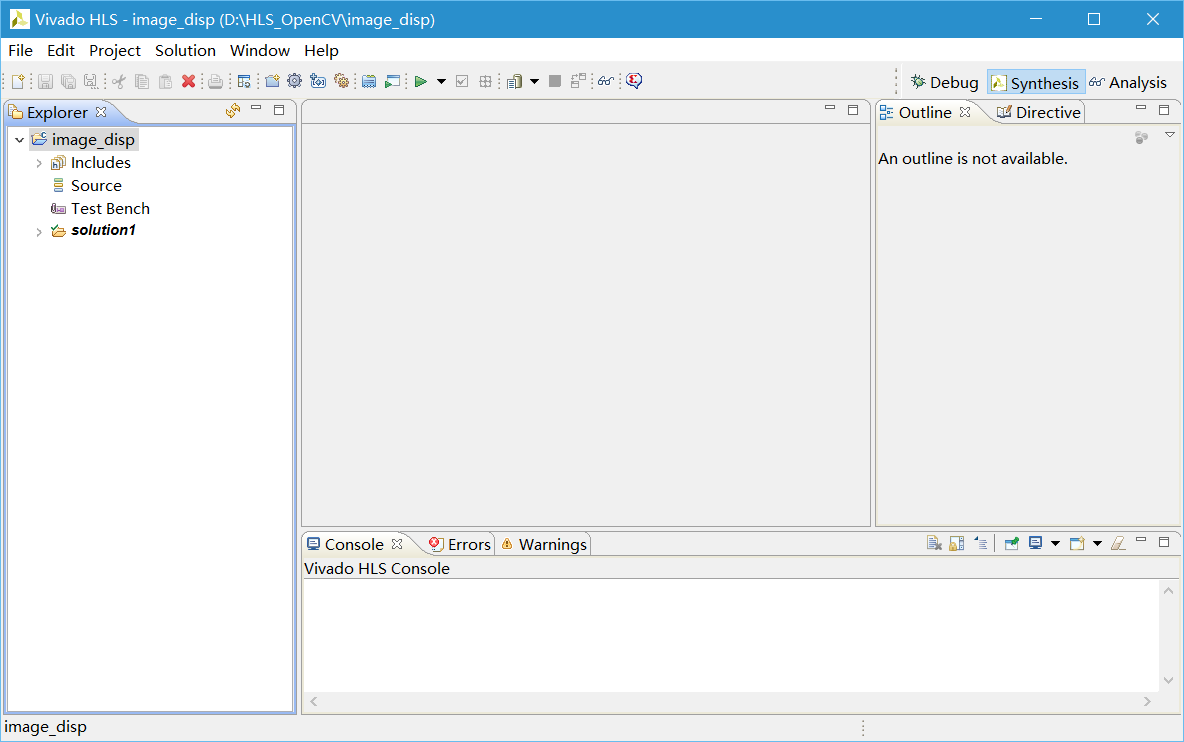

先從運(yùn)行一個(gè)創(chuàng)建一個(gè)項(xiàng)目開(kāi)始吧。

首先打開(kāi)Vivado設(shè)計(jì)套件Vivado HLS 2015.4;

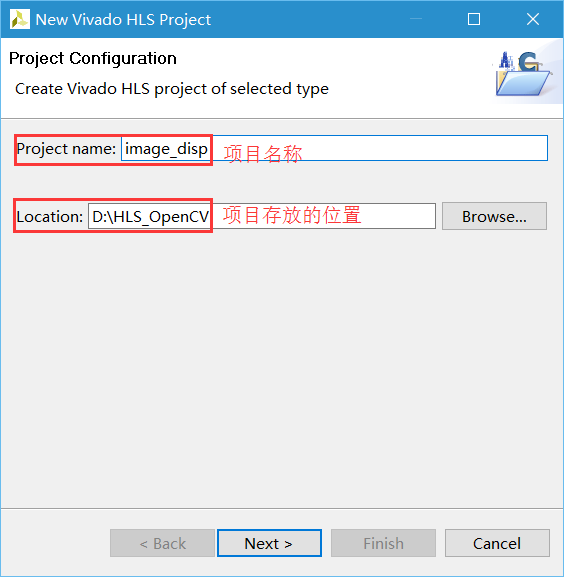

輸入項(xiàng)目的名稱和存放的位置;

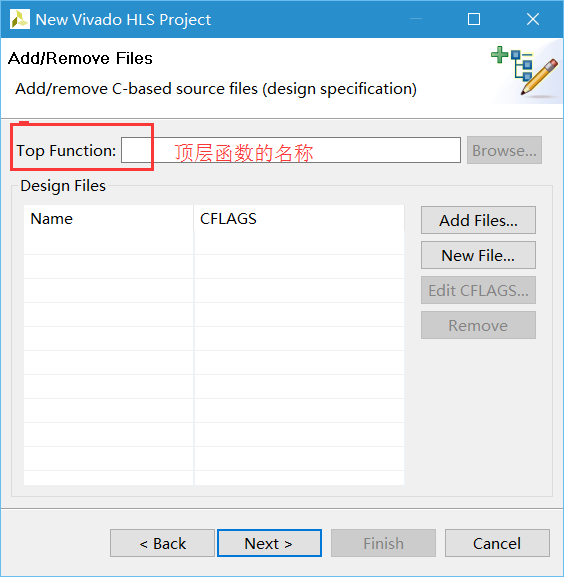

點(diǎn)擊下一步,輸入設(shè)計(jì)頂層函數(shù)的名稱,接著下一步;

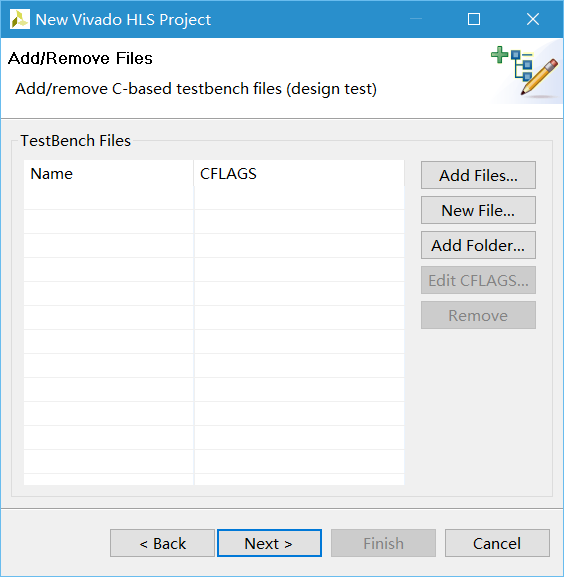

暫時(shí)不需要填寫(xiě),直接下一步;

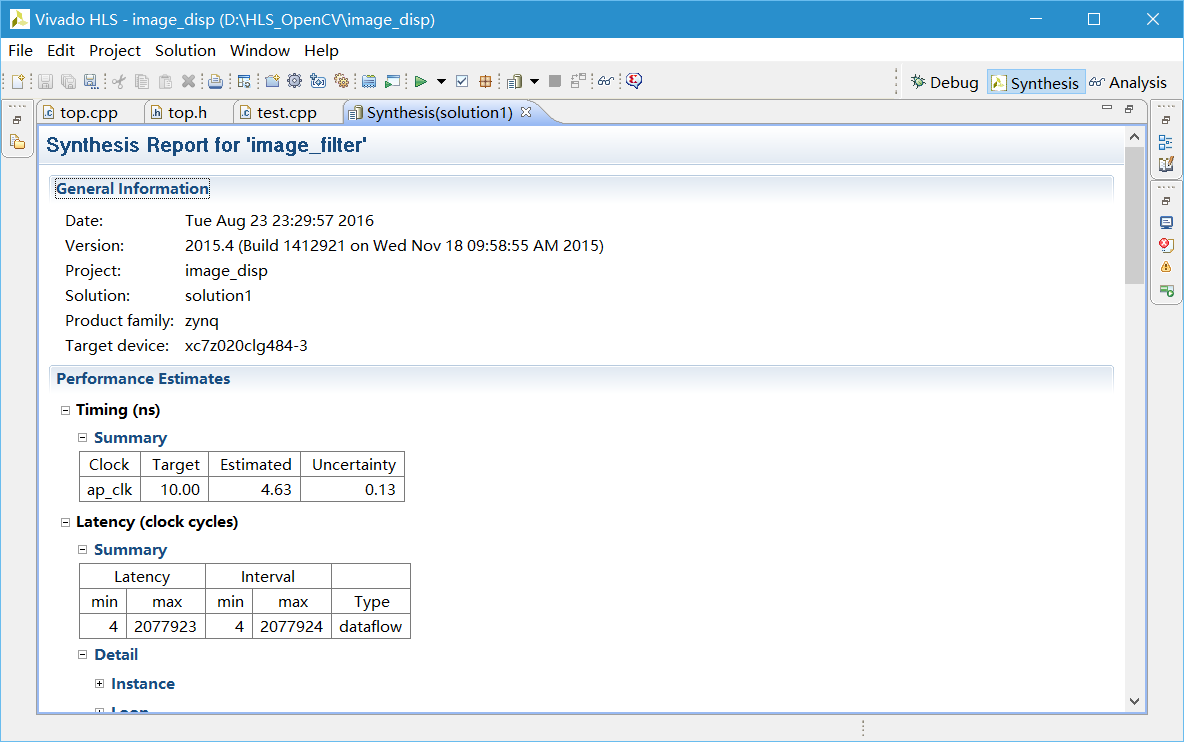

解決方案的名字默認(rèn) (solution1)就好, 時(shí)鐘周期根據(jù)需要自己設(shè),這里我設(shè)(10 ns), 時(shí)鐘的不確定性一般為12.5%,接著選擇器件,最后“finish”。

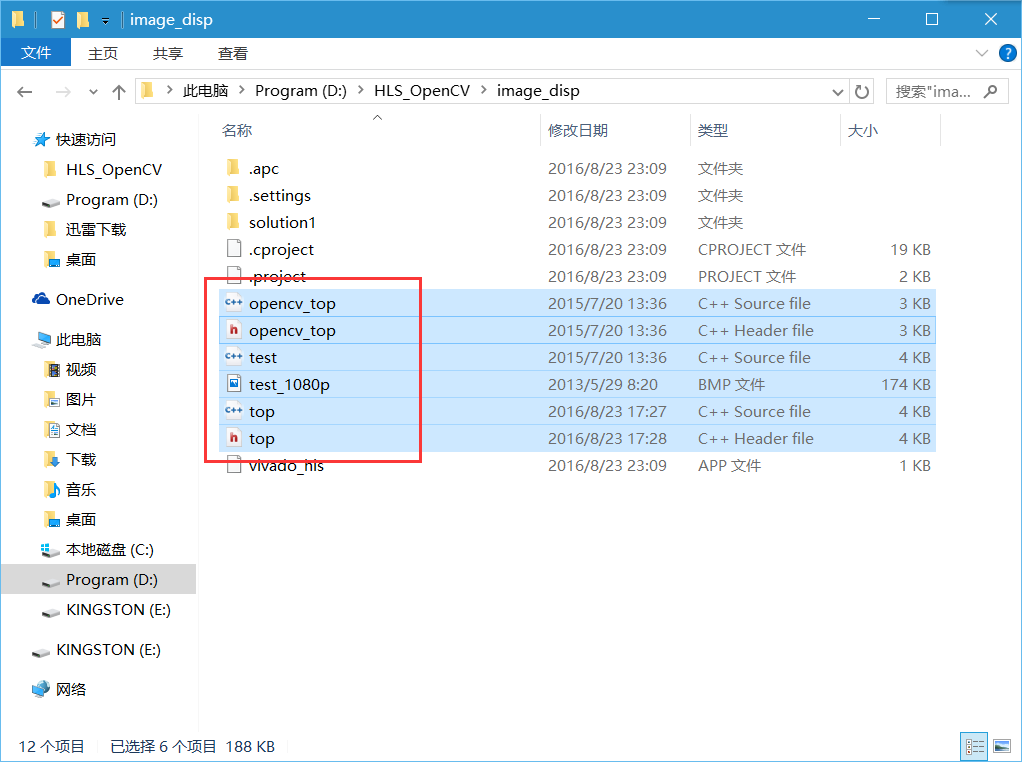

將該例程的設(shè)計(jì)文件和testbench全部復(fù)制到剛才創(chuàng)建的項(xiàng)目目錄下:

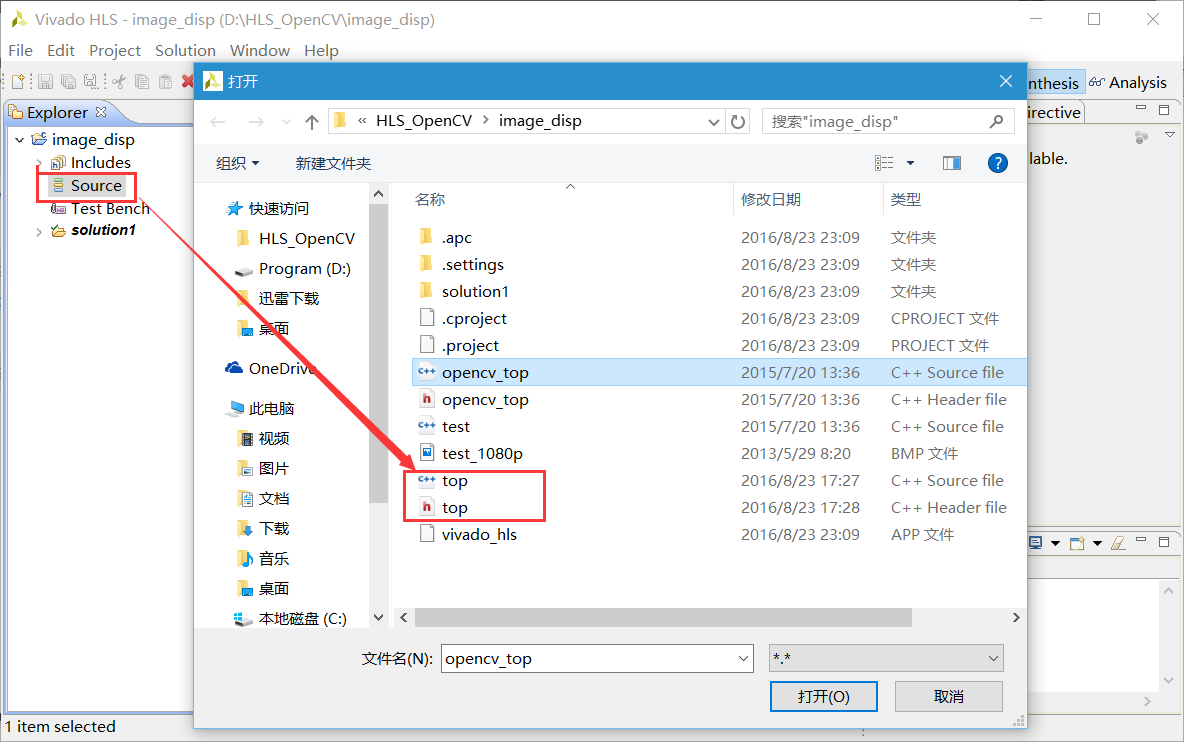

在設(shè)計(jì)資源窗口右擊“Source”,添加設(shè)計(jì)文件;

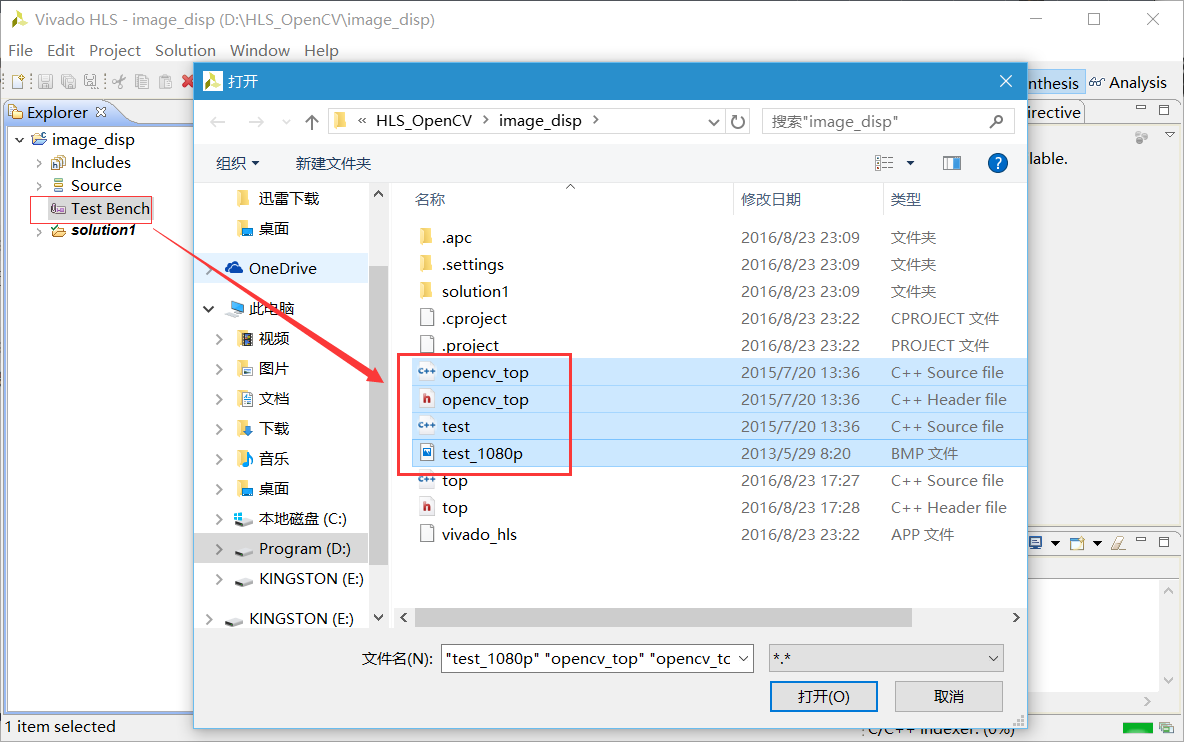

再接著右擊“Test Bench”,添加文件;

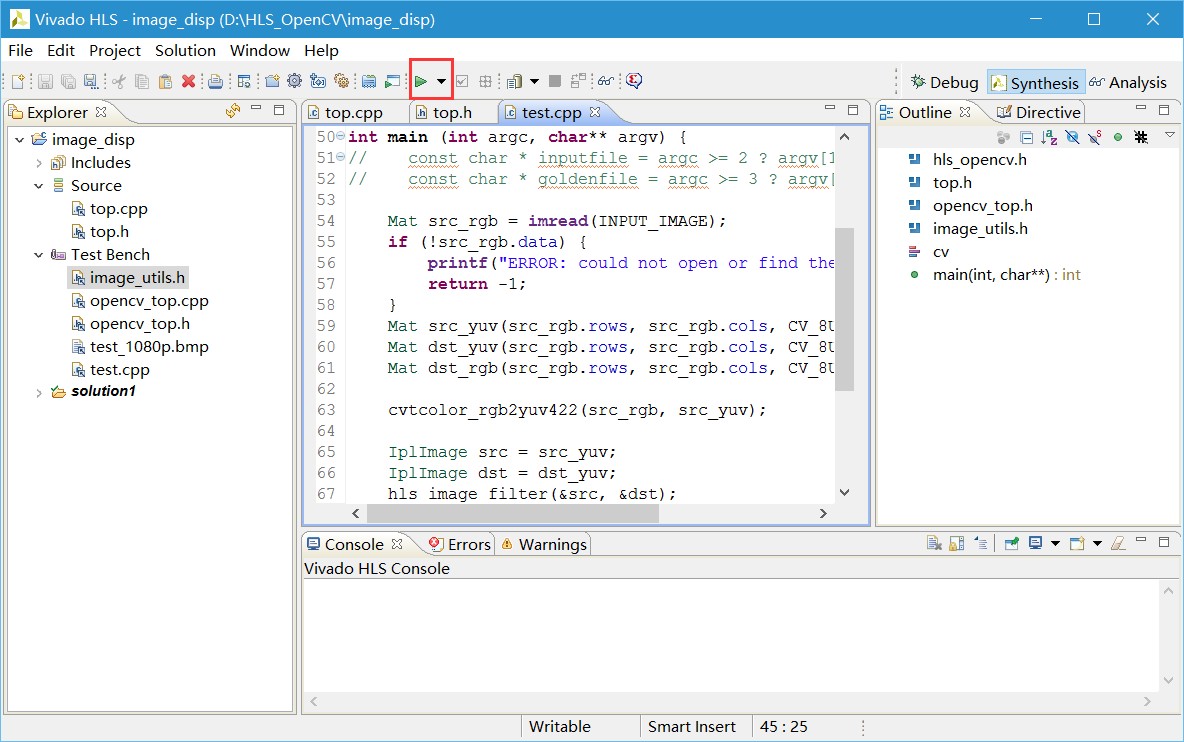

至此,項(xiàng)目建設(shè)完成。接著進(jìn)行綜合仿真,驗(yàn)證設(shè)計(jì)。 點(diǎn)擊“Run C Snthry”。

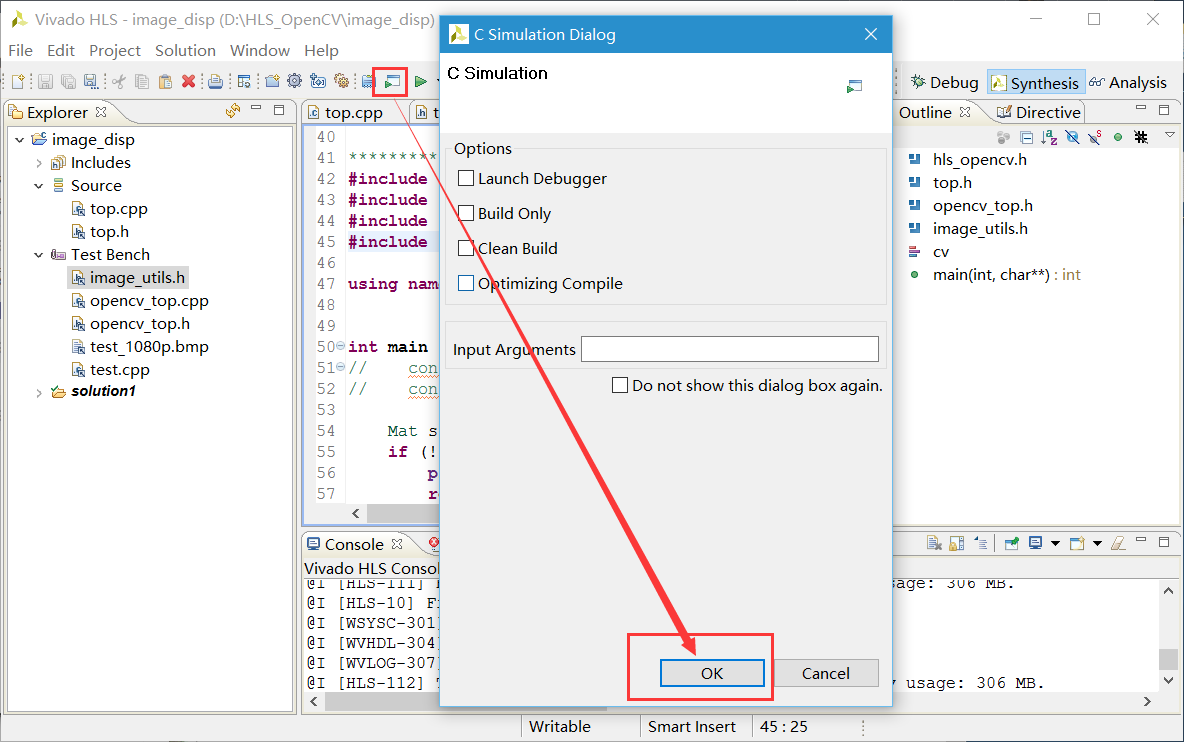

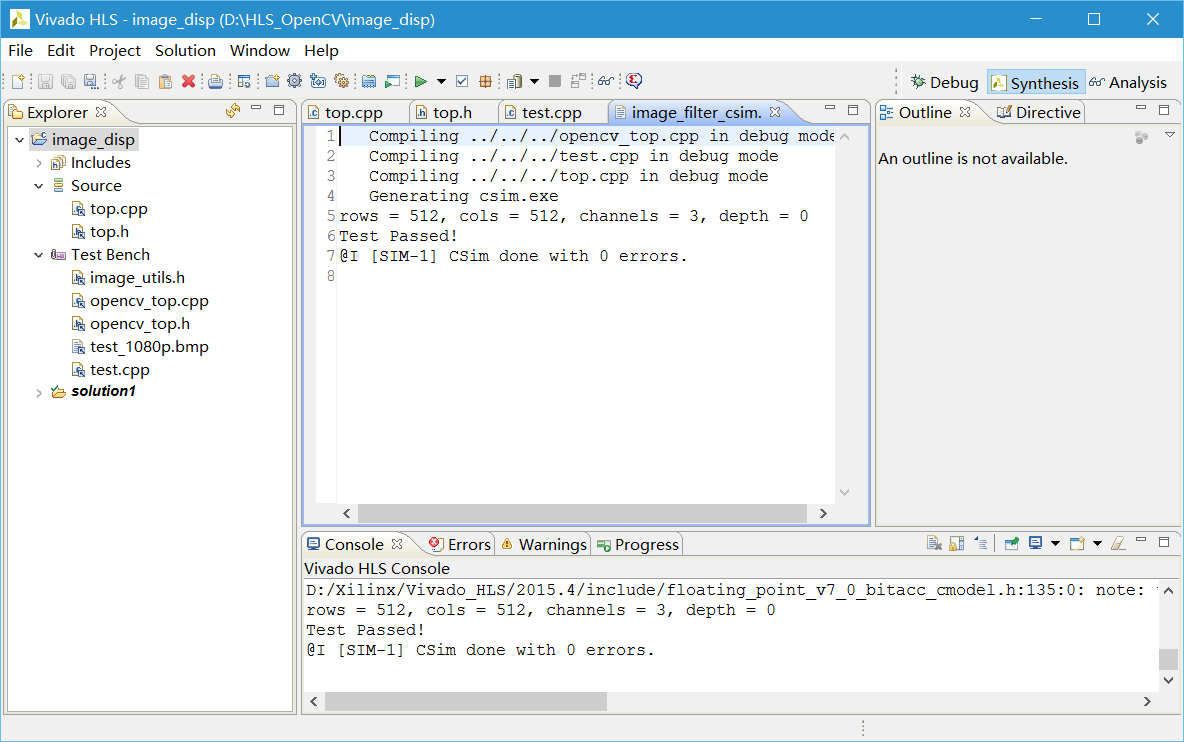

點(diǎn)擊“Run C Simulation”,接著點(diǎn)擊“OK”;

至此,此項(xiàng)目在沒(méi)有硬件調(diào)試的前提下算是成功運(yùn)行了。

審核編輯:湯梓紅

-

HDL

+關(guān)注

關(guān)注

8文章

328瀏覽量

47468 -

模型

+關(guān)注

關(guān)注

1文章

3313瀏覽量

49228 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66892

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

科技云報(bào)到:從大模型到云端,“AI+云計(jì)算”還能講出什么新故事

從Level1 Model到Level3 Modle來(lái)感受器件模型是如何開(kāi)發(fā)的

助力AIoT應(yīng)用:在米爾FPGA開(kāi)發(fā)板上實(shí)現(xiàn)Tiny YOLO V4

Vivado使用小技巧

Vivado 2024.1版本的新特性(2)

優(yōu)化 FPGA HLS 設(shè)計(jì)

一種在HLS中插入HDL代碼的方式

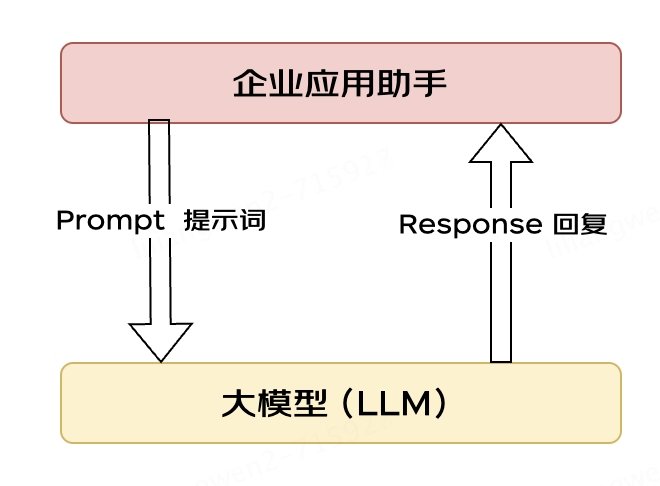

大模型應(yīng)用之路:從提示詞到通用人工智能(AGI)

FPGA設(shè)計(jì)中 Verilog HDL實(shí)現(xiàn)基本的圖像濾波處理仿真

簡(jiǎn)談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

Verilog到VHDL轉(zhuǎn)換的經(jīng)驗(yàn)與技巧總結(jié)

Vivado HLS從HDL到模型和C的描述

Vivado HLS從HDL到模型和C的描述

評(píng)論