實驗任務:

將輸入數據(data_in)存入ddr,然后讀出,驗證輸入輸出數據是否相等。

一、前言

接上一篇(3)MIG的使用教程

MIG配置如下:

1. 系統時鐘sys_clk = 200Mhz

2. 系統復位sys_rst 低有效

3. 模式:4:1

4. 位寬: 16bit

注:由于選擇的DDR3的突然長度為8,所以mig的數據位寬=16*8=128bit,對應到代碼即app_wdf_data[127:0] , app_rd_data[127:0]。

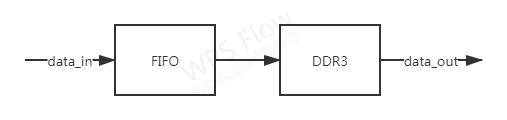

二、系統方案

2.1方案設計

實驗任務:

將數據(data_in),存入ddr,然后讀出,驗證輸入輸出數據是否相等。

實驗目的:

初步掌握DDR讀寫設計。

為什么要先過FIFO再寫入DDR?

因為DDR接口對用戶而言并不是一直有效,只有等DDR“有效”時(app_rdy = 1 && app_wdf_rdy = 1),才能進行寫入。

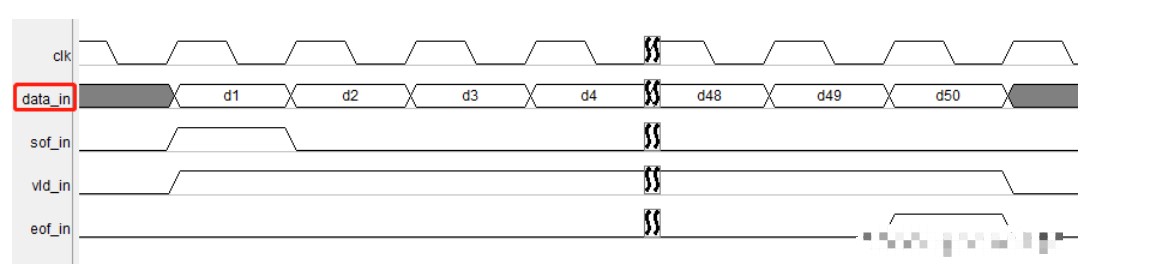

2.1.1輸入接口時序圖

輸入數據為1-50共50個數據,以vld_in信號表征輸入數據有效。

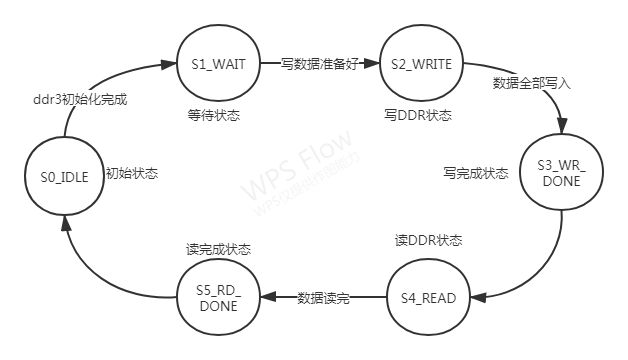

2.2狀態機設計

2.2.1獨熱碼localparam S0_IDLE = 6'b000001; //初始化狀態,DDR初始化成功就跳轉S1

localparam S1_WAIT = 6'b000010; //等待狀態,等FIFO緩存好數據就跳轉S2

localparam S2_WRITE = 6'b000100; //寫DDR狀態,FIFO數據寫完就跳轉到S3

localparam S3_WR_DONE = 6'b001000; //寫完成狀態,給出讀地址初始值就跳到S4

localparam S4_READ = 6'b010000; //讀DDR狀態,讀到相應長度的數量就跳到S5

localparam S5_RD_DONE = 6'b100000; //讀完成狀態,跳回IDLE

2.2.2狀態機流程圖

2.2.3三段式狀態機

always @(posedge sys_clk or posedge sys_rst)begin

if(sys_rst == 1'b1)

current_state else

current_state end

always @(*)begin

case(current_state)

S0_IDLE :

if(init_calib_complete == 1'b1)

next_state else

next_state S1_WAIT :

if(eof == 1'b1)

next_state else

next_state S2_WRITE :

if(ififo_empty == 1'b1)

next_state else

next_state S3_WR_DONE :

next_state S4_READ :

if(cnt_read == cnt_length)

next_state else

next_state S5_RD_DONE :

next_state default :

next_state endcase

end

always @(posedge sys_clk or posedge sys_rst)begin

if(sys_rst == 1'b1)begin

cnt_length cnt_read cnt_write app_addr end

else case(current_state)

S0_IDLE : ;

S1_WAIT : ;

S2_WRITE:

if(app_rdy && app_wdf_rdy && app_en)begin

app_addr cnt_write end

else begin

app_addr cnt_write end

S3_WR_DONE :begin

cnt_length app_addr end

S4_READ :

if(app_rdy && app_en)begin

app_addr cnt_read end

else begin

app_addr cnt_read end

S5_RD_DONE :begin

cnt_length cnt_read cnt_write end

default : ;

endcase

end

代碼很簡單,對應流程圖跳轉,此處不再啰嗦 。

2.3app接口設計

assign app_wdf_mask = 16'b0; //掩碼置0,表示傳輸的全部為有效數據

assign ififo_rden = (current_state == S2_WRITE)&& app_rdy && app_wdf_rdy;

assign app_en = ((current_state == S2_WRITE)&&(ififo_vld)) || (current_state == S4_READ);

assign app_cmd = (current_state == S4_READ) ? 3'b001 : 3'b000;

assign app_wdf_wren = ififo_vld;

assign app_wdf_end = ififo_vld;

assign app_wdf_data = ififo_rdata;

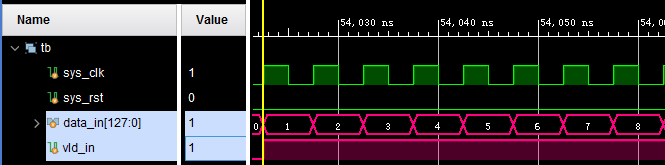

三、仿真結果

因為DDR仿真,需要用到ddr3_model和其他文件,單開一篇來講解。

這里只看仿真結果。

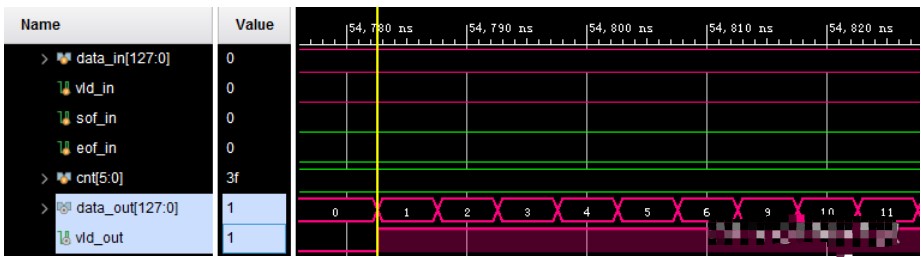

輸入:

輸出:

輸入數據: 1-50;

輸出數據: 1-50;

DDR讀寫測試成功!

審核編輯:湯梓紅

-

FPGA

+關注

關注

1630文章

21797瀏覽量

606016 -

DDR3

+關注

關注

2文章

276瀏覽量

42389 -

Xilinx

+關注

關注

71文章

2171瀏覽量

122142

發布評論請先 登錄

相關推薦

DDR3、DDR4、DDR5的性能對比

如何選擇DDR內存條 DDR3與DDR4內存區別

基于FPGA的DDR3多端口讀寫存儲管理設計

三星和SK海力士下半年停產DDR3內存

SK海力士、三星電子陸續停產DDR3內存,帶動市場價格上行

華邦傾力挺進DDR3市場,抓住轉單商機

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據表

完整DDR,DDR2,DDR3 和LPDDR3 存儲器電源解決方案同步降壓控制器數據表

完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表

適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩壓器數據表

具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數據表

具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內存電源解決方案數據表

完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表

Xilinx FPGA平臺DDR3設計保姆式教程(四)

Xilinx FPGA平臺DDR3設計保姆式教程(四)

評論