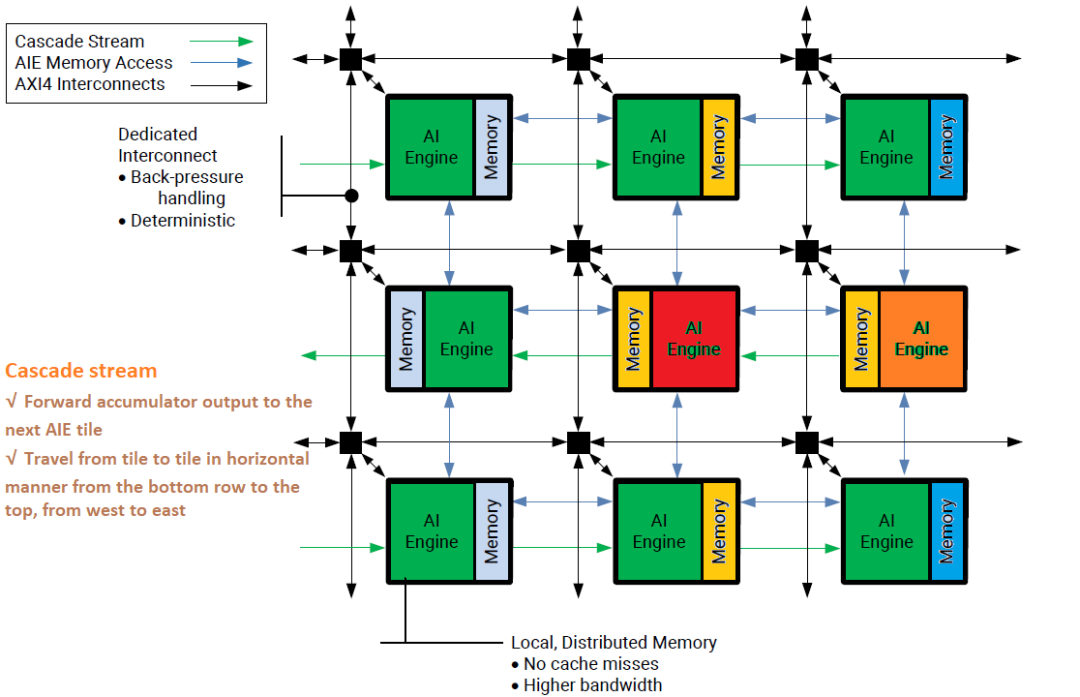

AI Engine陣列是由一系列的AI EngineTile構成。每個AI Engine Tile包含一個AI Engine,一個存儲單元和一個互連單元,如下圖所示。可以看到相鄰兩行AI Engine Tile的存儲單元與AI Engine的位置正好相反。

存儲單元可被東西南北四個方向的AI Engine共享,當然這也跟AI Engine的位置有關。例如圖中紅色AI Engine可訪問與之相鄰的4個存儲單元(黃色標記)。最右側的橙色AI Engine就只能訪問三個存儲單元,因為其位于邊界。每個方向的存儲單元都有對應的存儲器接口,AI Engine在訪問相應方向的存儲單元時正是通過這些接口實現的。每次訪問的最大位寬為256。

水平方向相鄰的兩個AI Engine之間還有級聯端口,用于傳送累加器的結果。仍以上圖為例,最下方的一行AI Engine可從左至右級聯,倒數第二行的AI Engine可從右至左級聯。同時,最下方級聯至最右側時可與倒數第二行最右側的AI Engine級聯,形成蛇形級聯。

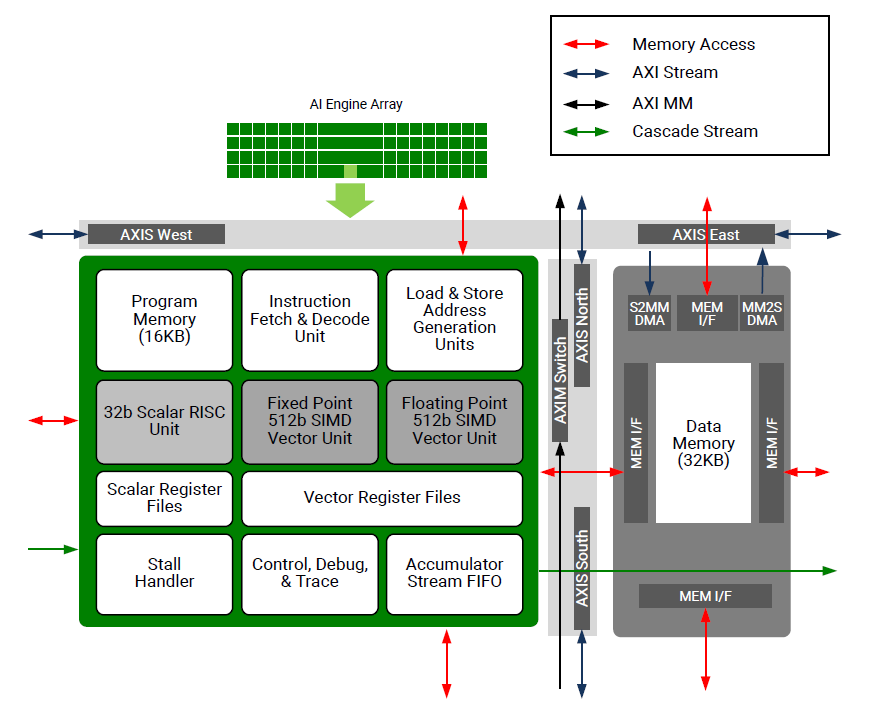

互連單元采用AIX4 Stream接口將數據在東西南北四個方向傳送。同時每個AI Engine Tile的存儲單元都包含一個DMA。每個DMA由一個獨立的S2MM和一個獨立的MM2S構成。前者用于將數據從Stream上取下來寫入到存儲單元,后者用于將存儲單元的數據上傳到Stream,如下圖所示。

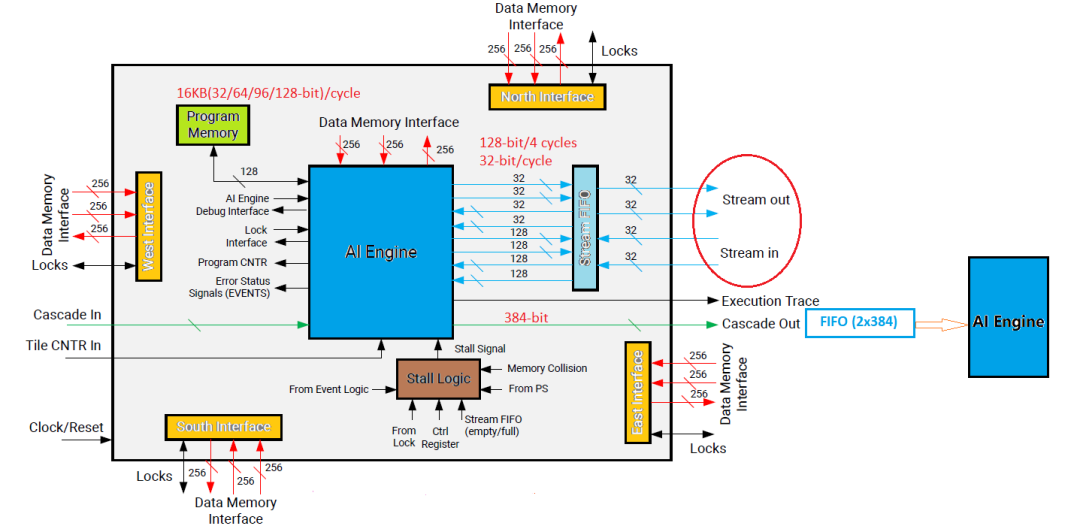

再看AI Engine自身,如下圖所示。每個AIEngine包含一個程序存儲單元,大小為16KB,有2個Stream輸入接口和2個Stream輸出接口,均為32位。因此,每個時鐘周期可從一個Stream上獲取一個32位數據或每4個時鐘周期可從一個Stream上獲取一個128位數據。每個AI Engine還有4個存儲單元訪問接口,但每個時鐘周期只可以有兩次讀操作和一次寫操作。

至此,我們可以看到AI Engine有三種數據源:存儲單元、AXI4-Stream和級聯接口。因此,編程時需要充分了解AIE的數據訪問能力:2個32位AXI4-Stream輸入,2個32位AXI4-Stream輸出,1個384位級聯Stream輸入,1個384位級聯Stream輸出,2個256位讀操作和1個256位寫操作。

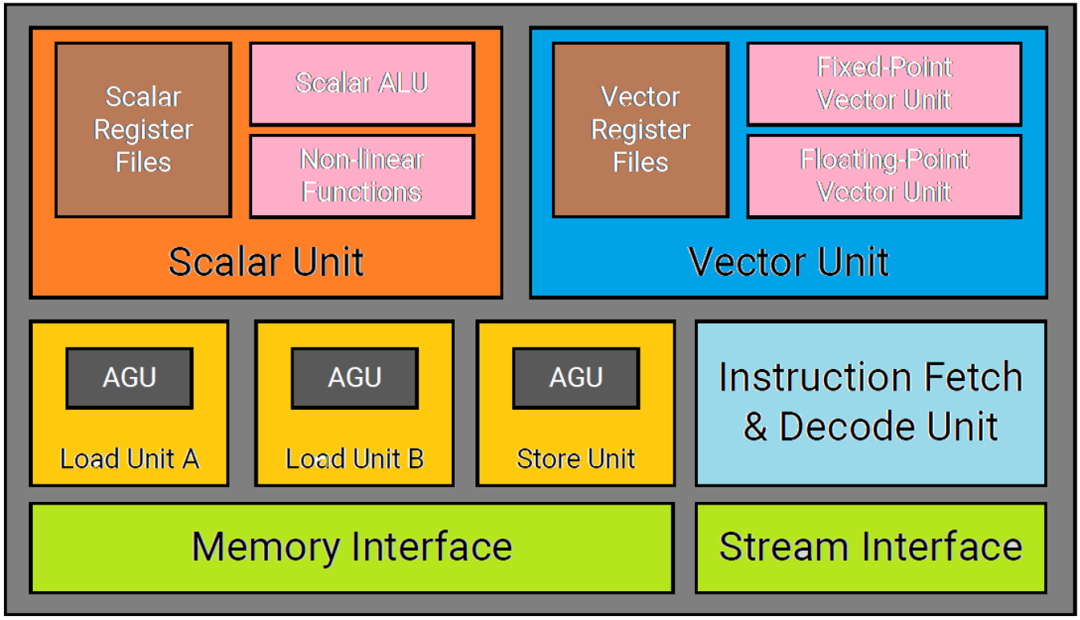

AI Engine本身是一個高度優化的SIMD(Single Instruction Multiple Data)& VLIW(Very Long Instruction Word)處理器,包含1個標量處理單元,1個向量處理單元,2個讀地址發生器,1個寫地址發生器,1個取指和譯碼單元,如下圖所示。正因為有2個讀地址發送器和1個寫地址發生器,所以每次訪問可實現2個256讀操作和1個256寫操作。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19407瀏覽量

231182 -

AI

+關注

關注

87文章

31513瀏覽量

270328

原文標題:AIE(12)—AI Engine架構概覽

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AI Engine架構的構成及應用優勢

AI Engine架構的構成及應用優勢

評論