“ 此小節(jié)中介紹Verilog HDL中提供的常用預(yù)編譯命令:`define ;`timescale ;`include ;`ifdef 、`elsif、`endif 。”

01、時間尺度`timescale

`timescale命令用于在文件中指明時間單位和時間精度,通常在對文件進行仿真時體現(xiàn)。EDA工具可以支持在一個設(shè)計中可根據(jù)仿真需要在不同模塊里面指定不同的時間單位。如模塊A仿真的時間單位為皮秒(ps),模塊B仿真的時間單位為納秒(ns)。使用`timescale命令語句格式如下:

`timescale 《時間單位》 / 《時間精度》

使用時注意《時間單位》和《時間精度》必須是整數(shù),且時間精度不能大于時間單位值。

其中時間單位是定義仿真時間和延遲時間的基準(zhǔn)單位;時間精度是定義模塊仿真時間的精確程度的,又被稱為取整精度(在仿真前,被用來對延遲的時間值進行取整操作,例程中會對此進行介紹)。如果在同一個設(shè)計中,出現(xiàn)多個`timescale命令,工具會采用最小的時間精度值來決定仿真的時間單位。

下面舉例說明`timescale用法。

`timescale 1ns / 1ps:此命令已定義模塊中的時間單位為1ns,即仿真模塊中所有的延遲時間單位都是1ns的整數(shù)倍;定義了模塊的時間精度為1ps,即仿真模塊中延遲單位可以指定到小數(shù)點后3位,小數(shù)超過3位會進行取小數(shù)點后3位的操作。

02、宏定義`define

在設(shè)計中,為了提高程序可讀性和簡化程序描述,可以使用指定的標(biāo)識符來代替一個長的字符串,或者使用一個簡單的名字來代替沒有含義的數(shù)字或者符號,此時需使用到宏定義命令`define。它的使用形式如下:

`define signal(宏名) string(宏內(nèi)容)

在設(shè)計中進行了以上聲明后,在與編譯處理時,在此命令后程序中所有的signal都替換成string,此過程稱為“宏展開”。具體使用方法如下:

例1 :`define LENGTH 16

reg[ `LENGTH–1 : 0 ] writedata;//即定義reg[15:0]writedata;

例2 :`define expression a+b+c

assign data = `expression + d ; // 經(jīng)宏展開之后assign //add_data = a+b+c+d;

例3 :`define A a+b

`define B c+`A

assign data = `B ; // 即data = c + a + b;

03、文件包含指令`includ

和C語言中聲明頭文件很類似。其一般形式為:`include “文件名”

例:

文件para.v中有一個宏定義 `defineA 2+3

在test.v文件中可以直接調(diào)用

`timescale1ns/1ps`include"para.v"`include"para2.v"module test(input wire clk,outputreg[7:0]result);always@(posedge clk)beginresult<=?`A+10;endendmodule

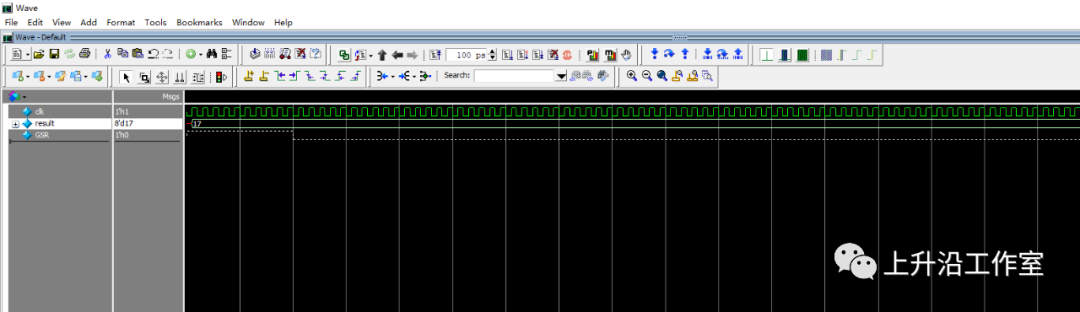

仿真結(jié)果如下:

關(guān)于“文件包含的幾點說明”:

-

一個`include只能指定一個包含文件;

-

`include中的文件名可以是相對路徑,也可以是絕對路徑(ISE中調(diào)用Modelsim仿真的時候得用絕對路徑,否則Modelsim會報錯);

-

如果文件1包含文件2,而文件2要用到文件3的內(nèi)容,那么在文件1中用`include命令分別包含文件2和文件3(文件3在文件2的前面)

例:

para.v中: `define A 2+3

para2.v中 : `define B `A+2

test.v中:

`timescale 1ns / 1ps`include"para.v"`include " para2.v"module test(input wire clk,output reg [7:0] result);always@(posedge clk)beginresult<=?`B+10;endendmodule

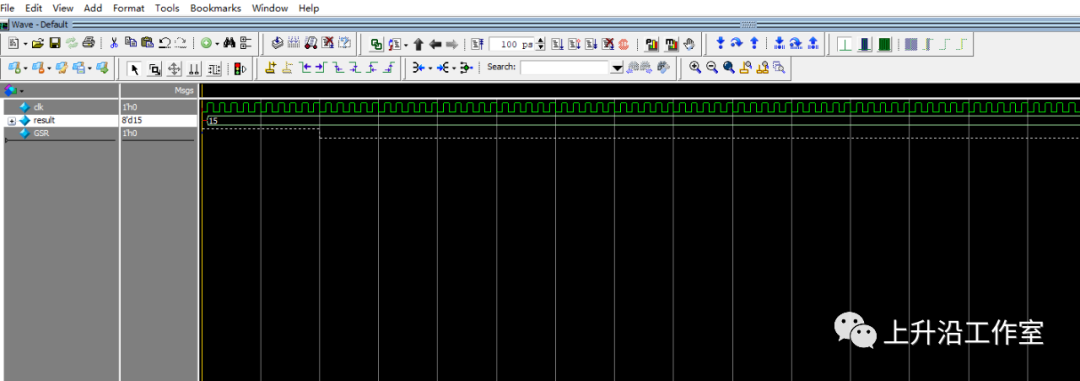

仿真結(jié)果如下所示:

04、 條件編譯指令(`ifdef、`elsif、`endif)

條件預(yù)編譯指令有如下幾種形式:

1. `ifdef宏名

程序段1

`elsif

程序段2

`endif

當(dāng)宏名被定義,則對程序段1進行編譯,程序段2被忽略;否則編譯程序段2,程序段1倍忽略。

`ifdef宏名

程序段1

`endif

其中程序段可以是語句組也可以是命令行

例:

`timescale1ns/1ps`defineMODE_ADD`defineMODE_ENABLEmodule test_add(input clk,rst_n,output reg [ 15 : 00 ] data_cal,output reg [ 15 : 00 ] data_cal2);:0]data;MODE_ADDclk or negedge rst_n) beginif(!rst_n)data_cal <= 1'b0;elsedata_cal <= data_cal + 16'd100;endMODE_ADD2clk or negedge rst_n) beginif(!rst_n)data_cal <= 1'b0;elsedata_cal <= data_cal + 16'd200;end`endifMODE_ENABLEM 10MODE_ENABLE2M 20`endifclk or negedge rst_n) beginif(!rst_n)data_cal2 <= 1'b0;elsedata_cal2 <= `M;end=`M;endmodule

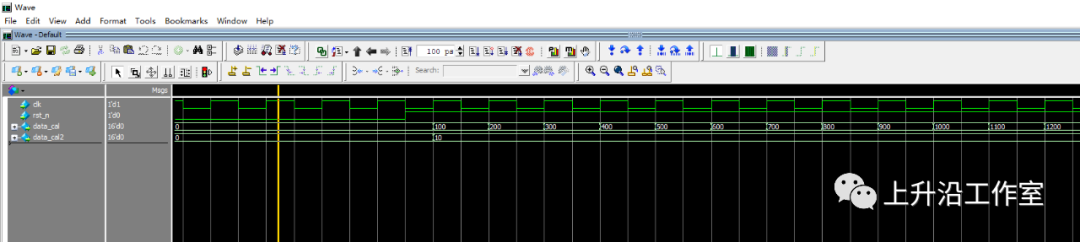

仿真結(jié)果如下:

如果將:

`defineMODE_ADD`defineMODE_ENABLE改成`defineMODE_ADD2`defineMODE_ENABLE2

仿真結(jié)果如下:

審核編輯:郭婷

-

仿真

+關(guān)注

關(guān)注

50文章

4124瀏覽量

134005 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110400 -

eda

+關(guān)注

關(guān)注

71文章

2788瀏覽量

173879

原文標(biāo)題:Verilog基礎(chǔ)知識學(xué)習(xí)筆記(五)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

未能獲得預(yù)編譯的模擬庫信息

Verilog-HDL實踐與應(yīng)用系統(tǒng)設(shè)計

Verilog HDL華為入門教程

Verilog HDL入門教程(華為絕密資料)

Verilog HDL硬件描述語言_Verilog語言要素

Verilog HDL入門教程

Verilog HDL入門教程之Verilog HDL數(shù)字系統(tǒng)設(shè)計教程

如何設(shè)計常用模塊的Verilog HDL?

Verilog教程之Verilog的命令格式資料說明

Verilog HDL入門教程

什么是預(yù)編譯

Verilog HDL中常用預(yù)編譯命令介紹

Verilog HDL中常用預(yù)編譯命令介紹

評論