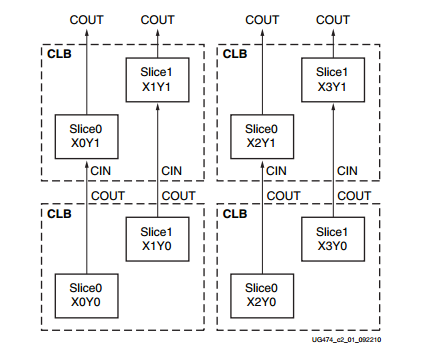

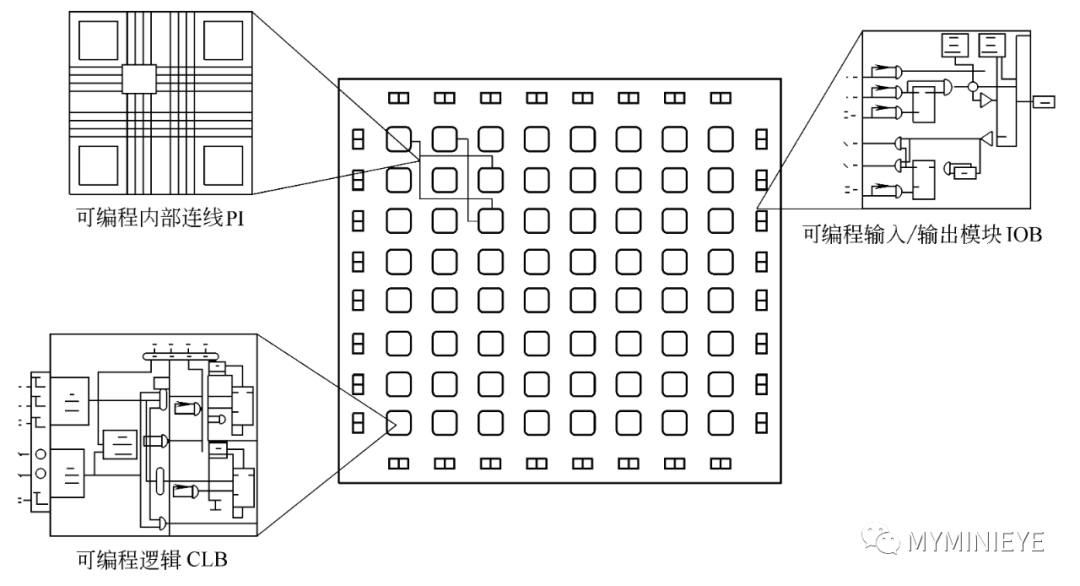

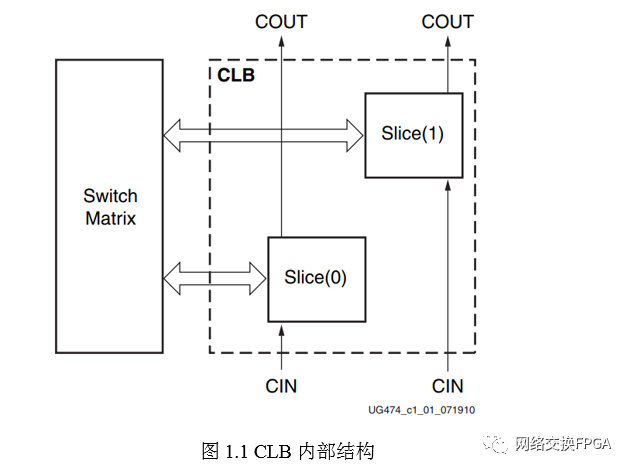

CLB是xilinx基本邏輯單元,每個CLB包含兩個slices,每個slices由4個(A,B,C,D)6輸入LUT和8個寄存器組成。

同一CLB中的兩片slices沒有直接的線路連接,分屬于兩個不同的列。每列擁有獨立的快速進位鏈資源。

slice分為兩種類型 SLICEL, SLICEM . SLICEL可用于產生邏輯,算術,ROM。SLICEM除以上作用外還可配置成分布式RAM或32位的移位寄存器。每個CLB可包含兩個SLICEL或者一個SLICEL與一個SLICEM.

7系列的LUT包含6個輸入 A1 -A6 , 兩個輸出 O5 , O6 .

可配置成6輸入查找表,O6此時作為輸出。或者兩個5輸入的查找表,A1-A5作為輸入 A6拉高,O5,O6作為輸出。

一個LUT包含6個輸入,邏輯容量為2^6bit,為實現7輸入邏輯需要2^7容量,對于更多輸入也一樣。每個SLICES有4個LUT,256bit容量能夠實現最多8bit輸入的邏輯。為了實現此功能,每個SLICES還包括3個MUX(多路選擇器)

F7AMUX 用于產生7輸入的邏輯功能,用于連接A,B兩個LUT

F7BMUX 用于產生7輸入的邏輯功能, 用于連接C,D兩個LUT

F8MUX 用于產生8輸入的邏輯功能, 用于連接4個LUT

對于大于8輸入的邏輯需要使用多個SLICES, 會增加邏輯實現的延時。

一個SLICES中的4個寄存器可以連接LUT或者MUX的輸出,或者被直接旁路不連接任何邏輯資源。寄存器的置位/復位端為高電平有效。只有CLK端能被設置為兩個極性,其他輸入若要改變電平需要插入邏輯資源。例如低電平復位需要額外的邏輯資源將rst端輸入取反。但設為上升/下降沿觸發(fā)寄存器不會帶來額外消耗。

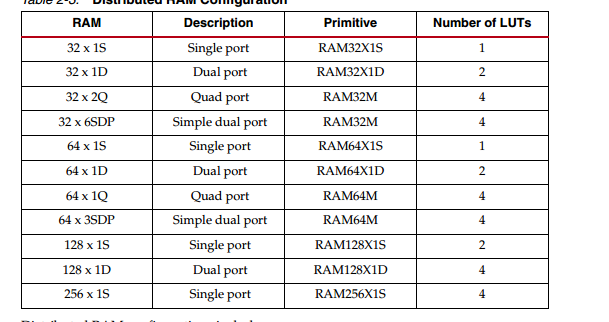

分布式RAM

SLICEM可以配置成分布式RAM,一個SLICEM可以配置成以下容量的RAM

多bit的情況需要增加相應倍數的LUT進行并聯。

分布式RAM和 BLOCK RAM的選擇遵循以下方法:

1. 小于或等于64bit容量的的都用分布式實現

2. 深度在64~128之間的,若無額外的block可用分布式RAM。要求異步讀取就使用分布式RAM。數據寬度大于16時用block ram.

3. 分布式RAM有比block ram更好的時序性能。分布式RAM在邏輯資源CLB中。而BLOCK RAM則在專門的存儲器列中,會產 生較大的布線延遲,布局也受制約。

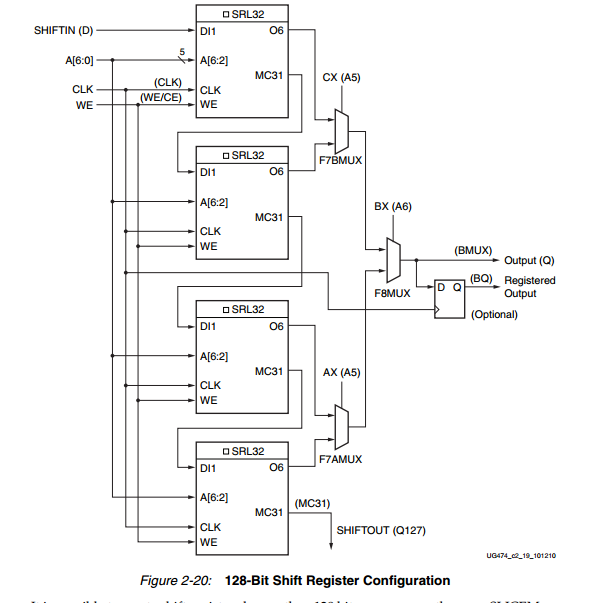

移位寄存器(SLICEM)

SLICEM中的LUT能在不使用觸發(fā)器的情況下設置成32bit的移位寄存器, 4個LUT可級聯成128bit的移位寄存器。并且能夠進行SLICEM間的級聯形成更大規(guī)模的移位寄存器。

MUX

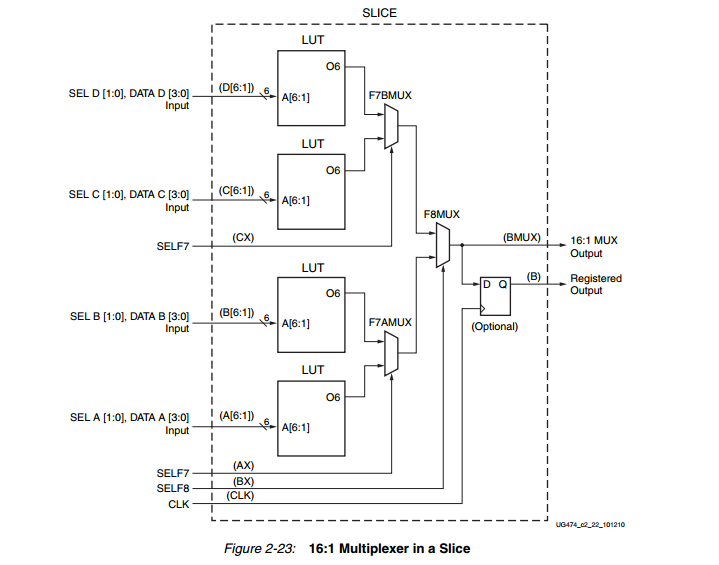

一個LUT可配置成4:1MUX.

兩個LUT可配置成最多8:1 MUX

四個LUT可配置成16個MUX

同樣可以通過連接多個SLICES達成更大規(guī)模設計,但是由于SLICE沒有直接連線,需要使用布線資源,會增加較大延遲。

進位鏈

每個SLICE有4bit的進位鏈。每bit都由一個進位MUX(MUXCY)和一個異或門組成,可在實現加法/減法器時生成進位邏輯。該MUXCY與XOR也可用于產生一般邏輯。

原文標題:FPGA學習-xilinx CLB資源詳解--slice、分布式RAM和Block ram

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

審核編輯:湯梓紅

-

Xilinx

+關注

關注

71文章

2171瀏覽量

122143 -

CLB

+關注

關注

0文章

29瀏覽量

5981 -

邏輯單元

+關注

關注

0文章

25瀏覽量

5146

原文標題:FPGA學習-xilinx CLB資源詳解--slice、分布式RAM和Block ram

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

以Xilinx的ZYNQ的7000系列為例,介紹CLB功能與結構

【干貨】編輯Xilinx FPGA內LUT內容的詳細方案

Xilinx FPGA中的基礎邏輯單元

如何在LUT和邏輯元件之間以及邏輯元件和邏輯單元之間進行交換

請問“邏輯單元”的意思是什么?

是否可以使用邏輯單元的verilog代碼?

FPGA從Xilinx的7系列學起(2)

Xilinx 7系列FPGA使用之CLB探索(一)

FPGA內部可編程邏輯CLB資源分析

CLB 如何顛覆傳統(tǒng)邏輯

如何使用可配置邏輯塊 (CLB) 實施定制串行接口

一文詳解xilinx CLB基本邏輯單元

一文詳解xilinx CLB基本邏輯單元

評論