本文探討了RISC-V的開源硬件模型背后的好處,討論了它的壽命、可移植性和可靠性。

RISC-V用于嵌入式應用程序的勢頭是不可否認的。如今,RISC-V基金會擁有超過100家公司支持免費和開放的RISC-V指令集架構(ISA),隨著越來越多的工具、軟件、硬件和操作系統供應商加入,其成員數量也在迅速增長。憑借其不斷擴大的生態系統,RISC-V為軟件和硬件設計人員提供了一個令人信服的替代現有嵌入式處理器的替代方案,隨著采用率的增長,在嵌入式設計中開啟了處理器創新的新時代。

RISC-V開啟新時代的原因歸結為三個關鍵因素:壽命、便攜性和可靠性。這三個原因都與RISC-V特別引人注目的原因有關。與通常在每一代都添加指令的已經建立的處理器架構不同,設計人員可以依靠帶有RISC-V的固定ISA,確保他們的軟件投資的壽命。這種壽命對于功能安全、認證和長產品生命周期很重要的嵌入式應用程序特別有利。

凍結的ISA

為了實現RISC-V的廣泛使用并讓市場決定處理器架構,RISC-V背后的加州大學伯克利分校工程團隊在2014年第25屆熱芯片研討會上介紹該技術前不久凍結了ISA。隨著2015年,非營利性RISC-V基金會成員的任務是指導HW/SW規范和生態系統的未來發展,以及推動ISA的采用。隨著基本ISA的確定和可選擴展的可用,設計人員可以實施針對其特定工作負載量身定制的處理器,而不必圍繞標準的、現成的處理器設計進行工作,這種設計幾乎沒有任何定制空間。

許多RTOS和完整的操作系統現在都支持RISC-V。由于Linux操作系統的使用越來越多,RISC-V對嵌入式應用程序特別有吸引力。這使設計人員能夠迅速采用ISA作為直接本地硬件實現的新開放標準架構。然而,即使不使用Linux,ISA所提供的凍結架構、壽命、可移植性和可靠性也是需要考慮的關鍵因素。

RISC-V擴展

凍結的ISA意味著軟件可以開發一次并在任何支持正在使用的擴展(如果有)的RISC-V設備上無限期運行。擴展是添加新指令的唯一方法。目前,有五個擴展名,也已被凍結。這些擴展包括:

M表示整數乘除。

A原子指令

F表示單精度浮點

D表示雙精度浮點

C用于壓縮指令

RISC-V處理器優勢

這種可預測性和簡單性對處理器設計和軟件開發有很多好處。讓我們一一來看看。

長壽

RISC-VISA提供了一個穩定、干凈的設計平臺,在用戶和特權模式之間有清晰和安全的分離,因為ISA是固定的并且包含少于50條指令。如果全部實現多個標準擴展,總數仍不足200個。不是引入新版本的ISA,而是通過擴展對標準指令集進行添加,便于未來設計增加穩定性。更少的指令意味著可以創建更簡單的架構,從而提高處理器實施的成本效益和功率效率。對于軟件開發人員來說,這意味著保留投資。一次編寫軟件并在任何RISC-V內核上永久運行。這對于必須支持數十年的產品壽命長的產品通常至關重要,

可移植性

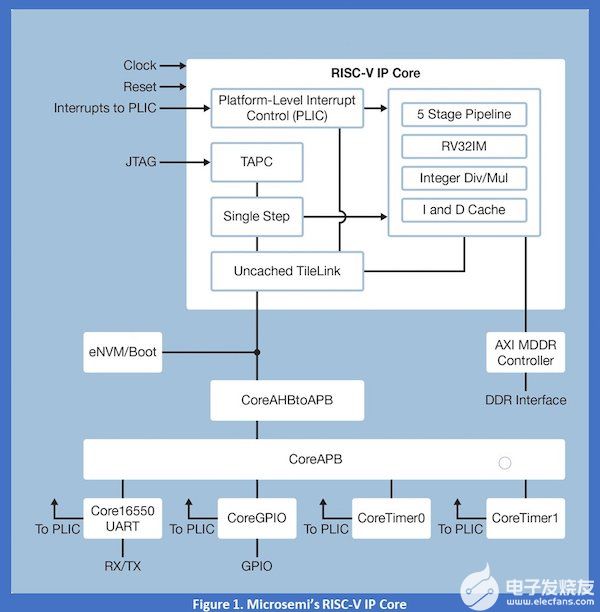

RISC-V使設計更容易擴大到大批量。例如,設計可以在運行軟RISC-V內核的FPGA中開始發貨(圖1)。由于該軟件將在任何具有RISC-V內核的設備上完全可移植,因此設計人員擁有本質上是“免版稅”的處理器子系統RTL代碼,可以在硬件中實現。設計人員可以修改、調整和遷移他們的設計到最適合他們產品的平臺。如果選定的FPGA需要更換為下一代器件,則無需重新編寫軟件代碼。現有的源RTL只需重新定位到另一個FPGA。此外,如果數量達到足夠高的水平,則可以將相同的RTL源重新定位到ASIC,而無需支付任何特許權使用費。

圖2.RISC-VIP內核圖表。

可靠性和安全性

RISC-V的靈活性實現了獨特的解決方案,特別是對于需要功能安全的嵌入式設計。例如,在具有多個功能等效內核的系統中,這些內核自主設計以實現終極冗余。一個這樣的內核可能是MicrosemiMi-VRV32IM,另一個內核可能是功能相同但完全不同的內部設計。RISC-V還允許在微架構上完全靈活;因此一個內核可以為數據和指令高速緩存提供單事件翻轉(SEU)保護措施。可以使用許多其他安全預防技術,因為RISC-V允許訪問RTL。

雖然Intelx86和ARM處理器架構的成熟變體不太可能很快消失,但鑒于設計人員必須自由定制,RISC-V處理器生態系統已準備好在嵌入式市場快速增長。處理器架構的設計本質上是靈活的,因此實現可以在硬件中加速某些操作,或者,例如,專門針對低功耗進行優化。設計人員還可以靈活地連接他們想要的任何總線接口,而不是僅僅依賴于成熟的處理器供應商提供的總線。由于ISA的固定性質,RISC-V微體系結構的任何變化都是可以接受的。

RISC-V資源

要為您的下一個設計了解更多關于RISC-V的信息,可以從幾個地方開始。

有關RISC-V及其成員的背景信息,請訪問RISC-V基金會網站。如果您想直接投入并開始為RISC-V內核編寫C代碼,請訪問Microsemi的Github站點并查看IGLOO2創意開發板RISC-V項目。Microsemi是第一家提供開放架構RISC-VIP內核和綜合軟件IDE解決方案的FPGA供應商。設計人員可以在多個基于閃存的FPGA中部署RISC-VIP內核,包括PolarFireFPGA、IGLOO2和RTG4設備。Mi-VCreative板(圖2)包含一個IGLOO2FPGA,預編程了一個RISC-V內核,可以開箱即用地運行“helloworld”。

對于軟件代碼開發,托管在Linux或Windows平臺上的基于Eclipse的軟控制臺集成開發環境(IDE)提供了完整的開發支持,包括C或C++編譯器和調試器功能。MicrosemiRISC-VIP內核、LiberoSoC開發軟件和軟控制臺IDE都可以從MicrosemiGithub站點免費下載。

憑借其凍結的ISA、簡單性、可移植性和可靠性,RISC-V為設計人員提供了一種全新的處理器范例,以超越既定處理器現狀的限制并突破創新的界限。

-

處理器

+關注

關注

68文章

19409瀏覽量

231207 -

開源硬件

+關注

關注

8文章

212瀏覽量

29979 -

RISC-V

+關注

關注

45文章

2324瀏覽量

46604

發布評論請先 登錄

相關推薦

關于RISC-V芯片的應用學習總結

Imagination放棄RISC-V處理器內核開發

Andes晶心科技推出D45-SE RISC-V處理器

Rivos全新產品采用Andes晶心科技NX45 RISC-V處理器

《RISC-V能否復制Linux 的成功?》

RISC-V,即將進入應用的爆發期

risc-v在人工智能圖像處理應用前景分析

淺談國產異構雙核RISC-V+FPGA處理器AG32VF407的優勢和應用場景

淺析RISC-V領先ARM的優勢

請問ESP32s3 ULP RISC-V協處理器是否支持ADC的讀取?

RISC-V有哪些優點和缺點

RISC-V有哪些優缺點?是堅持ARM方向還是投入risc-V的懷抱?

RISC-V 基礎學習:RISC-V 基礎介紹

芯來科技正式發布基于RISC-V處理器的HSM子系統解決方案

RISC-V處理器的優勢是什么

RISC-V處理器的優勢是什么

評論