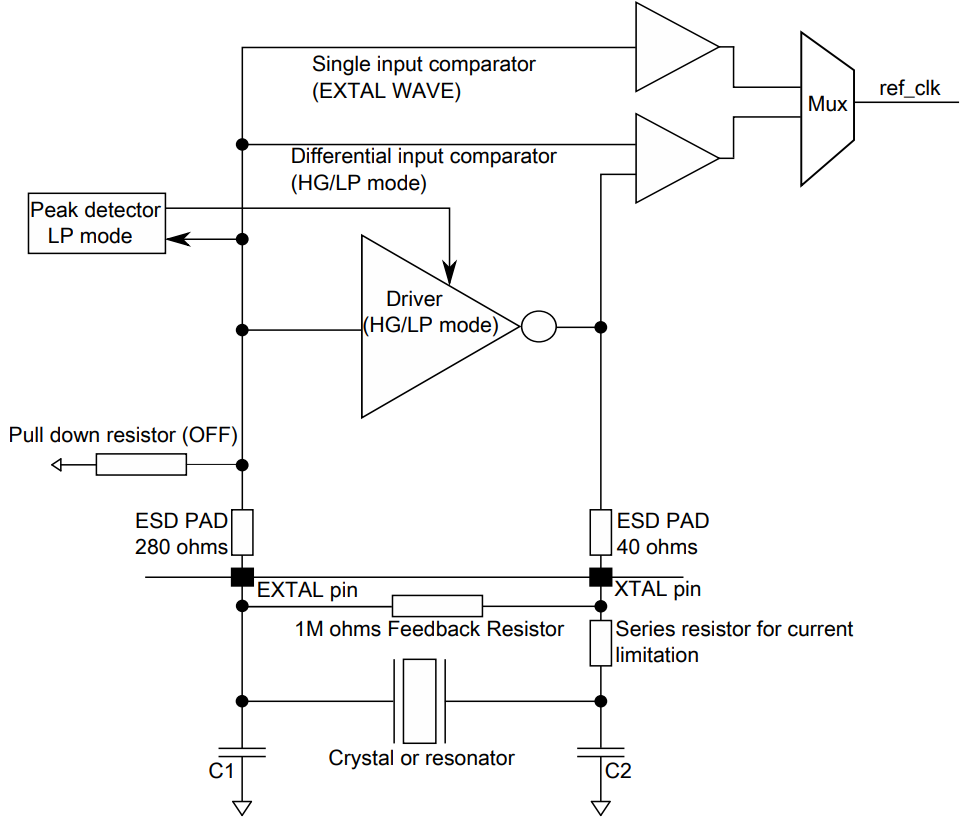

時(shí)鐘(Clock)在一般SoC電路上是必不可少的,精準(zhǔn)的時(shí)鐘通常由晶振提供,晶振很難集成到芯片中去,而是作為分立元件設(shè)計(jì)在PCB上。它就像是人的心臟,如果時(shí)鐘出錯(cuò)了,整個(gè)電路或者通信就會(huì)發(fā)生問題。比如,16MHz晶振給一個(gè)2.4G藍(lán)牙芯片提供參考時(shí)鐘,如果16MHz出現(xiàn)頻偏,比如偏-48ppm(頻率為15.999223MHz),由于射頻是參考時(shí)鐘倍頻上去的,也會(huì)出現(xiàn)-48ppm的頻偏(藍(lán)牙頻點(diǎn)變成2,399,883,450Hz,約100KHz的頻偏),造成藍(lán)牙與標(biāo)準(zhǔn)頻率的對(duì)端無法通信。因此一個(gè)好的時(shí)鐘電路是非常必要的,此篇文章對(duì)時(shí)鐘電路中的晶振電路layout簡(jiǎn)單做一下闡述。

對(duì)于晶振電路,我們需要從幾個(gè)方面考慮設(shè)計(jì):

降低寄生電容的不確定性

降低溫度的不確定性

減少對(duì)其他電路的干擾

設(shè)計(jì)注意點(diǎn):

1. 晶振盡量靠近芯片,保證線路盡量短,防止線路過長(zhǎng)導(dǎo)致串?dāng)_以及寄生電容。

2. 晶振周圍打地孔做包地處理。

3. 晶振底部不要走信號(hào)線,尤其是其他高頻時(shí)鐘線。

4. 負(fù)載電容的回流地要短。

5. 走線時(shí)先經(jīng)過電容再進(jìn)入晶振。

下面分別舉例貼片無源晶振及有源晶振的走線方式:

兩腳貼片無源晶振

6. 封裝較大,可從晶振中間出線。

7. 如果有測(cè)試點(diǎn),使stub盡量短。

8. 走線可以走成假差分形式。盡量走在同一層。

9. 部分晶振底下需要做掏空處理,以防電容效應(yīng)以及熱效應(yīng)造成頻偏。

10. 如果是鐵殼晶振,外殼做接地處理,提高抗干擾能力。

11. 晶振選型需要選工作溫度達(dá)到125攝氏度及以上的。

四腳貼片無源晶振

HTOL測(cè)試板上有源晶振的布局:

由于老化測(cè)試中一般芯片都在socket中測(cè)試,所以晶振不能與Socket放置在同一面,否則晶振會(huì)距離芯片較遠(yuǎn)。

晶振放在反面則需要打孔后連接至芯片管腳,此時(shí)需要在打孔附近增加回流地孔。

有源晶振需額外注意電源濾波電路處的電容,從大到小依次靠近晶振放置。

貼片有源晶振

原文標(biāo)題:PCB上晶振電路的layout設(shè)計(jì)

文章出處:【微信公眾號(hào):上海季豐電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

審核編輯:湯梓紅

-

Layout

+關(guān)注

關(guān)注

14文章

406瀏覽量

61958 -

時(shí)鐘電路

+關(guān)注

關(guān)注

10文章

239瀏覽量

50802 -

晶振電路

+關(guān)注

關(guān)注

7文章

92瀏覽量

25389

原文標(biāo)題:PCB上晶振電路的layout設(shè)計(jì)

文章出處:【微信號(hào):zzz9970814,微信公眾號(hào):上海季豐電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

晶振在“智能三表”中的應(yīng)用

有源晶振與無源晶振穩(wěn)定性比較:為何有源晶振更勝一籌?

無源晶振的等效電路與電路結(jié)構(gòu)解析

晶振的抗干擾設(shè)計(jì):確保系統(tǒng)時(shí)鐘的穩(wěn)定性

晶振過驅(qū)的影響及其預(yù)防措施:電阻與電容在晶振電路中的應(yīng)用

晶振在電路中有什么作用

晶振在GPS時(shí)鐘系統(tǒng)中的應(yīng)用

單片機(jī)振蕩電路晶振不起振原因分析與解決方法

如何減少無源晶振在電路中的電磁干擾

時(shí)鐘電路中的晶振電路layout簡(jiǎn)單闡述

時(shí)鐘電路中的晶振電路layout簡(jiǎn)單闡述

評(píng)論