在硬件準備就緒時開始嵌入式軟件開發的日子已經一去不復返了。軟件的規模和復雜性不斷增加,因此需要更早的開始日期才能有機會按時發貨。考慮到與軟件開發相關的投資和風險,公司必須確保在硅流片之前進行適當的軟件集成。不斷縮短的上市時間窗口進一步加劇了這些挑戰。

唯一的解決方案是尋找執行方法,因此在最終目標硬件可用之前測試和調試軟件。甚至在硬件設計最終確定之前,開發通常就必須認真開始。改進硬件設計和驗證以及加速軟件啟動的一種方法是將應用程序部署在虛擬或仿真硬件上。

虛擬原型

“虛擬原型”一詞沒有單一、精確的定義。就本文而言,該術語將用于描述可以運行嵌入式代碼的任何環境,從而在實際目標系統可用之前實現有用的開發。讓我們仔細看看這些可能性。

在 PC 上運行的本機代碼

這顯然是在 PC 上編譯和運行代碼的第一步。工具很容易獲得、便宜,甚至是免費的,而且 PC 提供了高級別的功能。這個環境非常適合測試算法和基本邏輯。與實際目標相比,代碼在 PC 上的運行速度可能會更快,因為 PC 的 CPU 可能比嵌入式處理器更強大。

除了時鐘速度之外,代碼時序沒有用處,因為 x86 處理器上的指令組合與大多數嵌入式設備非常不同。一旦代碼需要與硬件或實時操作系統 (RTOS) 交互,這個執行環境就不再有用了。

本機代碼與外圍/系統模型一起運行

大多數 RTOS 制造商都提供了一個主機執行環境,可以運行特殊版本的 RTOS 或在 Windows 下模擬其功能。這與提供外圍設備功能模型的方法一起,可以取得進一步的進展。然而,時機仍然具有誤導性。

在評估板上執行

大多數半導體供應商都提供低成本評估板,以促進其 CPU 的快速部署。商業 RTOS 產品,如 Mentor Embedded 的 Nucleus RTOS 可以為此類電路板預配置,從而實現快速生產。

這種執行環境很有吸引力,因為 CPU 速度和指令組合可能非常接近最終目標,這使得時間敏感代碼的測試變得可行。這種環境的準確性取決于外圍設備與目標設備的相似性。

使用指令集模擬器

盡管執行真實芯片的代碼看起來很有吸引力,但它的缺點是需要添加代碼才能獲得某些軟件功能的可見性。這稱為“檢測”代碼。另一種方法是使用指令集模擬器 (ISS),它在逐條指令的基礎上模擬代碼執行。ISS 可以以接近實時的速度運行,并提供精確、高度可見的代碼執行。實際上,當 ISS 跟蹤仿真期間消耗的時鐘周期時,可以停止實時。

大多數 ISS 產品允許某種功能外圍建模,這使得軟件開發取得重大進展。

具有外圍設備硬件描述語言模型的 ISS(協同仿真)

硬件是使用硬件描述語言 (HDL) 設計的,例如 VHDL 或 Verilog。設計人員經常使用仿真器來驗證他們的 HDL 設計,并且當今的許多開發工具將 ISS 與 HDL 仿真器相結合。這使代碼能夠在與看似真實的硬件交互的準確 CPU 環境中執行。軟件開發人員可以使用最終目標系統的 HDL 模型來開發與硬件密切交互的驅動程序和引導代碼等軟件組件。

協同仿真的缺點是更高的精度是以降低執行速度為代價的。

完整系統的 HDL 模型,包括 CPU

最準確的虛擬原型應該是整個系統的 HDL 模型,包括 CPU 和外圍設備,這似乎是合乎邏輯的。三個原因解釋了為什么情況并非如此:

這種模型上的代碼執行速度將非常緩慢。完成任何有用的事情都不夠快。

CPU 的 HDL 不太可能可用。

由于國際空間站很可能經過精心設計,因此使用它沒有任何缺點,但確實將性能提高到了有用的水平。

具有 SystemC 外設模型的 ISS

為了允許可以適應軟件執行的適當仿真速度,可以使用諸如 SystemC(C/C++ 類庫)之類的更高抽象語言對系統進行建模。更高抽象級別的建模使用松散或近似的時序。這種時序適用于軟件執行和性能分析。

硬件仿真

到目前為止討論的虛擬原型技術可以繪制在代碼執行速度與精度的關系圖上,并且基本上會產生一條直線(參見圖 1)。開發人員可以從一系列可能性中進行選擇:一個極端是快速、抽象的模擬,另一個是緩慢、精確的模擬。然而,另一種技術逆勢而上,偏離了直線。

圖 1:除仿真外,虛擬原型環境在代碼執行速度與精度的關系圖中形成一條直線。

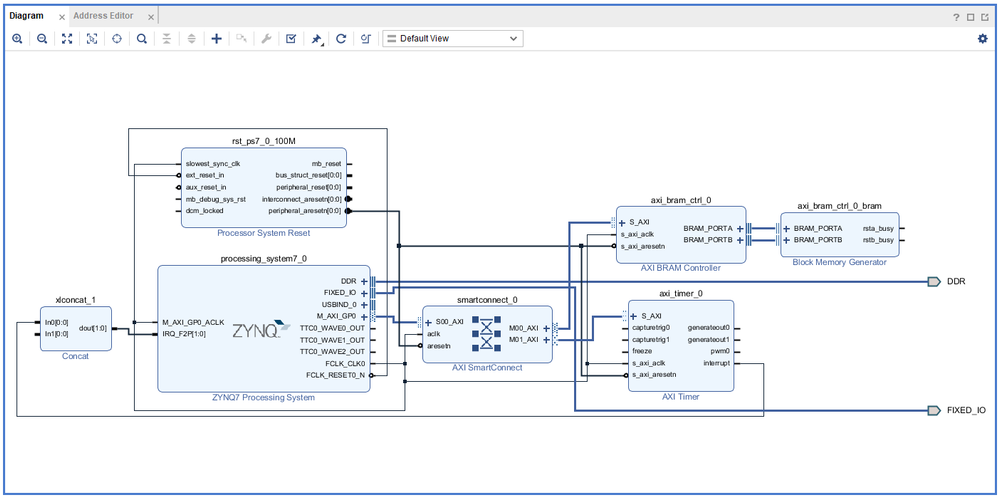

盡管只需使用功能強大的臺式計算機就可以降低 HDL 仿真的速度限制,但這也有限制,設計人員總是想要更多。電子設計自動化 (EDA) 社區的回應是開發仿真。仿真器是一種專門的硬件,實際上提供了運行 HDL 仿真的專用環境。這通常使用 FPGA 來實現。

使用 ISS、SystemC 模型和模擬一些外圍硬件的仿真器構建的集成平臺打破常規,提供精確、高性能的執行環境。運行虛擬目標和仿真可以更深入地了解硬件和軟件執行線程,并實現更高效的調試和系統性能分析。

超越調試

嵌入式軟件開發人員傳統上專注于讓他們的代碼正常運行。在最高抽象級別,這導致設備以符合設計規范的可預測方式響應刺激。這并沒有改變,但開發人員的簡介正在變得更廣泛。對軟件開發人員工作量的最重要補充是對功率的考慮。

低功耗設計之所以成為熱門話題,有幾個原因。雖然這在歷史上一直是硬件問題,但今天的復雜設計為根據系統的當前狀態、軟件和實時環境調整功耗提供了許多機會。該狀態由軟件確定;因此,電源管理正在成為一個軟件問題。

使用虛擬原型在硬件可用性之前開發和調試電源管理代碼是一項艱巨的任務,但這正是我們所需要的。當然,原則上都是可以的;硬件模擬可以得出功耗數據,并且可以測量CPU的實際功耗。這只是一個以有意義的方式將此信息傳達給軟件開發人員的問題。

前進的道路

任何認為軟件和硬件開發是獨立活動的想法都必須摒棄。好消息是,片上系統 (SoC) 生產商現在認識到需要先于芯片進行嵌入式軟件開發。壞消息是,盡管傳統的 EDA 硬件工具可以通過仿真和仿真運行嵌入式軟件,但它們并不關注嵌入式系統設計的關鍵問題,包括操作系統上下文、多核和線程處理以及緩存考慮。

需要一種集成方法來提供設計為以良好協調的方式工作并以硬件和軟件團隊都熟悉的方式呈現信息的工具。軟件開發人員必須能夠使用他們用來開發將在 FPGA 原型和具有集成技術的最終芯片上運行的應用程序所利用的相同本地工具更早地與硬件進行交互。Mentor Embedded Platform 中提供了一種這樣的統一方法,它結合了 Mentor Graphics 的熟悉技術,例如使用 Vista 硬件調試和分析的虛擬原型設計以及用于軟件開發的 Sourcery CodeBench 集成開發環境 (IDE)。通過使用這個集成嵌入式平臺進行早期軟件開發,開發人員可以使用虛擬和仿真硬件進行性能分析,

這種跨學科的早期研究改進了設計硬件并加速了 SoC 和嵌入式系統的軟件調試和啟動。軟件開發人員和硬件工程師都同意這是朝著正確方向邁出的一步。

審核編輯:郭婷

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606064 -

嵌入式

+關注

關注

5094文章

19178瀏覽量

307732 -

soc

+關注

關注

38文章

4204瀏覽量

219113

發布評論請先 登錄

相關推薦

嵌入式系統的調試技巧

嵌入式系統的硬件平臺組成

嵌入式Linux專題(一)——嵌入式Linux系統構成及啟動流程

集成嵌入式平臺加速了SoC和嵌入式系統的軟件調試和啟動

集成嵌入式平臺加速了SoC和嵌入式系統的軟件調試和啟動

評論