學習內容

學習關于ZYNQ IP核中的GP接口和HP接口的異同,介紹關于AXI_GP接口和AXI_HP接口的相關內容。

AXI_HP和AXI_GP異同

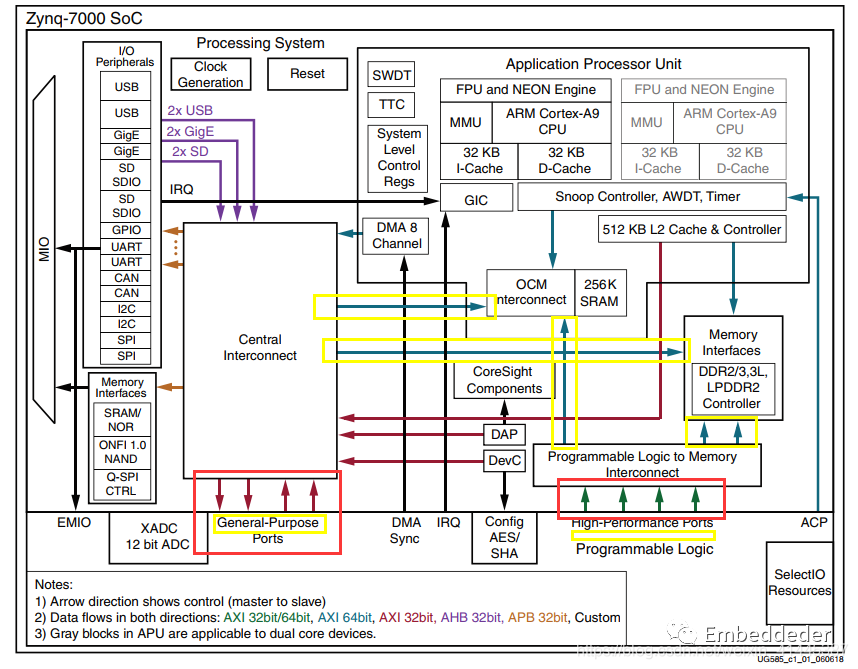

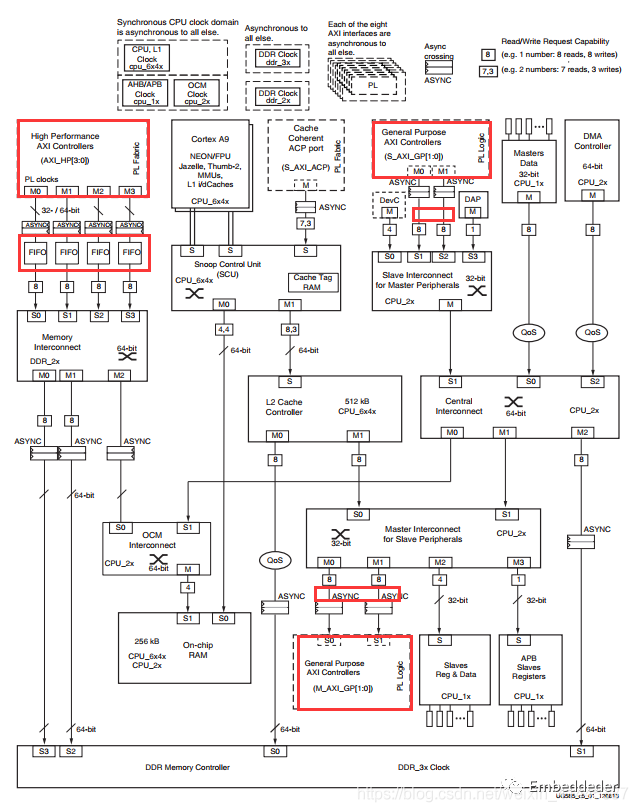

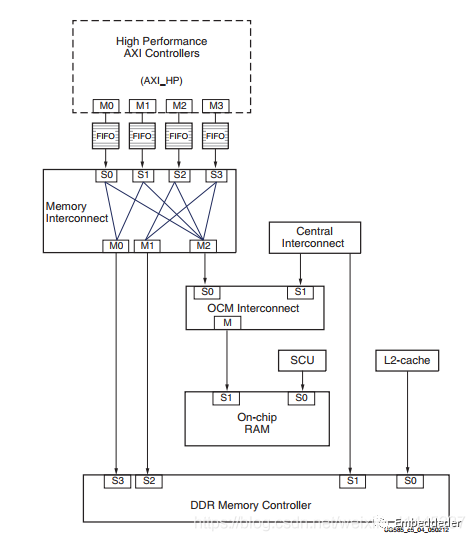

首先給出ZYNQ SoC的系統(tǒng)框圖,如下圖所示。在圖中,箭頭方向代表主機到從機的方向。

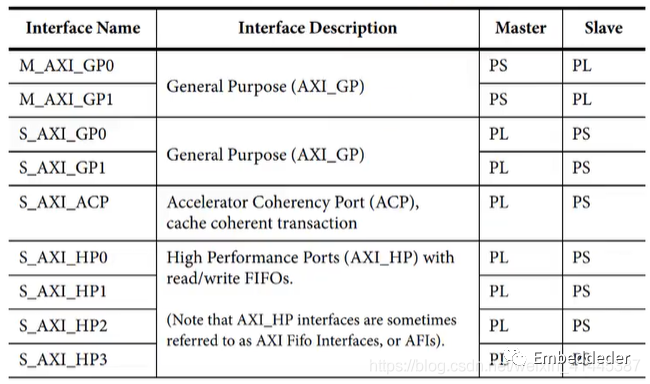

對于GP接口(general purpose)通用目的接口,有四個接口(兩個從端口,兩個主端口);HP接口(high-performance purpose)高性能接口,有四個接口(四個都是從端口)。GP接口直接連接到的是中央互聯(lián)區(qū)(central interconnect),然后由中央互聯(lián)區(qū)再連接到OCM interconnect和存儲器接口上;而HP接口直接連接到的是OCM interconnect和存儲器接口。所以對于GP接口,通常使用他進行控制配置;而對于HP接口,通常使用它進行數據傳輸交互。下圖是HP和GP對應主從機具體信息:

AXI_HP接口

4個AXI HP接口為PL的主機提供了DDR和OCM存儲器的高帶寬的數據路徑。 每個HP接口包括兩個的FIFO緩存,用于讀寫傳輸。PL到內存互連高速AXI HP端口路由連接到兩個DDR內存端口和一個OCM存儲器端口。AXI HP接口也被稱為AFI (AXI FIFO接口),以強調它們的緩沖功能。 PL電平移位器必須通過LVL SHFTR EN啟用后,才能進行PL邏輯通信。

特點

這些接口被設計為在PL主存儲器和PS存儲器(包括DDR和片上RAM)之間提供一個高吞吐量的數據路徑。主要功能包括:

可以實現(xiàn)32或64位數據位寬的主接口(每個端口獨立編程)。

在32位接口模式下,可以進行動態(tài)配置位為64位,以實現(xiàn)對齊傳輸,通過AxCACHE [1]可以進行控制。

在32位接口模式下,為未對齊的32位傳輸自動擴展到64位。

可編程的寫命令釋放閾值。

PL和PS之間的所有AXI接口的異步時鐘域交叉。

使用1kb (128 × 64位)數據緩存FIFO來平滑“長延遲”傳輸,用于讀寫。

從PL端口提供QoS信令。

命令和數據FIFO填充級計數可用于PL端。

支持標準AXI 3.0接口。

可編程命令下發(fā)到互連,分別用于讀和寫命令。

14到70個指令范圍的高性能從接口讀接受能力。(取決于突發(fā)長度)

8到32個指令范圍的高性能從接口寫接受能力。(取決于突發(fā)長度)

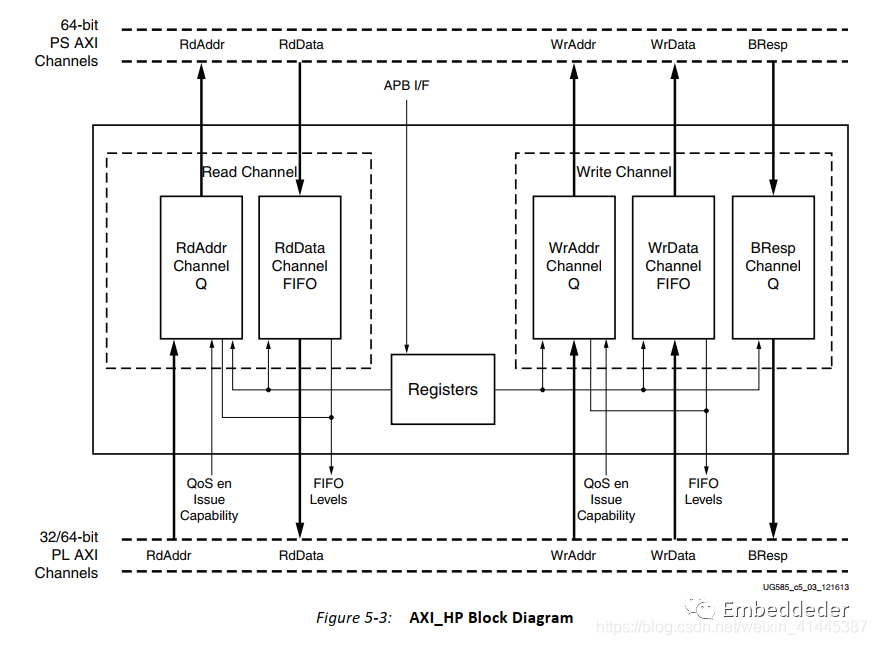

AXI_HP接口的框圖

為了提高讀寫的性能,在讀寫數據通道添加了FIFO用于讀寫數據的傳輸。

有兩組AXI端口,一組直接連接到PL,另一組連接到AXI互連矩陣,允許訪問DDR和OCM內存:

AXI_GP接口

AXI_GP接口直接連接到主互連和從互連的端口,沒有任何額外的FIFO緩沖,不像AXI_HP接口使用FIFO緩沖以提高性能和吞吐量。因此,性能受到主互連端口和從互連端口的限制。這些接口僅用于通用用途,并不是為了實現(xiàn)高性能。

特點

AXI GP的特性包括:

支持標準AXI協(xié)議

數據總線寬度只有32位

主端口ID位寬為12位

主端口發(fā)送能力:8位讀,8位寫

從端口ID位寬為6位

從端口接受能力:8位讀,8位寫

Reference

Xilinx UG585

正點原子ZYNQ開發(fā)視頻教程

原文標題:Reference

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

存儲器

+關注

關注

38文章

7528瀏覽量

164340 -

接口

+關注

關注

33文章

8691瀏覽量

151911 -

HP

+關注

關注

1文章

86瀏覽量

40171

原文標題:Reference

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

Zynq MPSoC系列器件的AXI總線介紹

如何實現(xiàn)從microblaze端訪問ARM DDR?

玩轉Zynq連載34——[ex54] 基于Zynq的AXI GP總線的從機接口設計

如何避免AXI_hp總線鎖死?

AXI接口協(xié)議詳解

何謂 AXI?關于AXI3/AXI4的相關基礎知識

你必須了解的AXI總線詳解

AXI4-Stream Video 協(xié)議和AXI_VDMA的IP核介紹

關于AXI BRAM控制器的相關內容

AXI VIP當作master時如何使用?

AXI_GP接口和AXI_HP接口的相關內容

AXI_GP接口和AXI_HP接口的相關內容

評論