引言

在未來幾代器件中,光刻膠(PR)和殘留物的去除變得非常關鍵。在前端制程(FEOL)離子注入后(源極/漏極、擴展、haIos、深阱),使用PR封閉部分電路導致PR實質上硬化且難以去除。在后段制程(BEOL)蝕刻中,在不去除低k材料的情況下去除抗蝕劑和殘留物的選擇性是非常具有挑戰性的。概述了現狀、問題和一些新的方法。

介紹

光致抗蝕劑用于保護晶片的某些區域免受干蝕刻化學物質、離子注入等的影響。工藝完成后,需要選擇性地去除光致抗蝕劑并清潔表面,以確保表面沒有殘留物和顆粒。原則上,使用濕化學物質如熱SPM、有機溶劑或通過使用干等離子體的“灰化”去除抗蝕劑是可能的。然而,在干法蝕刻或注入處理過程中,抗蝕劑會發生化學改性,這種改性會顯著降低剝離速率。如果更具侵略性-例如,使用高度氧化的化學物質,這可能導致晶片上其他材料的不希望的侵蝕。雖然這些考慮幾十年來,對于單元工藝開發非常重要,對于45納米技術節點和更高技術節點的某些iTRS路線圖要求變得越來越嚴格,以至于工業實驗室正在考慮對cMOS集成流程的幾個模塊進行根本性的范式轉變。同時,新的替代集成方案,包括使用應變硅、金屬硬掩模和金屬柵電極,導致不同的要求。這使得對這一主題的研究更加復雜。

在下文中,我們華林科納總結了現狀、問題和新方法,重點關注FEOL中的源漏注入模塊和BEOL的低k干法刻蝕模塊。

FEOL:植入后抗蝕劑剝離

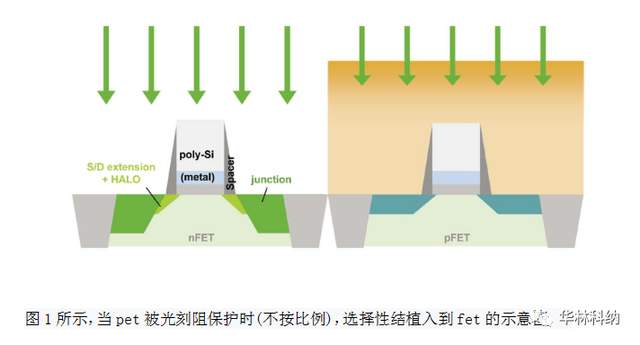

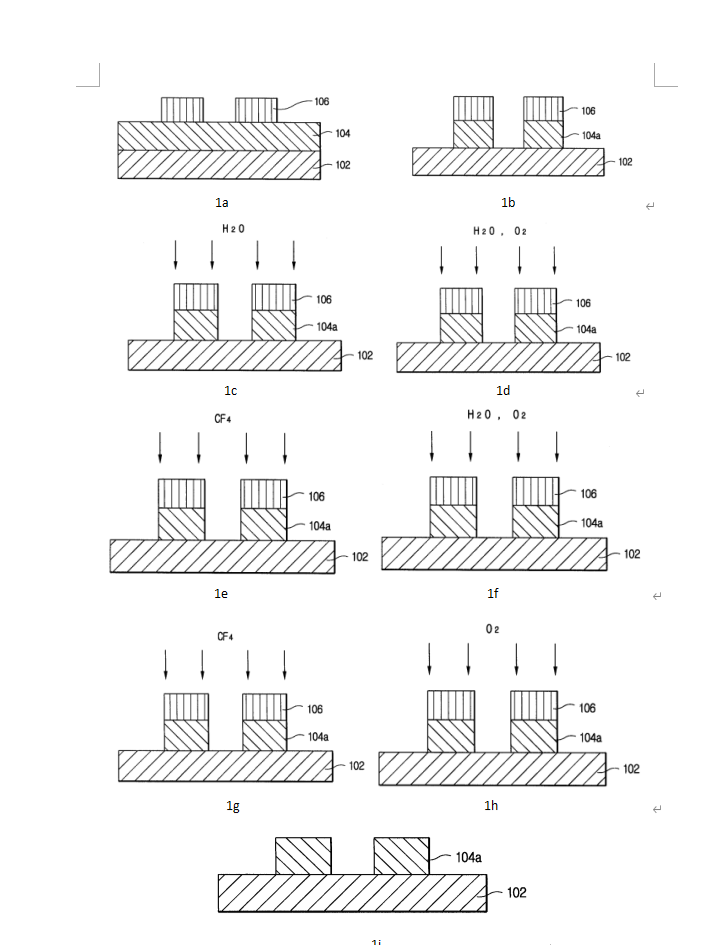

源極-漏極注入模塊場效應晶體管的源極/漏極(S/D)結是通過將摻雜劑離子注入硅襯底而形成的。這種注入通常涉及離子as、P、B或BF2的面密度約為。1012到幾個1015cm。離子能量的范圍從非常淺的S/D擴展的幾100eV到深注入的幾十keV。為了確保在同一芯片/晶片上制造的各種器件,特別是nFETs和pFETs,每個器件只接受適當的注入,需要進行選擇性注入。這是通過用圖案化的光致抗蝕劑進行掩蔽來實現的,如圖1示意性所示。因此,S/D區域中復雜的摻雜劑幾何形狀是通過光致抗蝕劑應用和圖案化、離子注入、抗蝕劑剝離和表面清潔的循環產生的。

注入抗蝕劑的離子導致近表面區域的化學改性。抗蝕劑聚合物的化學鍵被來自撞擊離子的能量破壞,這會導致聚合物主鏈斷裂。

結論

開發下一代光刻膠剝離劑和殘留物去除劑并不容易。它來自于大量的辛勤工作和致力于創造一種滿足90納米節點或以下技術需求的化學。

我們最新的化學技術可有效去除low-?電介質上的大塊光刻膠、灰渣和抗反射涂層。它還是100%水溶性的,是一種更加環保的解決方案。

-

蝕刻

+關注

關注

9文章

419瀏覽量

15508 -

晶片

+關注

關注

1文章

404瀏覽量

31582 -

光刻膠

+關注

關注

10文章

322瀏覽量

30346

發布評論請先 登錄

相關推薦

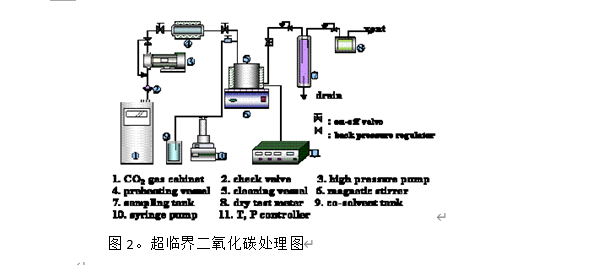

使用超臨界二氧化碳剝離碳化光刻膠的實驗

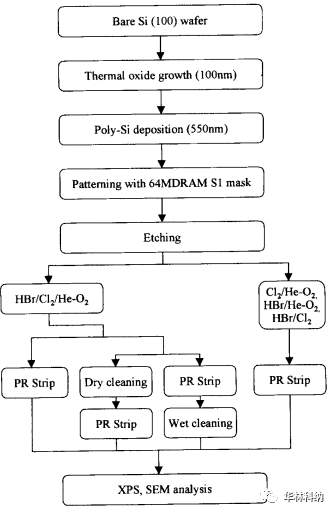

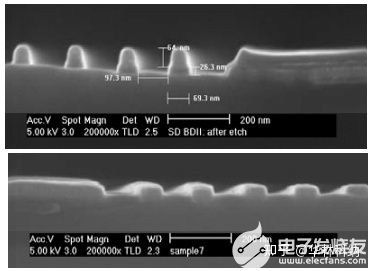

多晶硅蝕刻殘留物的的形成機理

Futurrex高端光刻膠

光刻膠殘留要怎么解決?

光刻膠

光刻膠在集成電路制造中的應用

《炬豐科技-半導體工藝》光刻前 GaAs 表面處理以改善濕化學蝕刻過程中的光刻膠附著力和改善濕蝕刻輪廓

Mattson利用歐洲的IMEC為低k/銅工藝開發光刻膠去除技術

使用濕化學物質去除光刻膠和殘留物

蝕刻后殘留物和光刻膠的去除方法

蝕刻后殘留物和光刻膠的去除方法

評論