我們所知道的第一個半導體路線圖可能是摩爾觀察到的,以他為名字的“摩爾定律”預計,芯片的計算能力隨著時間的增長呈指數增長。這促使芯片制造商定期對芯片進行升級,而這些廠商的設備和材料供應商也需要了解未來的技術將如何發展,因此制定了國際半導體技術路線圖(ITRS)半導體路線圖。芯片制造商之間合作,并進行了對未來需求和挑戰的預測,以提供對行業發展方向和需求的公開描述。

該路線圖已演變為國際設備和系統路線圖或IRDS路線圖,與ITRS路線圖的不同的是,它更多地是由上而下,而不是由下而上推導出來的。換句話說,它不是由芯片制造商的需求驅動的,而是通過預測未來器件性能的進展,然后確定什么類型的器件和結構可以提供未來所需的性能,其中包括了很多部分。本文重點介紹了2021年更新的光刻路線圖中的光刻部分。

有關芯片光刻路線圖的一些知識

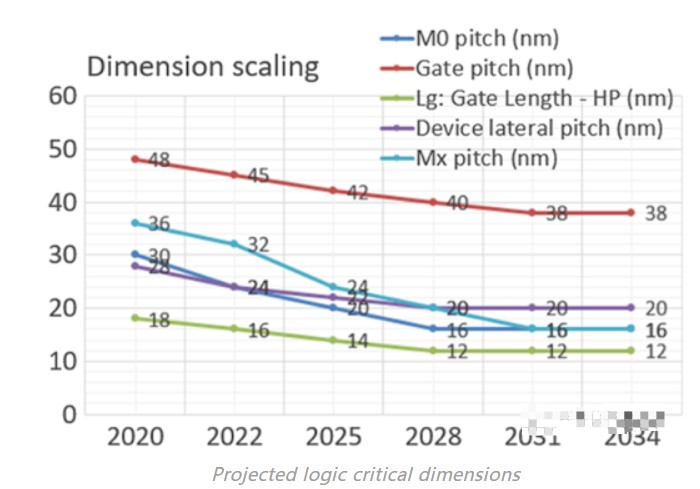

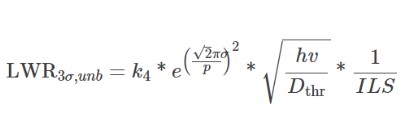

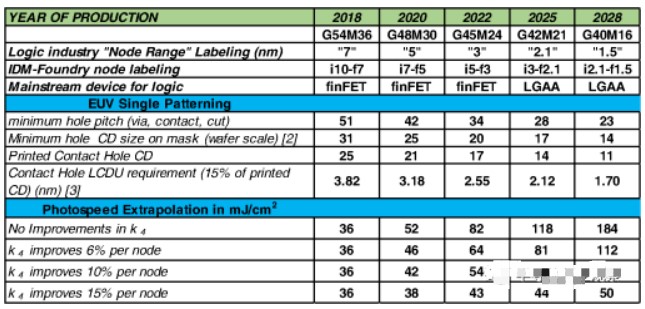

IRDS路線圖中More Moore部分預測了傳統邏輯和存儲芯片的改進。這部分升級是由大數據、物聯網、云計算和性能改進的一般需求驅動的。據預測,高性能邏輯器件將推動分辨率提高,而動態隨機存取存儲器(DRAM)器件的分辨率將落后于邏輯器件。非易失性存儲器已經主要轉向3D堆疊,將不會提高分辨率。關鍵邏輯節點的相關數據如圖所示。在接下來的10年里,尺寸會變得更小,然后隨著邏輯切換到3D堆疊,預計尺寸將停止縮小。

Projected logic critical dimensions

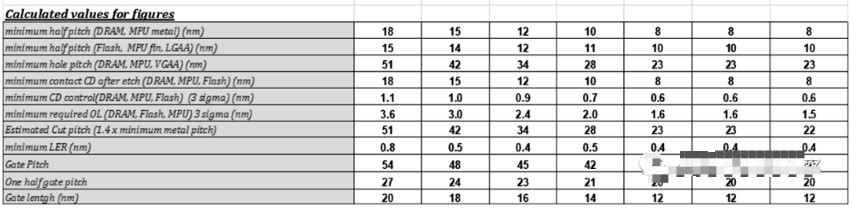

圖2顯示了2021年光刻路線圖中邏輯和DRAM預測的光刻需求。注意,節點的名稱用引號括起來,因為節點名稱不再代表任何邏輯產品中的實際物理維度。

邏輯和DRAM的投影光刻要求。

白色的單元格表示存在可制造解決方案來滿足這一要求,并正在進行優化,黃色的單元格表示已知可制造解決方案,可以實施,紅色的單元格表示未知可制造解決方案。

歷史上,光刻路線圖關注的一個關鍵挑戰就是分辨率,預計未來幾代芯片需要比目前光刻系統更好的分辨率。現在情況已經不同了,如果使用雙重圖案化,則已經通過在制造中使用的EUV系統來解決路線圖上的最小線和空間尺寸。對于接觸孔(contact holes)和其他孔類型水平(hole type levels),使用當前工具的雙重曝光可以解決直到2025年的“1.5 nm”所需的最小間距問題。“1.5 nm”節點將可以使用當時預計的High NA EUV工具進行雙重曝光。在此之后,預計不需要進一步的分辨率改進。

包含分辨率數據的單元是黃色的,“可制造的解決方案是已知的”,其中使用EUV的雙重圖案化已經可以產生這種尺寸。在沒有High NA EUV的情況下,EUV雙重圖案化是無法滿足的,或者在光刻委員會認為雙重圖案化的圖案質量有問題的情況下,單元被編碼為紅色,“可制造的解決方案是未知的”。

未來10年光刻技術面臨的主要挑戰主要與噪聲和缺陷有關,Overlay預計也將是一個挑戰。

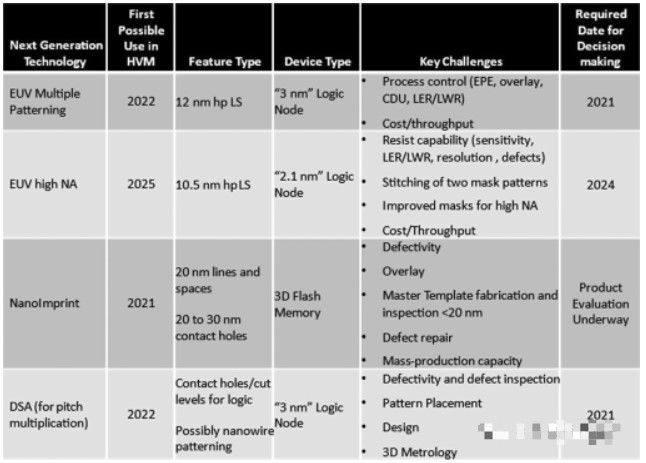

光刻路線圖的一部分是對未來挑戰潛在解決方案的描述。

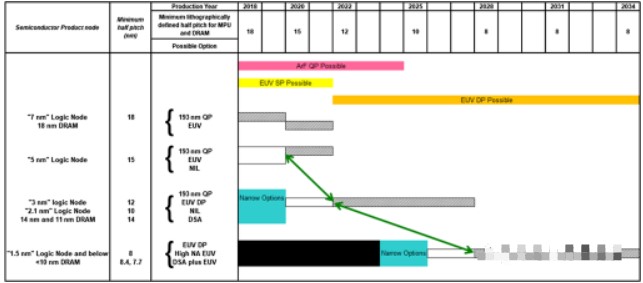

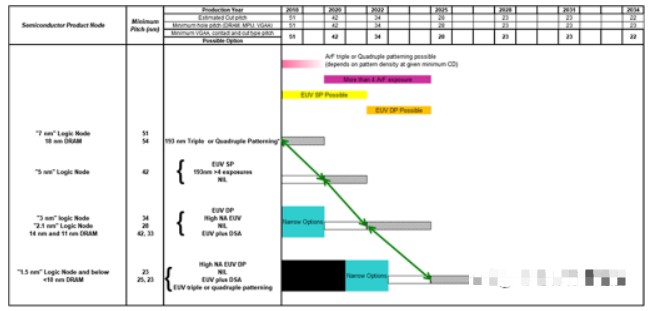

圖3和圖4分別顯示了線和間隔以及接觸孔。在這些圖形中,水平方向是時間,也是需要圖案的最小CD。這些行反映了不同邏輯和存儲芯片的節點。灰色條表示節點預計何時投入生產。白色條形表示已選擇并正在實施的模式選項,但尚未投入生產的時間段。在這種實現之前的時間段內,芯片生產商必須從有限的可能性集合中選擇要使用的模式選項,這被稱為“窄選項”。

Line and space potential solutions.

Contact hole potential solutions

對于線和間隔,EUV雙圖案可以為任何未來預計的臨界尺寸提供足夠的分辨率,雖然最終可能不是首選的解決方案。對于接觸孔和其他孔型圖案,NA=0.33的EUV雙圖案可能不能提供足夠的分辨率,需要新的解決方案,High NA和EUV雙圖案是一個潛在的解決方案。

隨機性(Stochastics)指的是成像過程中組件的隨機變化,可以認為是噪聲。成像中的噪聲有多種來源,其中最主要的是由于光子噪聲引起的空間圖像的隨機變化,以及由于構成光刻膠的化學成分的數量和位置的隨機性而引起的化學變化。

在EUV中,二次電子的產生和傳播也存在噪聲,而二次電子驅動了EUV光刻膠中的輻射化學。這些噪聲因素通過影響線邊緣粗糙度(LER:line edge roughness )、線寬度粗糙度(LWR:line width roughness )和臨界尺寸均勻性(CDU:critical dimension uniformity )來影響圖案質量。

在EUV中,噪聲也會導致某些類型的缺陷,如missing contacts 、line opens 以及 bridges。LER、LWR和CDU的要求隨著分辨率的變化而變化,因此當尺寸變小時,這些要求就會變得更嚴格。

隨機變化與臨界維度的縮放方式不同,因此它們的顯著性隨著臨界維度的減小而增,這是一個光刻界一直在努力解決的矛盾。EUV的出現帶來了噪聲問題。對于給定的曝光能量(以單位面積能量衡量),不僅光子少14倍,而且印刷特征尺寸大約比ARF浸沒小兩倍或更多倍,導致對所有噪聲源更敏感,噪聲限制了EUV可以打印的最小特征尺寸。

噪聲的一個控制因素是光刻膠的”印刷“劑量。較慢的光刻膠往往比較快的光刻膠顯示出更少的噪聲,但光刻膠越慢,EUV曝光通量越差。EUV曝光工具的成本遠遠超過一億美元,因此這些工具的高效使用和快速吞吐量非常重要。如果未來對低噪聲成像的需求迫使使用慢速EUV光刻膠,這可能會影響半導體產業沿著IRDS路線圖發展的進展。對于2020年IRDS路線圖,光刻團隊進行了縮放計算,以預測作為關鍵尺寸函數的預期打印劑量。

我們對于噪聲問題的代理(proxy)是接觸孔印刷的預期CDU。光子統計量(photon statistics)、電子統計量(electron statistics)或接觸小孔的化學變化(chemical variation)應該直接轉化為CD變化。

我們計算的起點是“7nm”邏輯節點,對于某些關鍵級別,該節點正在使用EUV進行批量生產。我們假設生產該節點的晶圓廠使用最快的EUV光刻膠,仍然給出可接受的缺陷和噪聲水平。路線圖顯示了每個節點所需的最小接觸孔尺寸和最小目標CDU。我們將使用CDU規格用于印刷CD 15%的接觸孔,對于3.82nm的7nm接觸孔尺寸來說,這給出了預期的3σ變化。較小的CDU將需要相應較小的CDU,在其他條件相同的情況下,將強制使用較慢的光刻膠。假設使用類似的單次曝光光刻膠工藝來印刷所討論的所有CD,通過計算必須改變多少光刻膠的光刻速度才能提供這種較低的CDU,我們可以預測未來所需的光刻速度。

可以認為CD變化主要來自兩個來源:曝光中光子的散粒噪聲(shot noise)和光刻膠中發生的所有化學和電子相關過程的變化。散粒噪聲將與要打印的劑量的平方根成比例。如果所有的CDU變化僅來自于該因素,則每次目標CD收縮30%時,印刷劑量將必須加倍,才能讓接觸孔CD變化對新節點和舊節點的比例相同。

另一方面,如果所有的CDU都是由隨機光刻膠(random resist)工藝引起的,則光刻膠必須在每個節點上提高20%到30%,才能將CDU降低到目標水平。這兩種限制情況都不現實,因為已知光刻膠特征尺寸變化來自這兩個來源。最好的辦法就是將每個變化源(source of variation)的影響分開,分別預測每個變化源的改進,并將各個變化元分別組合起來,以預測整體的光速變化。然而,我們無法找到適合此任務的令人滿意的噪聲源分類,因此我們使用了不同的方法。

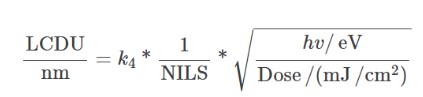

這個K4局部臨界尺寸均勻性(LCDU:local critical dimension uniformity)的方程于2019年由GEH引入,它將LCDU計算為通過normalized image log slope(NILS)測量的空間圖像質量、打印劑量、用于成像的光子能量和無量綱因子的函數。K4:

這個K4因子以與瑞利相同的方式測量用于使接觸孔成像的工藝和光刻膠的質量K1因子表征給定光刻膠和工藝的分辨率。光子能量由用于所討論的工藝的波長設置,因此對于我們的目的,它是一個常數,因為EUV光刻假設用于所有曝光。NILS受曝光工具因素(如NA、像差(aberrations)和光斑(flare))、使用的照明條件、特征尺寸和掩模效應的影響。我們選擇預測NILS從節點到節點大致恒定,值為2.5。這等同于假設曝光工具、掩模版、工藝和設計改進將以足以補償由于較小的特征尺寸,而導致NILS損失速率額(at a rate sufficient to compensate)發生,并且意味著從節點到節點成像的顯著改進。

如下文所述,我們使用這些假設來預測用于印刷臨界尺寸的EUV光刻膠的未來印刷劑量。我們在2020年的SPIE微光刻會議上介紹了這項工作。在同一次會議上,對K4介紹了配方。在修訂后的公式中,有一個新的術語[e(√2πσ/P)2]如下面的等式所示,添加了包含光刻膠的blur(σ)和 pitch(P)為LWR測量的特征。

這個新等式調整了K4觀察到光刻膠是圖案間距的函數。

這個新的因素“模糊間距“(blur pitch)是必要的,因為resist blur影響光刻膠中圖像的有效NILS。在原來那個K4等式,相同的光刻膠以不同的節距印刷將給出不同的K4數值。利用修正后的方程,K4通過間距(pitch)是恒定的。

然而,在我們對印刷的EUV劑量的預測中,隱含的是,不同的光刻膠將用于每個節點和每個臨界尺寸,并且還隱含了,光刻膠將針對被印刷的特定尺寸進行優化。當臨界尺寸縮小時,最佳resist blur也將縮小。用于反應擴散的最佳resist blur被報告為半節距CD的35%,這意味著用于每個CD的優化光刻機將具有恒定的比率σ向P。按比例減少blur并不是微不足道的,諸如二次電子blur的因素必須與諸如acid diffusion等傳統因素一起解決。

從歷史上看,光刻膠開發人員已經根據需要減少了Blur,我們假設他們未來將繼續這樣做,雖然這并不是必然的,前面的等式中的blur間距因子將是常數。原來的K4,假設resist blur對于每個連續的臨界尺寸被優化,等式表現出了用于外推到印刷劑量的適當縮放。注意,該方法假設由于隨機效應導致的CD控制的損失是選擇光刻膠的限制因素。但是隨機效應也會產生不想要的缺陷,例如缺失或合并的接觸孔。據報道,這類缺陷比簡單地使用其平均值和標準偏差來推斷CD分布更常見。了解這類缺陷形成對光刻速度和良率的影響是下一個路線圖的工作。

估計未來多久K4能夠得到改善,我們轉向歷史數據抵抗改善。2002年,Dammel17回顧了歷史上的光刻膠分辨率改進,并將這些改進轉化為等效K1改進。他發現I線和KrF光刻膠的分辨率每年都有一致的改善,并且改善率相似。假設邏輯節點間隔2年,每年的分辨率改進轉化為每個邏輯節點6%的改進。

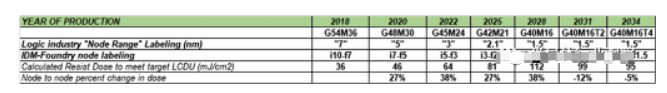

對給定光刻膠改進的預測,我們對恒定NILS的預測以及路線圖對LCDU的要求,然后可以計算將使K4方程工作。插入NILs的值,K4,和7nm節點,LCDU目標到公式中K4給出打印的標稱劑量36mj/cm2對于7nm臨界尺寸的接觸孔。使用6%的改進K4對于每個連續的未來節點,并且使用目標LCDU給出了要為每個未來節點打印的預計劑量。每個邏輯節點的計劃打印劑量如圖所示。以及與前一節點相比,打印每個節點的劑量增加的百分比。每個邏輯節點的計劃打印劑量如圖所示。以及與前一節點相比,打印每個節點的劑量增加的百分比,結果如圖所示。請注意,預計印刷劑量在2031年開始下降,因為邏輯切換到3D堆疊,關鍵尺寸不再縮小,但預計光刻膠將繼續改善。

EUV dose to print roadmap

EUV dose to print versus critical dimension.

打印的劑量預計將上升到100mj/cm2,該預測與最近的EUV光刻膠化學的隨機模擬一致。這些模擬包括electron blur,并且他們預測,除非印刷劑量結束,否則掛你科教成分因素的任何組合都不會導致GIA感冒了快哦阿婆在沒有不可接受的缺陷水平的情況下,成像10nm線和間隔100mj/cm2。我們宏觀尺度的匹配K4基于該文獻詳細的物理特性,可以確信每個節點6%的改進是可以實現的。

靈敏度分析表明,如果啟動K4對于7nm邏輯節點假設的值或起始NILS值是變化的,則對于7nm節點圖案的印刷劑量將變化,但是從節點到節點的印刷劑量的百分比增加將是相同的。然而,印刷劑量的增加速率對光刻膠的改善靈敏度,如通過K4.圖7顯示了不同改善率的預期打印劑量與節點的函數關系。

Increase in dose to print for different rates ofk4k4improvement.

如果光刻膠隨機性不隨光刻膠優化而改善,那么印刷的光刻膠劑量將在5個節點上增加五倍。如果光刻膠隨機性改善這么多K4,每個節點都能提高15%,在相同的五個節點上,打印劑量增加不到50%。考慮到這種對光刻膠隨機改進速率的巨大依賴性,未來或許可能使改進慢于或快于公布的路線圖,估計每個節點提升6%的因素是有用的。

在已發表的關于EUV光刻膠改進的研究中,一些研究顯示每年的改進非常小。(參考文獻顯示新光刻膠落在與舊光刻膠相同的LER感光速度曲線上)。新光刻膠沿著印刷劑量和線粗糙度之間的現有平衡下降。但是最近的一些論文已經顯示了用于特定應用或特定成像條件的光刻膠有了很大的改進。這種二分法的一部分可能是因為在當前使用的兩類EUV光刻膠中,存在大部分或全部使用有機化學的化學放大光刻膠,并且大部分使用金屬氧化物作為關鍵EUV成像組分的無機光刻膠。

化學放大系統的工作原理在應用于KrF和ARF成像時已得到很好的確立,基于已經為ARF應用中隨機性優化的成熟機制,很難期望光刻膠可以得到快速改進。有些人可能會爭辯說,噪聲的來源是眾所周知的,并且可以實現的LWR、LER或CDU有一個下限。

無機光刻膠是一類新的光刻膠,不限制于以前的波長,因此可以預期,它們將比EUV化學放大光刻膠改進得更快,用于EUV的基于金屬的光刻膠在性能上已經與傳統的化學放大光刻膠相匹配。然而,無機光刻膠僅在 negative tone中可用,在某些應用中比基于有機的化學放大光刻膠具有優勢。

這里描述的方法是高層次的,并不考慮如何進行實際改進的細節。例如,它不考慮光刻膠中的具體問題,比如電子模糊或競爭EUV引起的反應;也不考慮替代工藝,比如,能讓低EUV劑量打印成為可能的缺陷DSA修復。這是基于我們對過去技術進步的理解而做出的推斷,它顯示了存在哪些挑戰,但沒有給出解決這些挑戰的解決方案。從歷史上看,這個行業過去在創新和增量改進方面都遇到了困難的挑戰,整個光刻委員會都希望這種情況在未來繼續發生。

IRDS認為在K4上6%的改善也將代表光刻膠改進的相當大的速率。但是,最終這個6%的數值是一個專家委員會對未來的預測,而不是一個通過實驗確定的數字。

由于吞吐量的減少,以及曝光工具成本的增加,預計印刷劑量的增加將給EUV用戶帶來很大的成本。一種替代方案是使用EUV雙重曝光,這將增加光刻成本,但由于光刻膠中較大的印刷尺寸而提供改進的隨機性。比較EUV應用的單次曝光和兩次曝光的研究已經在進行中。

另一種策略是接受不良的隨機因素,但找到提高圖案質量的工藝替代方案。雙重圖案化是一種這樣的工藝,定向自組裝也顯示出能夠使用快得多的光刻膠的潛力。(一篇由G. Singh, E. Han和F. Gstrein在2020年SPIE微光刻大會上發表的論文“用DSA使摩爾定律生效”。遺憾的是,沒有會議記錄文件。2021年,參考文獻提交了一份后續論文。)。或許能對流程改進有所幫助。工藝改進的一個例子,就是印刷比所需更大的通孔以獲得更少的CDU,然后通過蝕刻或一些其他工藝來縮小它們,還可能出現新的光刻膠類型和工藝。最近報道了關于干沉積和顯影光刻膠的工作,但是沒有足夠的公開數據來比較它們與當前材料的隨機性。

除了與噪聲相關的模式質量之外,還有其他挑戰。Edge placement error(EPE)是未來節點面臨的主要挑戰,對EPE的要求是最終特征尺寸的函數,并且EPE要求隨著CD變小而縮小。放寬印刷CD要求的工藝,如雙重圖案,通常會使EPE變得更糟糕。隨著印刷特征尺寸的減小,保持可接受的NILS將需要改進掩模、曝光工具和源掩模優化,以及可能的芯片設計變化,更容易成像。NA為0.55的,更高NA的EUV曝光工具預計將在2023年或2024年推出。與較低NA成像相比,這些較高NA工具將改善特定特征尺寸的NILS,這些工具將具有當前工具的一半曝光區域大小,并且對于某些產品設計可能需要區域縫合。它們將需要改進的掩模版。由于對聚焦敏感的EPE,曝光工具中較高的照明和成像角度可減小聚焦深度,并且還減小圖像對比度,但這些挑戰的解決方案尚未展示。

當前行業正在積極研究替代印刷技術,如納米壓印、定向自組裝和直接寫入。納米壓印已經顯示出實質性的最新進展,但沒有展現出用于批量存儲芯片生產的足夠的生產率,也沒有顯示出足夠低的缺陷水平來考慮用于前沿邏輯應用。它還需要在用于邏輯的覆蓋方面進行改進,但定向自組裝仍未在批量生產中得到證實。雖直接寫入對于高容量芯片生產沒有足夠的吞吐量,但對于不需要前沿尺寸的低容量生產具有優勢。最近的論文描述了正在開發的新的直接寫入工具。

從長遠來看,當邏輯開始垂直發展而不是縮小關鍵尺寸時,良率和工藝復雜性將成為關鍵挑戰。路線圖預測,3D邏輯將在2031年投入生產,但解決其挑戰和開發此類設備必須比這早得多,2021年光刻困難挑戰如圖所示。

IRDS 2021 lithography difficult challenges.

IRD路線圖預測,未來半導體面臨的挑戰以及應對這些挑戰的可能解決方案。它表明,在未來大約10年內,邏輯器件將推動關鍵尺寸的縮小和圖案化的改進。之后,邏輯將切換到垂直縮放。IRDS路線圖的光刻部分解決了這些圖案化挑戰,包括投影圖案要求和可能的圖案選項。一個主要的挑戰是成像中的噪聲。隨著印刷特征變得更小,對低缺陷和良好圖案質量的要求將驅動EUV印刷劑量的增加。即使假設在光刻膠、工具和其他成像基礎設施等方面有實質性的改進,打印的劑量也會超過100mj/cm2,預計將到2028年,才能沒有實施減輕噪聲影響的替代工藝或設計,這估計對預測的抵抗隨機性的改善靈敏度。即使假設隨機性被控制得,足夠好能給出足夠的LWR和CDU,其他因素,例如缺失或合并的特征,或者在減小的尺寸下不能可靠起作用,也可能是未來EUV使用的障礙。其他主要的挑戰是改進EPE,以及高NA EUV成像的開發和實施。該行業正在積極尋求替代的圖案化技術,特別是納米壓印光刻、定向自組裝和直接寫入。

從長遠來看,隨著半導體縮放改變為3D堆疊,良率和工藝復雜性將成為特定圖案化的挑戰。

審核編輯:劉清

-

芯片

+關注

關注

456文章

51170瀏覽量

427255 -

DRAM

+關注

關注

40文章

2325瀏覽量

183866

原文標題:芯片光刻路線圖

文章出處:【微信號:半導體科技評論,微信公眾號:半導體科技評論】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

未來10年智能傳感器怎么發展?美國發布最新MEMS路線圖

光刻工藝的基本知識

2024學習生成式AI的最佳路線圖

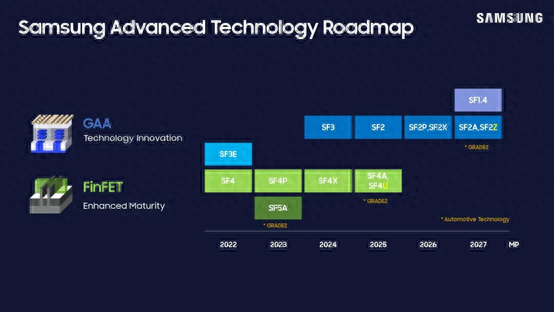

三星公布最新工藝路線圖

三星芯片制造技術路線圖出爐,意強化AI芯片代工市場競爭力

英飛凌為AI數據中心提供先進的高能效電源裝置產品路線圖

iPhone升級路線圖曝光:1年后才配12G內存,2026年有折疊屏

事關衛星物聯網!LoRaWAN 2027 發展路線圖重磅公布

有關芯片光刻路線圖的一些知識分享

有關芯片光刻路線圖的一些知識分享

評論