2014 年,賽普拉斯推出了 HyperBus 接口,該接口利用并行和串行接口存儲器的傳統(tǒng)特性,提高了系統(tǒng)性能,簡化了設(shè)計(jì),并顯著降低了成本。在支持 HyperBus 的解決方案中,HyperRAM 是一種新穎的技術(shù)解決方案,能夠?qū)崿F(xiàn)高達(dá) 333 MB/s 的吞吐量,在 HyperRAM 2.0 中增加到 400 MB/s。HyperRAM 2.0 是一種高速、低引腳數(shù)自刷新動態(tài) RAM (DRAM),專為需要擴(kuò)展內(nèi)存的高性能嵌入式系統(tǒng)而設(shè)計(jì),例如汽車、工業(yè)、消費(fèi)和物聯(lián)網(wǎng)應(yīng)用。HyperRAM 2.0 提供 HyperBus 和 Octal SPI 接口,并在 DDR 模式下提供高達(dá) 400 MBps 的讀/寫帶寬。

超內(nèi)存

通過與 Cypress 的合作,華邦電子已經(jīng)推出了 32Mb 到 512Mb 密度的產(chǎn)品。目前,車規(guī)級24BGA(6×8 mm 2)、面向消費(fèi)級可穿戴市場的WLCSP(Wafer Level Chip Scale Package)、KGD(Known Good Die)等產(chǎn)品均已上市。

除了 Cypress 之外,其他相關(guān)的領(lǐng)先 MCU 制造商,如 NXP、Renesas、ST 和 TI 都已經(jīng)開發(fā)了支持 HyperBus 接口的微控制器,并且他們的支持也有望在未來得到支持。同時,Cadence、Synopsys 和 Mobiveil 等領(lǐng)先的芯片 IP 供應(yīng)商也開始提供 HyperBus 內(nèi)存控制 IP,從而加快了包含該內(nèi)存解決方案的產(chǎn)品的上市時間。

HyperRAM 可以顯著提高終端設(shè)備的性能,其主要優(yōu)勢如下:

低功耗:此特性是通過混合睡眠模式 (HSM) 實(shí)現(xiàn)的,該模式僅消耗 45μW@1.8V 和 55μW@3V(與相同容量的待機(jī)模式 SDRAM 的 2000μW@3.3V 相比)

減少占用空間:低引腳數(shù)可以節(jié)省 PCB 上的寶貴空間

易于控制:使用較少的活動引腳,設(shè)計(jì)更簡單,而不會影響整體系統(tǒng)性能。

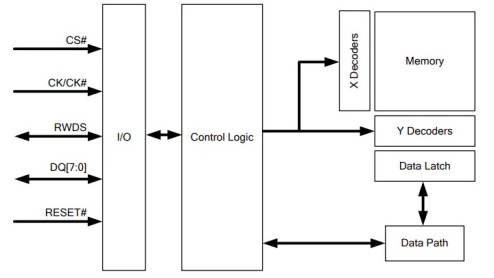

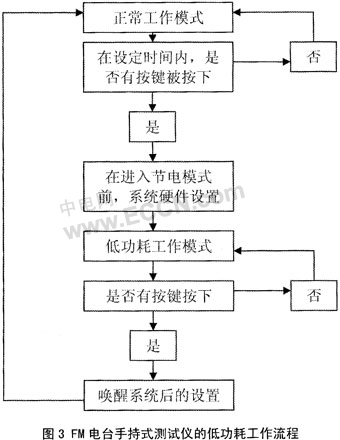

除了更高的功耗外,低功耗 SDRAM 的外形尺寸比 HyperRAM 更大,這并不使其成為應(yīng)盡可能減少占用空間和 PCB 面積的理想解決方案。如圖 1 所示,HyperRAM 接口僅需要 13 個引腳(DQ[7:0]、RWDS、CS#、RESET#、CK 和 CK#),大大簡化了 PCB 設(shè)計(jì)和封裝尺寸。反之亦然,傳統(tǒng)的 SDRAM 解決方案在 54BGA 封裝中需要 38 個引腳和 8×8 mm 2的面積,而 LP SDRAM 解決方案在 54BGA 封裝中需要 41 個引腳和 9×8 mm 2的面積。因此,在產(chǎn)品的設(shè)計(jì)階段,更多引腳可用于實(shí)現(xiàn)附加功能,從而使解決方案更具成本效益。

圖 1:華邦 HyperRAM 框圖

HyperRAM 的另一個相關(guān)特性是它是一個自刷新 RAM,這意味著它可以在完成讀/寫操作后自動返回待機(jī)模式。這可以減少系統(tǒng)設(shè)計(jì)和固件開發(fā)的工作量。

關(guān)于可以從該解決方案中受益的用例和行業(yè),它們包括所有需要低功耗和高 MCU 計(jì)算能力的應(yīng)用,例如汽車、工業(yè) 4.0、智能家居、可穿戴設(shè)備和物聯(lián)網(wǎng)設(shè)備。此外,對于智能揚(yáng)聲器和智能電表等電池供電設(shè)備,低功耗對于實(shí)現(xiàn)更長的電池壽命至關(guān)重要。

華邦 HyperRAM 是嵌入式 AI 和圖像處理分類的理想解決方案,其中設(shè)備應(yīng)盡可能小,同時提供足夠的內(nèi)存空間來支持計(jì)算密集型算法,例如人臉識別、物體檢測、實(shí)時圖像識別和邊緣計(jì)算。

“HyperRAM實(shí)際應(yīng)用案例主要有兩種:一種是精準(zhǔn)圖像識別,一種是語音識別,兩者都支持語音或圖像的AI模型”,華邦半導(dǎo)體DRAM市場經(jīng)理Jacky Tseng在接受采訪時表示。與 EEWeb。

SpiStack

SpiStack 是華邦開發(fā)的一種內(nèi)存解決方案,它是通過將一個 NOR 裸片和一個 NAND 裸片堆疊到同一個封裝中而形成的,例如一個 64Mb 串行 NOR 和一個 1Gb QspiNAND 裸片。該解決方案使設(shè)計(jì)人員能夠靈活地將代碼存儲在 NOR 裸片中,并將數(shù)據(jù)存儲在 NAND 裸片中。

通過堆疊同構(gòu)或異構(gòu)閃存模塊,SpiStack 提供了具有不同密度的各種存儲器,用于代碼和數(shù)據(jù)存儲,同時為設(shè)計(jì)人員提供最大的存儲靈活性以滿足其設(shè)計(jì)要求。SpiStack 存儲器只需要 8 個信號管腳,而與堆疊裸片的數(shù)量無關(guān)。可以通過簡單的軟件芯片選擇命令切換有源芯片,提供工廠分配的芯片 ID 號。該器件的時鐘頻率可高達(dá) 104MHz,對應(yīng)于 Quad-SPI 下的 416MHz 時鐘速率。此外,SpiStack (NOR+NAND) 支持并發(fā)操作,這意味著其中一個裸片可以被編程或擦除,而另一個裸片可以同時編程/擦除/讀取,反之亦然。例如,應(yīng)用程序可以使用 NOR 裸片(SpiFlash,它提供更好的耐用性和保持力,和快速的隨機(jī)訪問時間)用于存儲啟動代碼和應(yīng)用程序代碼,而多個大型數(shù)據(jù)(例如嵌入式 AI 和相機(jī)圖像的學(xué)習(xí)數(shù)據(jù))可以存儲在 NAND 芯片(QspiNAND)上。多個 SpiFlash 裸片,每個裸片的密度范圍從 16Mb 到 2Gb,可以與 NOR 和 NAND 裸片的任意組合堆疊。

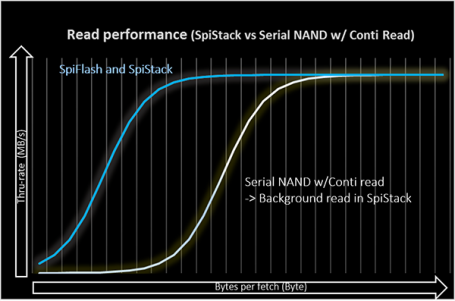

如圖 2 所示,SpiStack 提供比連續(xù)讀取的串行 NAND 更好的讀取性能。這是因?yàn)?SpiStack 支持并發(fā)操作:在一個芯片上執(zhí)行讀取操作時,可以在另一個芯片上執(zhí)行寫入/擦除操作,而不會中斷數(shù)據(jù)更新的代碼執(zhí)行。

圖 2:SpiStack 與串行 NAND(續(xù))。讀取性能

采用 SpiStack 解決方案帶來的主要好處主要有以下三個:

PCB 占用空間小:這是多個應(yīng)用的強(qiáng)制性要求,包括物聯(lián)網(wǎng)、可穿戴設(shè)備、消費(fèi)類和醫(yī)療設(shè)備

成本效益:SpiStack 解決方案允許減少組件數(shù)量和引腳數(shù)量,簡化 PCB 布局和布線

高靈活性:NOR 和 NAND die 的尺寸可以組合以滿足特定的應(yīng)用需求。SpiFlash NOR 閃存提供 16Mb、32Mb、64Mb、128Mb 和 256Mb 大小,而 QspiNAND 提供 512Mb、1Gb 和 2Gb 大小。

“我們解決方案的第一個好處是它可以提供更小的外形尺寸,這對于物聯(lián)網(wǎng)等應(yīng)用至關(guān)重要。第二個是成本,可以通過將兩個內(nèi)存芯片放在同一個芯片組中來降低成本。第三個好處是客戶可以選擇任何可用密度的 NOR 和 NAND 裸片”,華邦閃存營銷經(jīng)理 Wilson Huang 說。

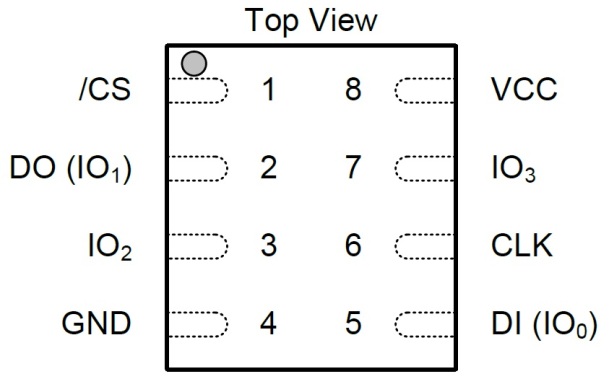

此外,通過將兩個芯片集成在一個封裝中可以降低制造成本,并且通過使用標(biāo)準(zhǔn)封裝,即 8 焊盤 WSON 8mmx6mm 封裝來保持硬件兼容性(見圖 3)。

圖 3:SpiStack WSON 包

“我們提供高質(zhì)量的產(chǎn)品,因?yàn)槲覀冎皇褂贸墒炜煽康募夹g(shù)(46nm NAND 和 58nm NOR)。因此,質(zhì)量非常好,我們的客戶不需要擔(dān)心質(zhì)量”,華邦的演講者總結(jié)道。

審核編輯 黃昊宇

-

嵌入式

+關(guān)注

關(guān)注

5092文章

19177瀏覽量

307647 -

NAND

+關(guān)注

關(guān)注

16文章

1690瀏覽量

136459 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3055瀏覽量

74327 -

HyperRAM?

+關(guān)注

關(guān)注

0文章

4瀏覽量

6076

發(fā)布評論請先 登錄

相關(guān)推薦

嵌入式系統(tǒng):測試和測量挑戰(zhàn)入門手冊

嵌入式系統(tǒng)中的低功耗設(shè)計(jì)

基于嵌入式DSP系統(tǒng)的低功耗優(yōu)化設(shè)計(jì)

通用AC輸入70W緊湊型音頻電源解決方案

基于ARM的緊湊型圖像采集系統(tǒng)設(shè)計(jì)

嵌入式系統(tǒng)內(nèi)存管理方案研究

基于μCOS-II嵌入式系統(tǒng)的低功耗開發(fā)

嵌入式系統(tǒng)設(shè)計(jì)中的低功耗技術(shù)

嵌入式系統(tǒng)的組成及其低功耗的設(shè)計(jì)

嵌入式AI解決方案中內(nèi)存驅(qū)動的設(shè)計(jì)介紹

嵌入式Linux的低功耗策略

低功耗嵌入式計(jì)算解決方案:選擇處理器的幾個關(guān)鍵因素

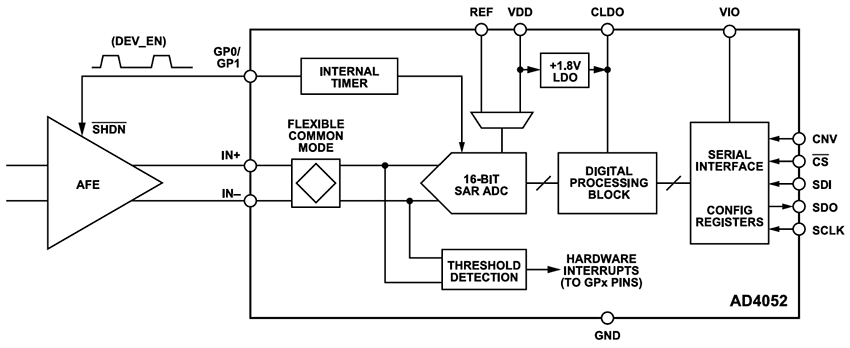

AD4052緊湊型低功耗Easy Drive SAR ADC

Neousys宸曜發(fā)布Alder Lake N緊湊型可擴(kuò)展嵌入式計(jì)算平臺

低功耗和緊湊型解決方案滿足嵌入式系統(tǒng)內(nèi)存要求

低功耗和緊湊型解決方案滿足嵌入式系統(tǒng)內(nèi)存要求

評論