多年來,功率 MOSFET 一直是大功率應(yīng)用的支柱,可靠地提供大電流。然而,隨著電源應(yīng)用技術(shù)的進(jìn)步,需要極高水平的電流。這些應(yīng)用已經(jīng)達(dá)到了實(shí)現(xiàn)一個 MOSFET 不再足夠的功率水平要求,迫使設(shè)計(jì)人員求助于并聯(lián)放置 MOSFET。

并聯(lián)MOSFET的問題及解決方案

為了實(shí)現(xiàn)良好的并聯(lián)設(shè)計(jì),傳統(tǒng)上選擇 MOSFET——通過篩選——基于它們的閾值電壓相似,以確保它們同時(shí)導(dǎo)通。然而,屏蔽 MOSFET 會增加成本和復(fù)雜性,并且仍然容易受到溫度不穩(wěn)定性的影響。因此,考慮到上述問題,專用 MOSFET 技術(shù)可以在并聯(lián)應(yīng)用中提供更好的解決方案,而無需額外的篩選過程。

均流與 MOSFET 中的兩種主要模式相關(guān):動態(tài)(即開關(guān)轉(zhuǎn)換)和穩(wěn)態(tài)/傳導(dǎo)(即通過導(dǎo)通電阻)。對于 MOSFET 而言,穩(wěn)態(tài)期間的均流本質(zhì)上是穩(wěn)定的,不在本文討論范圍內(nèi);本說明的重點(diǎn)是動態(tài)期間的電流共享。在切換期間,重要的是并聯(lián)設(shè)備同時(shí)開啟。在其中一個并聯(lián) MOSFET 比另一個更早開啟的情況下,該設(shè)備將傳導(dǎo)完整的系統(tǒng)電流,直到其他設(shè)備開啟,使其面臨磨損和潛在故障的風(fēng)??險(xiǎn)。MOSFET 在不同時(shí)間的導(dǎo)通是由于 V GS的自然擴(kuò)散閾值電壓。無論制造商或技術(shù)如何,都不能保證兩個 MOSFET 具有相同的閾值電壓。為了克服這個問題,設(shè)計(jì)人員通常采用一種解決方案,通過匹配的閾值電壓篩選和選擇 MOSFET,縮小值的范圍。這需要額外的制造過程,這會增加成本和復(fù)雜性。

V GS閾值電壓的匹配是一種有效的方法,但并不能解決與作為參數(shù)的 V GS相關(guān)的所有問題。閾值電壓與溫度有關(guān)并具有負(fù)溫度系數(shù),這意味著如果溫度升高,器件閾值電壓電平會下降。如果器件在不同溫度下運(yùn)行,它們的 V th差異會更大。這是因?yàn)檩^熱的器件由于溫度不匹配而使其 V th電平下降,從而提前開啟。因此,在理想制造環(huán)境中被認(rèn)為匹配的設(shè)備在實(shí)際應(yīng)用中不一定保持匹配。這種效果如圖 1 和圖 2 所示。

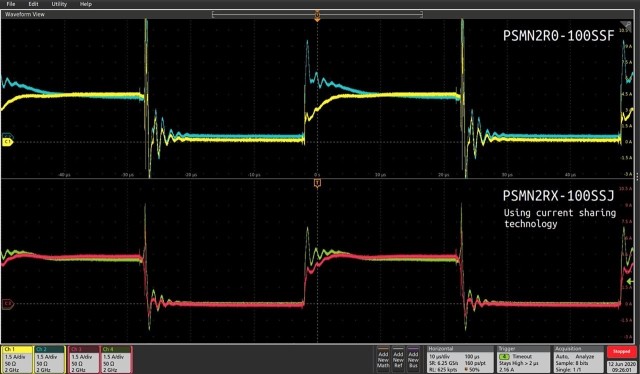

圖 1:比較低溫下的常規(guī)與均流技術(shù)

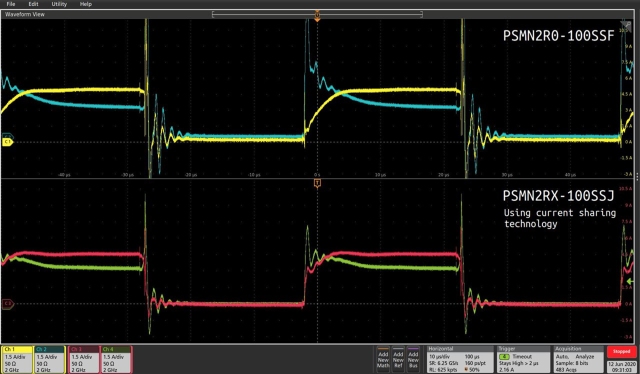

圖 2:在加熱時(shí)比較常規(guī)與均流技術(shù)

溫度均流

圖 1 和圖 2 顯示了在并聯(lián)應(yīng)用中測量的結(jié)果。在圖 1 中,頂部的兩條軌跡,藍(lán)色和黃色,是兩條PSMN2R0-100SSF [i]使用常規(guī)技術(shù)的設(shè)備,其閾值電壓之間有 0.5V 的差值。底部的兩條跡線(綠色和紅色)是采用 Nexperia 均流技術(shù)的器件,其閾值電壓范圍為 0.5V。使用常規(guī)技術(shù)和 Nexperia 均流技術(shù)的測試具有相同的電路設(shè)計(jì),以相同的頻率驅(qū)動相同的感性負(fù)載。對于常規(guī)和均流技術(shù),在相同時(shí)間、溫度和速率(分別為藍(lán)色和綠色跡線)的情況下,以較低閾值電壓對器件施加熱量。比較圖 2 和圖 1 可以看出,與 Nexperia 均流技術(shù)相比,常規(guī)技術(shù)在溫度方面并不穩(wěn)定。這背后的原因是 Nexperia 均流技術(shù)不依賴于閾值電壓來保持匹配以均勻分流。這很重要,因?yàn)楝F(xiàn)實(shí)生活中的應(yīng)用可能不一定會在 PCB 上的所有并聯(lián) MOSFET 上實(shí)現(xiàn)均勻的溫度。因此,在制造環(huán)境中篩選和匹配的設(shè)備可能無法在實(shí)際應(yīng)用中保持匹配。

較高電流下的均流

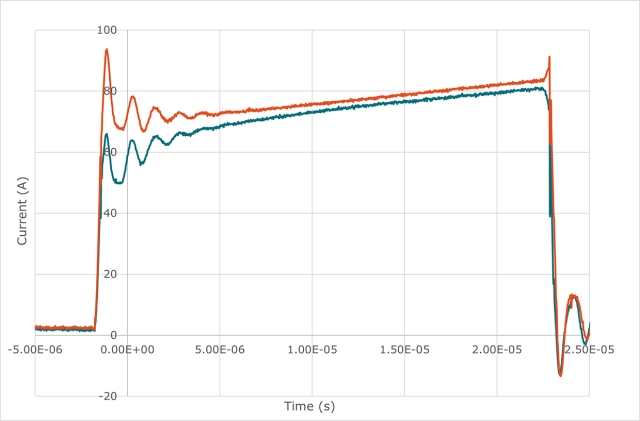

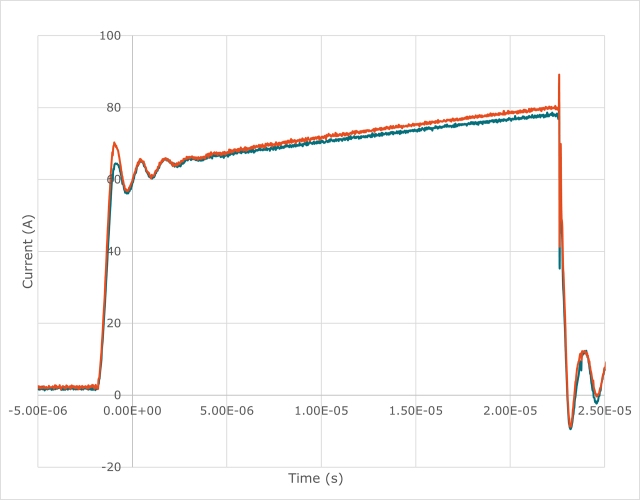

與前面提到的制造篩選工藝方法相比,Nexperia 均流技術(shù)解決了在技術(shù)本身內(nèi)實(shí)現(xiàn)更均等的均流問題。使用具有 Nexperia 均流技術(shù)的 MOSFET 意味著設(shè)計(jì)工程師不再需要依賴 V th參數(shù)匹配。該技術(shù)在溫度下保持穩(wěn)定,并提供更好的均流性能,如圖 3 和圖 4 所示,與 Nexperia 電流相比,選擇了閾值電壓范圍為 0.5V 的常規(guī)技術(shù)的真實(shí)測量結(jié)果-共享技術(shù)也具有相同的 0.5-V 閾值電壓分布。通過將來自每種技術(shù)的兩個設(shè)備放置在同一塊板上,以相同的頻率驅(qū)動相同的感性負(fù)載并捕獲流過它們的電流來捕獲結(jié)果。在這個例子中,每個設(shè)備在 20 kHz 下開關(guān)的電流大約為 75 A。但是,常規(guī)技術(shù)并聯(lián)設(shè)備之間的峰值電流差異超過 30 A,而 Nexperia 均流技術(shù)僅相差 5 A。

圖 3:閾值電壓范圍為 0.5V 的常規(guī)技術(shù)

圖 4:Nexperia 均流技術(shù),閾值電壓分布為 0.5V

值得指出的是,與圖 4 相比,常規(guī)技術(shù)需要大約 5 μs 才能開始更均等地共享電流,其中設(shè)備在不到 0.5 μs 內(nèi)開始均等共享。對于常規(guī)技術(shù),具有較低 V th的設(shè)備將增加應(yīng)力,增加磨損和故障風(fēng)險(xiǎn)。進(jìn)行的進(jìn)一步測試(此處未顯示)表明均流的動態(tài)響應(yīng)是恒定的,這意味著如果頻率增加,動態(tài)響應(yīng)仍將相同。因此,Nexperia 均流技術(shù)也有利于以更高頻率進(jìn)行切換的應(yīng)用。

結(jié)論

如實(shí)際實(shí)驗(yàn)室測量所示,Nexperia 均流技術(shù)為并行 MOSFET 設(shè)計(jì)應(yīng)用帶來明顯優(yōu)勢。它提供了一種不需要基于V th進(jìn)行篩選,也不依賴于V th來實(shí)現(xiàn)更均等的均流的技術(shù)解決方案。該技術(shù)解決了在較高電流下均流的問題,并且對整個 PCB 的溫度變化具有彈性——正如實(shí)際應(yīng)用中所經(jīng)歷的那樣。

審核編輯:劉清

-

MOSFET

+關(guān)注

關(guān)注

147文章

7242瀏覽量

214273 -

導(dǎo)通電阻

+關(guān)注

關(guān)注

0文章

350瀏覽量

19865 -

電壓電平

+關(guān)注

關(guān)注

0文章

26瀏覽量

7539

發(fā)布評論請先 登錄

相關(guān)推薦

碳化硅(SiC)MOSFET并聯(lián)應(yīng)用均流控制技術(shù)的綜述

UPS電源“十全十測”之9:UPS并機(jī)均流性能測試

MOSFET并聯(lián)在高功率設(shè)計(jì)中的應(yīng)用

AOS MOSFET并聯(lián)在高功率設(shè)計(jì)中的應(yīng)用

N+1熱插拔電源模塊并聯(lián)均流系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

使用DRV3255-Q1驅(qū)動并聯(lián)MOSFET

成功并聯(lián)功率MOSFET的技巧

PCIM2024論文摘要|并聯(lián)SiC MOSFET的均流研究

并聯(lián)MOSFET應(yīng)用中的均流技術(shù)

并聯(lián)MOSFET應(yīng)用中的均流技術(shù)

評論