之前有朋友問我怎么用腳本產生一個驗證環境,這個問題今天和大家介紹下兩種做法。

第一種用VCS自帶的uvmgen工具

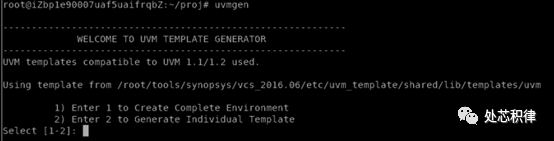

當你在命令行時直接輸入uvmgen會輸出如下信息

選擇1

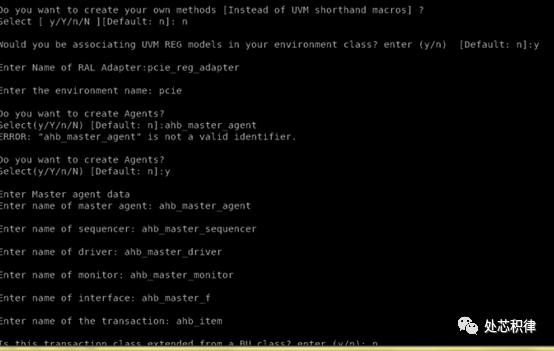

然后按照提示步驟進行UVM環境的創建

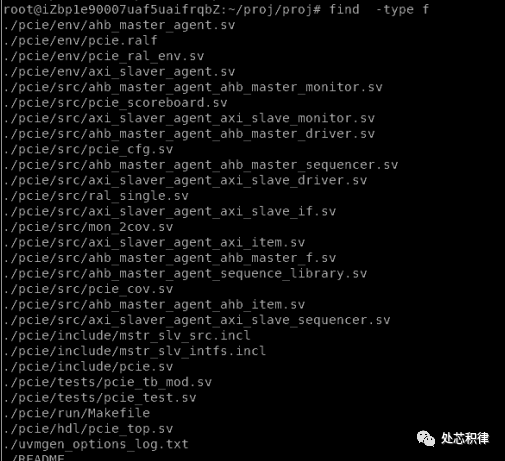

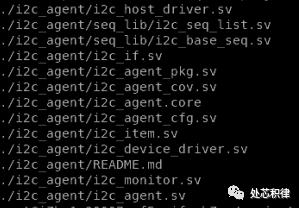

創建完之后我們看看環境目錄

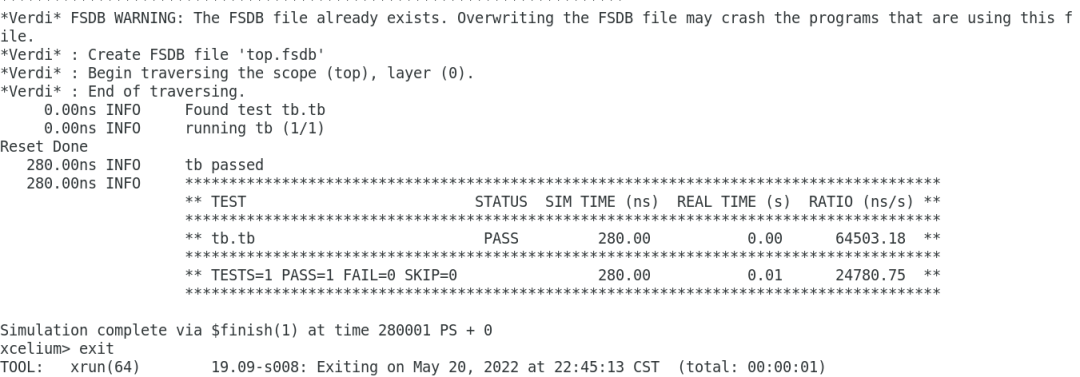

剛才我們創建的env,agent,scoreboar,coverage收集模塊等都已經完備,跑環境的Makefile也都自動生成好了。對于一些簡單的UVM環境,用uvmgen還是非常適用的。

但是采用這種方式產生UVM環境的局限也比較明顯,比如agent不能添加多個等,對于一些復雜的驗證環境還得自己手動添加。有沒有一種腳本能夠將整體框架大家好,甚至將驗證管理中的checklist都準備妥當。下面介紹的這個uvmdvgen.py 腳本將實現這些強大的功能。

介紹下這個腳本實現的功能

可以快速生成 agent;

能夠根據用戶需求產生UVM環境;

自帶checklist;

自帶testplan;

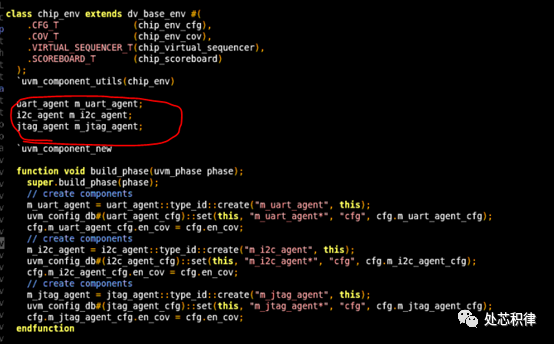

這里產生的UVM環境可以支持多個不同的agent,并且UVM環境的編碼風格對復用性非常友好。讓我們看看這款UVM的腳本是怎么使用的。

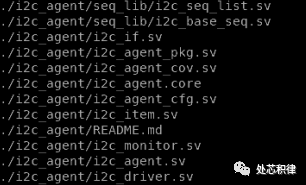

用-a 單獨生成一個agent,例如

uvmdvgen.py i2c -a

生成i2c 的agent

用-s 可以一個agent里面增添 host driver 和device driver

uvmdvgen.py i2c -a -s

講完agent,開始講environment,用-e 產出UVMenvironment

uvmdvgen.py i2c -e

Checklist,Testplan,UVMenvironment 一應俱全。

用-ea添加agent,可以隨便添加多少個agent

uvmdvgen.py chip -e-ea uart i2c jtag

如此在environment添加agent便完成了。

該腳本還可以用-hi和-hr實現是否有interrupt,register model等功能。

是不是功能超級強大,迫不及待想用這個腳本的小伙伴可以在下面鏈接獲取。

-

編碼

+關注

關注

6文章

957瀏覽量

54953 -

UVM

+關注

關注

0文章

182瀏覽量

19228 -

腳本

+關注

關注

1文章

392瀏覽量

14938

原文標題:如何自動產生一個UVM環境

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一個優秀的SOC驗證環境應該具備哪些功能呢

SoC驗證環境搭建方法的研究

參數化UVM IP驗證環境(上)

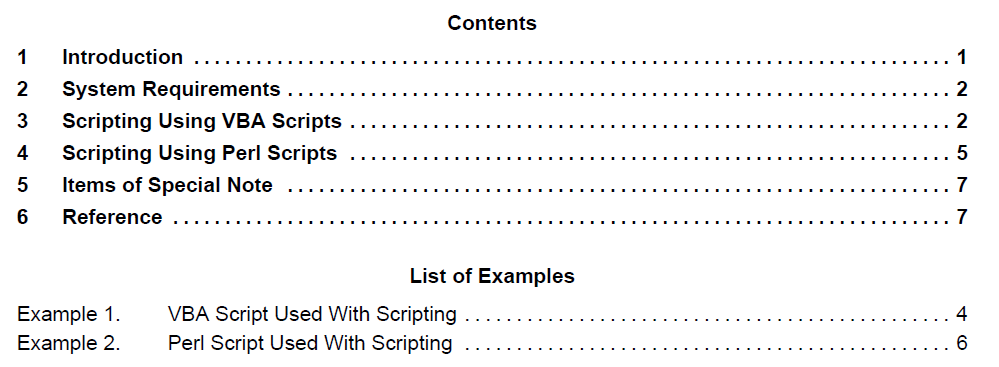

如何在代碼編寫器StudioIDE開發環境中使用腳本實用程序的詳細描寫

來練習一個寫Redis部署的腳本

通過一個腳本搞懂fork、source和exec

Bash腳本中特殊變量$0是什么?

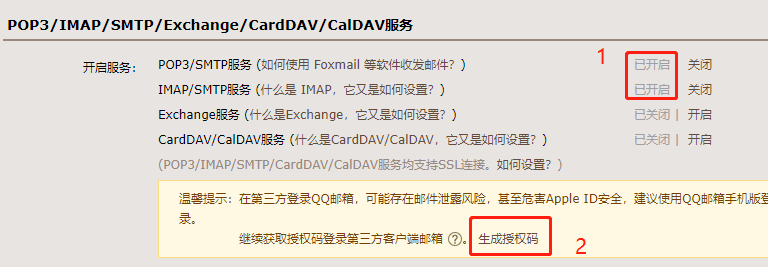

怎么用Python構建一個自動發送郵件的腳本

怎么用Python構建一個自動發送郵件的腳本

怎么用腳本產生一個驗證環境

怎么用腳本產生一個驗證環境

評論