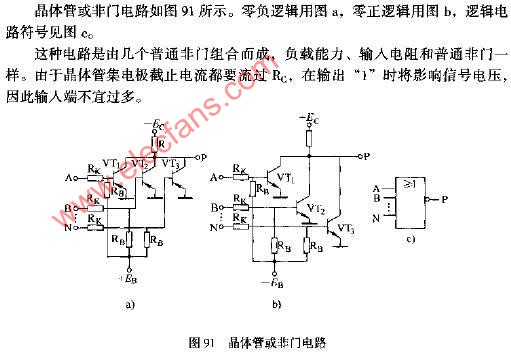

或非門(NOR Gate)是邏輯門,也是通用門之一,用于構造類似于AND Gate的基本門。通過組合非門和或門,可以構造或非門。或非門的輸出是或門的反轉。通常情況下,或非門有2個輸入,比如X和Y,以及一個輸出Z。

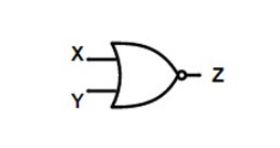

或非門邏輯符號如下圖所示:

或非門運算的邏輯數學表達式為 Z =(X+Y) ?。其中, ?表示反向運算。

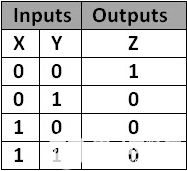

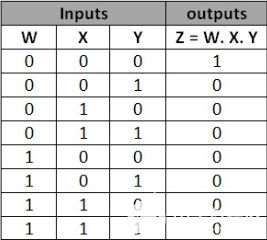

另外,或非門的真值表如下圖所示,它表明如果兩個輸入都處于低邏輯電平,則或非門輸出邏輯高值。如果其任何輸入處于高邏輯電平,則會產生邏輯低值。

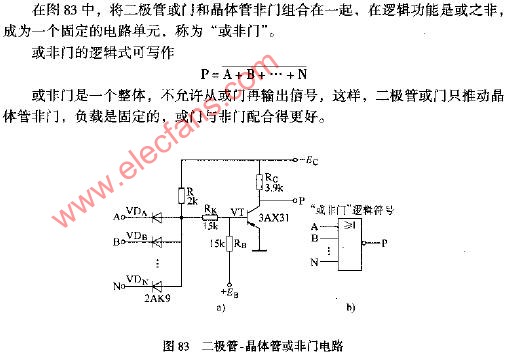

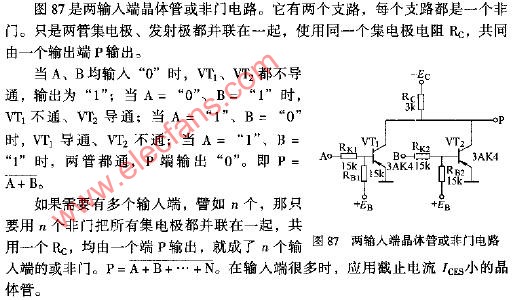

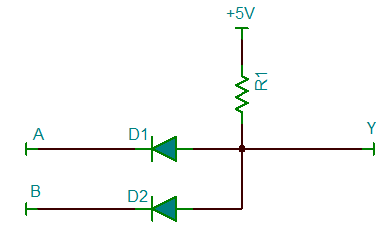

使用輸入晶體管設計的或非門

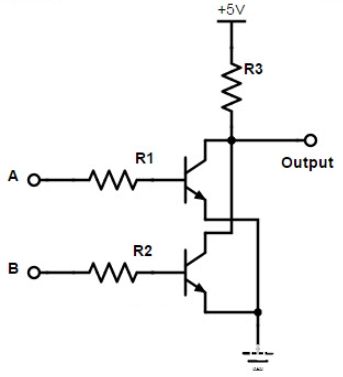

在兩個輸入或非門中,兩個晶體管用于設計一個或非門。+6伏的電路驅動電壓連接到第一個晶體管的集電極。相同的電源電壓也將并聯到第二個晶體管的集電極。連接兩個電阻作為或非門的輸入(每個10K)。兩個晶體管的發射極共同接地。輸出在電源電壓、電阻和第一個晶體管的集電極節點處收集。

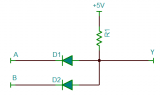

使用兩個晶體管設計的2輸入或非門邏輯門如下圖所示:

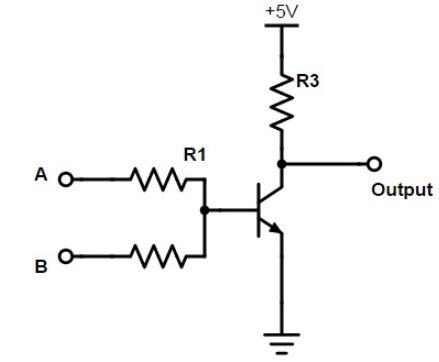

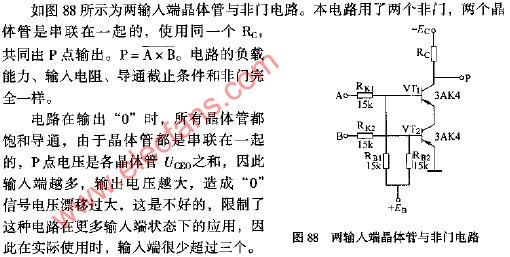

此外,或非門還有另一種設計方法,即單晶體管設計的或非門。在這里,晶體管的基極通過電阻為并聯的兩個輸入供電。發射極接地,集電極連接到+6伏的電路驅動電壓(電源電壓)。輸出在晶體管的集電極端收集,如下圖所示:

上圖是實現NOR邏輯門的另一種方法。

或非門的脈沖操作

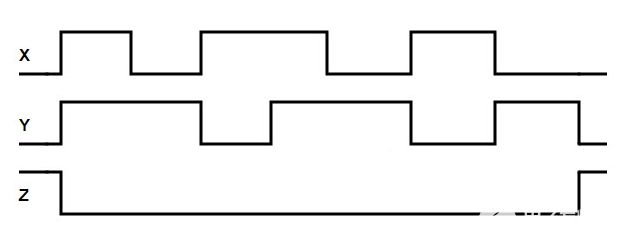

如果應用2個不同的時鐘信號作為或非門X和Y的輸入,那么或非門的輸出將如下圖所示(X、Y為輸入,Z為輸出):

觀察上述時鐘信號,可以發現,當兩個輸入都為高電平時,或非門的輸出為低電平,并且每個輸入邏輯低電平都保持低電平輸出狀態。在時鐘脈沖結束時,輸出變為高電平,因為或非門的兩個輸入端都為低電平。

通用或非門

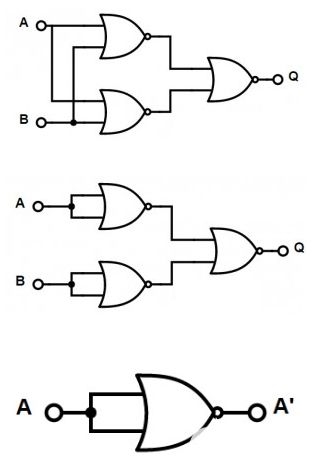

或非邏輯門被稱為“通用邏輯門”,只需在其輸入端進行一些更改,該門就可以用作任何基本邏輯門。但大多數情況下,我們更喜歡NAND門而不是NOR門來設計其它基本邏輯門。接下來看看如何使用或非門設計其他門。

1、僅使用或非門的基本邏輯門

其實或非門可以設計基本的邏輯門,例如AND、OR、NOT門。或非門執行所有3種類型的基本邏輯門如下圖所示:

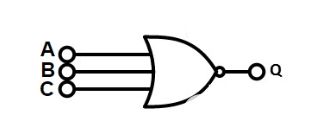

2、3-輸入或非門

多輸入或非門可以通過在其輸入側連接其他邏輯門來設計。下面來看看3輸入或非門的邏輯符號和真值表,其中布爾表達式沒有隨著輸入數量的變化而變化,或非門的輸出是或非門輸入加法的倒數。

3-輸入或非門符號:

3-輸入或非門的布爾表達式為Q = (A+B+C) ?。

3-輸入或非門的真值表如下:

當所有3個輸入為高電平時,3個輸入或非門的輸出為低電平,而對于所有其他輸入組合,它將為高電平。

3、4-輸入或非門

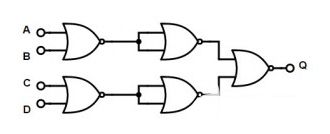

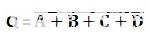

與3輸入或非門類似,也可以設計4輸入或非門,其符號如下圖所示:

4輸入或非門的布爾表達式是:

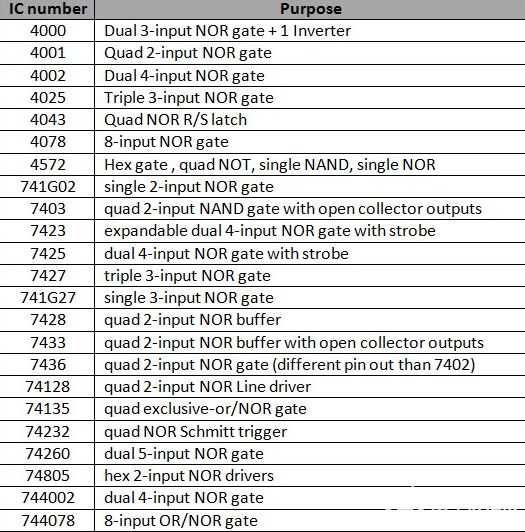

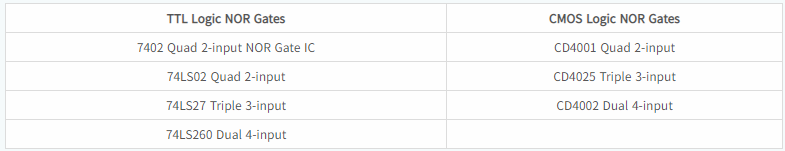

常用的TTL和CMOS邏輯或非門IC

下面給出了所有TTL和CMOS邏輯NOR門的IC列表:

一些最常用的或非門IC是:

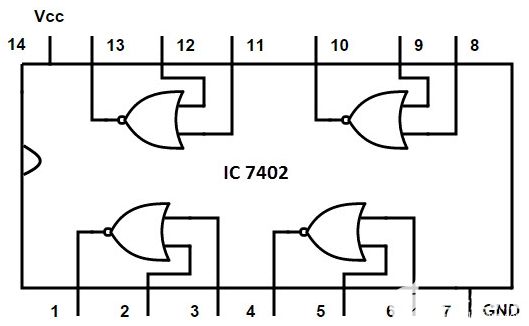

Pin引腳配置圖如下所示:

引腳說明如下圖所示:

主要應用

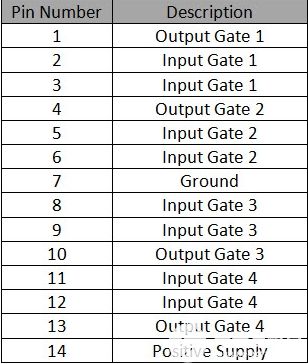

邏輯或非門可用于構建異或門和其他一些實時應用,它的實時應用之一是“混合攪拌罐(Mixer tank)”,下面簡單介紹下。

觀察下圖,可以使用3輸入NOR門來控制攪拌罐的成分流動。不同種類的成分儲存在單獨的圓柱形桶中,電容式接近開關布置在每個圓柱體的底部,位于其底部,這是為了檢測成分的數量或水平。

當配料下降到傳感器水平時,氣缸產生高電平邏輯輸出。高于傳感器的成分電平將被視為低邏輯電平(0)。當所有成分下降到傳感器電平時,或非門的所有輸入都將變為高電平。

當所有成分下降到傳感器電平時,或非門的輸出將變為高電平。其中輸出連接到電源轉換器,電源轉換器連接到Motot(混合成分)。NOR邏輯門的高輸出激活電源轉換器并激活電機,使電機運轉并混合所有成分。

總結

不看看出,或非門是數字邏輯電路中的基本元件,實現邏輯或非功能。有多個輸入端,1個輸出端,多輸入或非門可由2輸入或非門和反相器構成。只有當兩個輸入A和B為低電平(邏輯0)時輸出為高電平(邏輯1)。

需要注意的是,在實際使用過程中,由于或非門作為開關的打開速度相對較慢,所以人們更愿意用與非門(AND Gate)。

-

邏輯門

+關注

關注

1文章

142瀏覽量

24127 -

晶體管

+關注

關注

77文章

9745瀏覽量

138896 -

或非門

+關注

關注

0文章

21瀏覽量

15398

發布評論請先 登錄

相關推薦

使用輸入晶體管設計的或非門

使用輸入晶體管設計的或非門

評論