2020 年7 月14 日,半導體標準化組織JEDEC(JointElectron Device Engineering Council)發布了JESD79-5 DDR5 SDRAM 標準,帶來許多關鍵性性能強化。隨英特爾近期正式發布第12 代Core 處理器(代號Alder Lake),意味2021 年是DDR5 存儲器啟航元年。下載鏈接:《內存技術:內存測試和測量挑戰》

此文盡量設法排除高深莫測的DRAM相關技術名詞,讓各位迅速了解DDR5相對DDR4的優勢與可能的影響,最后再同場加映英特爾Atom x6000系列引進的「In-Band ECC」技術,讓大家瞧瞧英特爾如何在沒有ECC模組下提供類似糾錯功能。

「理所當然」的提升數據傳輸率

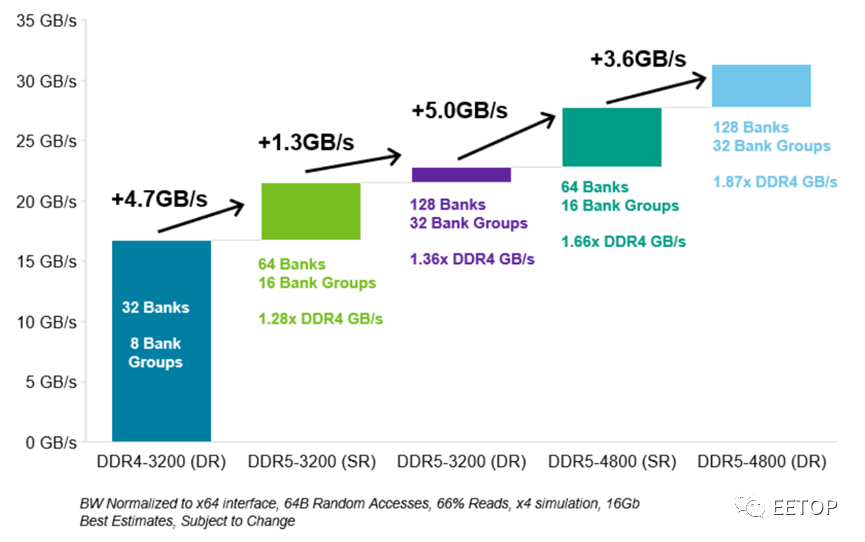

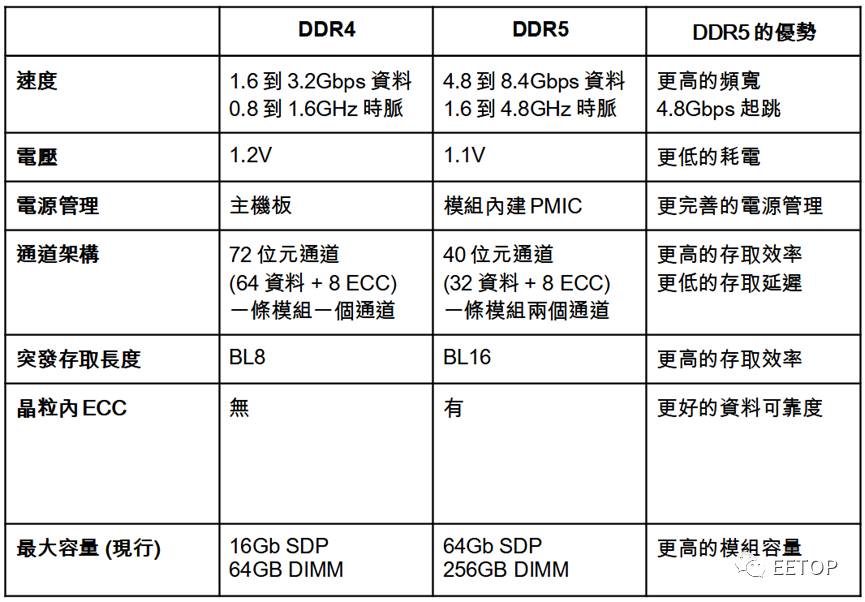

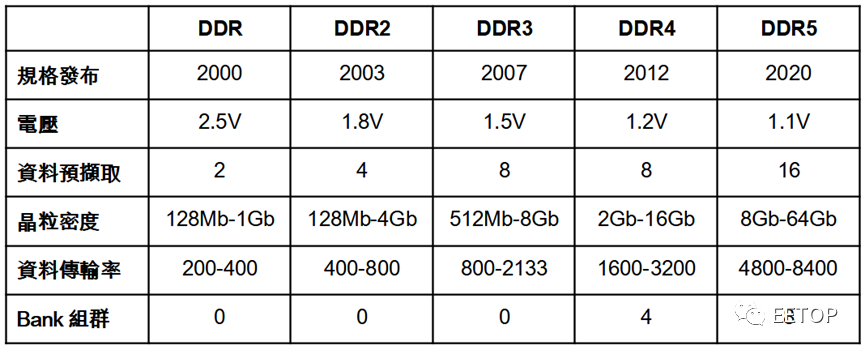

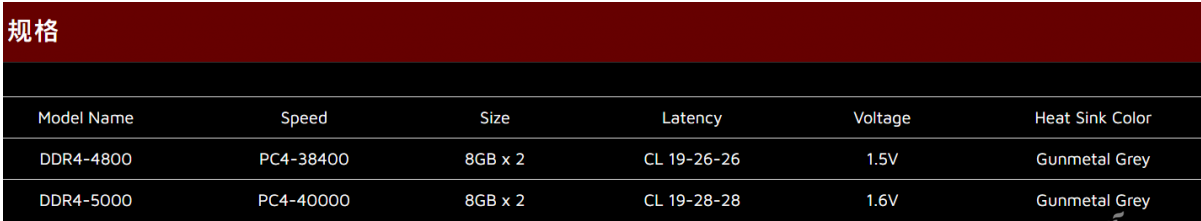

初期DDR5可提供超過DDR4 50%數據傳輸率,最終預期可達2.6倍8.4Gbps。回顧JEDEC SDRAM歷代演進,提升幅度還算驚人,但到頭來也只是充分反應相隔八年累積的制程技術成長。

至于「一定會膨脹」的容量看似沒什么好提,但后面會提到DDR5強化數據可靠性的手段。

更低電壓與嶄新電源架構

持續降低工作電壓也是歷代JEDEC SDRAM的傳統,從20年前DDR2.5V一路調降到DDR5 1.1V,讓存儲器運作「理論上」更節能省電。

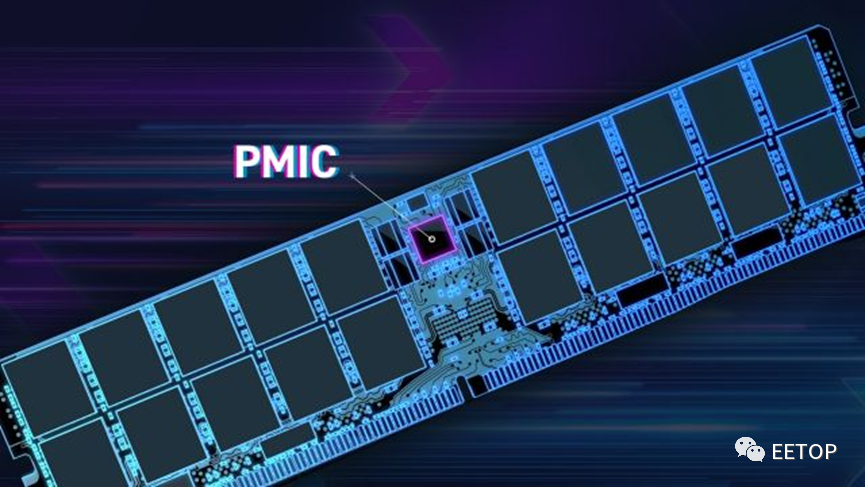

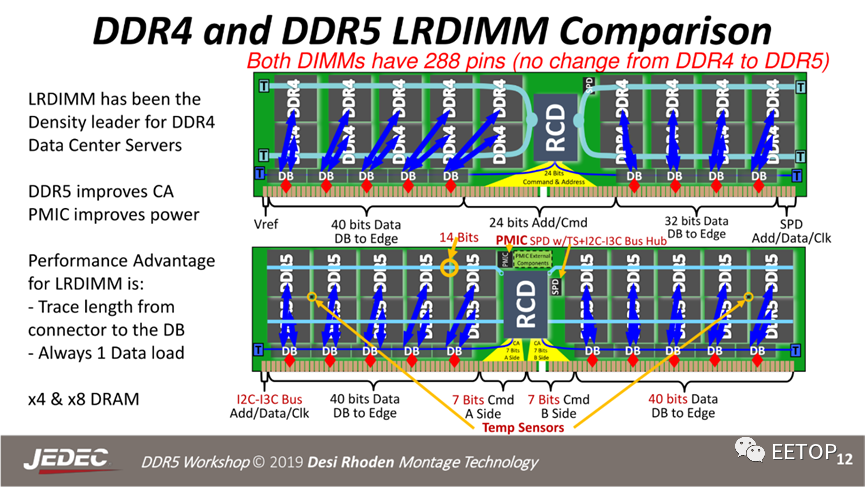

但當DDR5基礎工作電壓降到1.1V時,意味更小信號容限,所以過去由主機板負責的電源管理功能,就轉移到存儲器模組本身,因此DDR5會多一顆PMIC,直接控制存儲器電源,提供更佳信號辨識能力。

不過多了這顆PMIC也就抬高了成本,都將轉嫁給制造商成本和消費者帳單,以及更高的缺料風險。

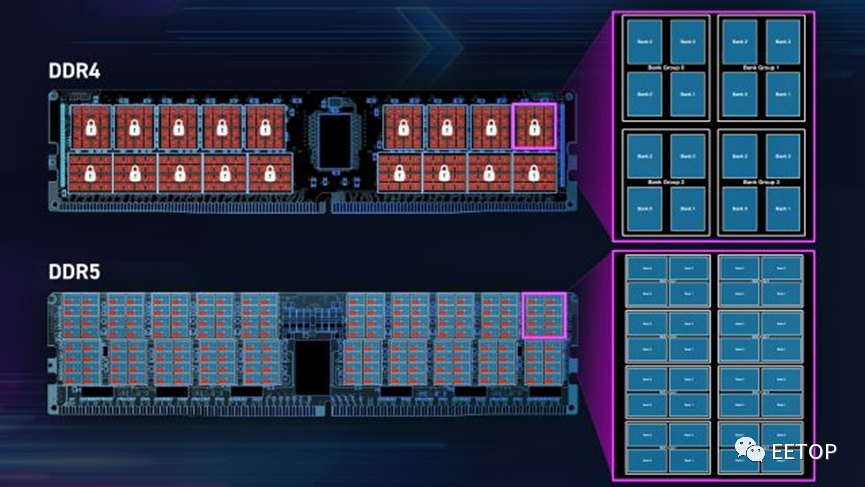

兩倍的Bank群組、通道架構與突發存取長度

Bank意指DRAM顆粒可單獨運作的儲存單元。DDR5采用八個Bank群組而成的32Bank,是DDR4兩倍。DRAM因儲存原理是需定時刷新(Refresh)數據的電容,DDR4與前代刷新時無法執行其他操作,但DDR5可透過Same Bank Refresh (REFsb)命令,允許系統刷新某些Bank時,可存取其他Bank的數據。

換言之,DDR5存取可用性起碼是DDR4兩倍。

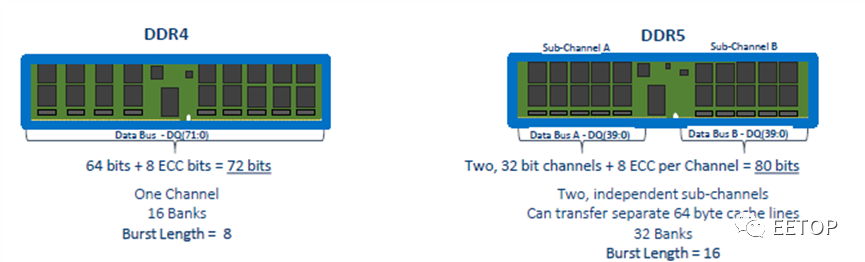

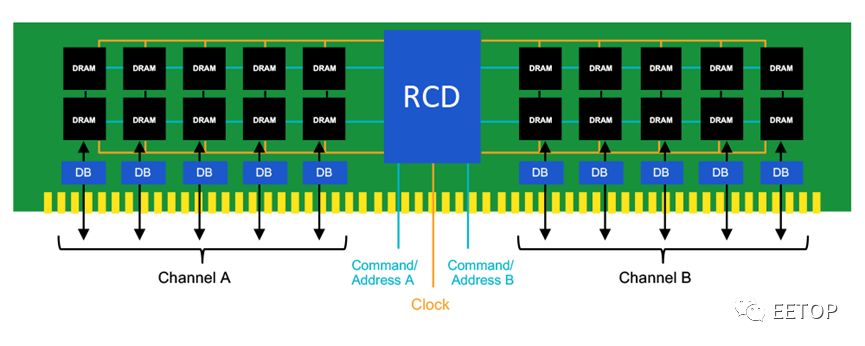

DDR5另一個規格面重大變化(也許是最重要者),在于將雙通道實作于單模組。過去DDR都是72位元(64位元數據+8位元ECC),但DDR5變成兩組40位元(32位元數據+8位元ECC)。兩個較小獨立通道可提高存儲器存取效率,特別是縮短存取延遲。分而治之的結構,也可便于提高信號完整性。

看起來似乎好棒?但對服務器會用到的ECC模組就不是這樣了,因拆成兩邊都需要完整ECC,會增加額外顆粒數量,例如原本18個顆粒的ECC模組就可能變成20顆,意味更高成本。

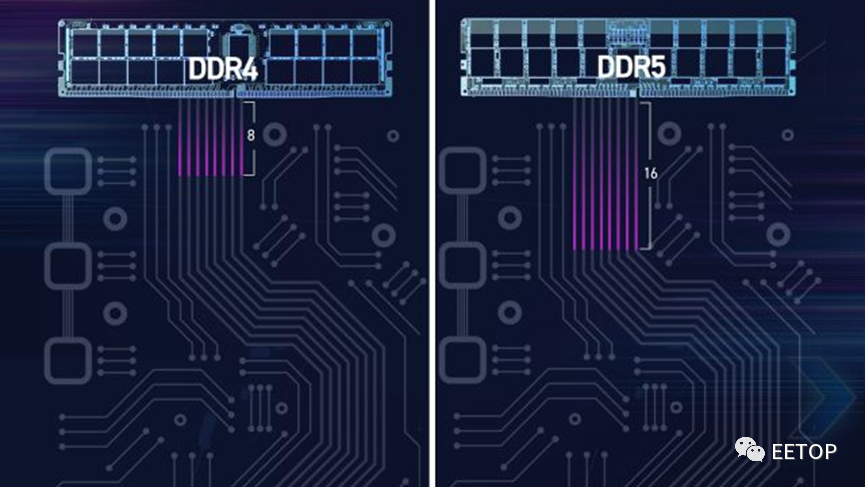

再來就是跟以上雙通道結構息息相關的突發存取長度(Burst Length)了,這數字決定單一讀寫指令可存取的數據量。DDR5的BL從DDR4八倍增到16,這對時下的主流處理器是個「魔術數字」。為何?DDR5的雙通道結構讓單次數據存取寬度變成32位元(4 Byte),BL16就代表「可一次填充處理器的64 Byte快取存儲器區塊」。

換句話說,一條DDR5模組可同時滿足兩個64 Byte快取區塊的需求,是DDR4兩倍。

更高的存儲器有效帶寬比例

一般來說,JEDECSDRAM的存儲器有效帶寬比例,多半是約定俗成的80%(理論和實際畢竟有差距),但DDR5結合這么多架構改進,按某些存儲器模組廠商估算,這次有機會達85%~90%,很接近Rambus水準(號稱90%以上)。搞了這么多年,JEDEC SDRAM「總算」看到Rambus的車尾燈,值得大書特書一下。

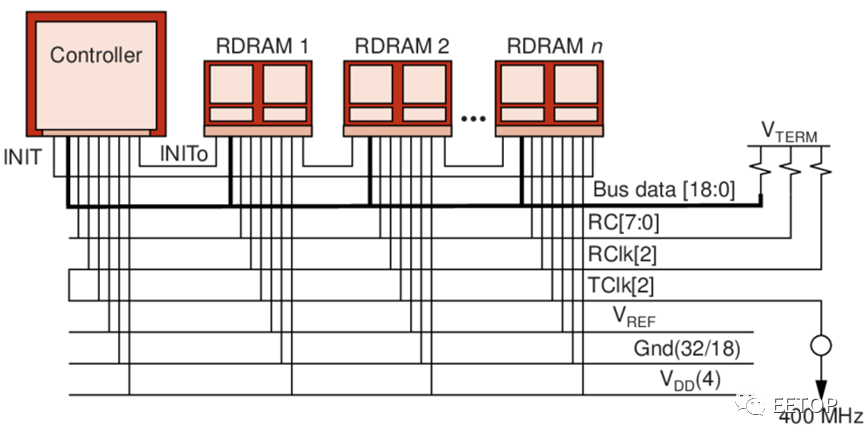

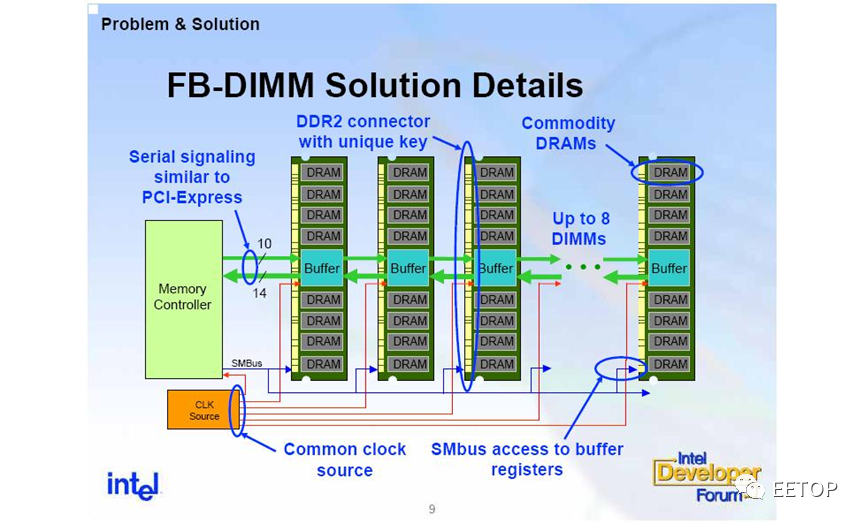

筆者不得不先談談Rambus這個英特爾芯片組發展史的黑歷史了。Rambus發展出一系列所謂「Protocol-Based DRAM」將傳統總線的定址、控制與數據,都包在類似網絡封包的Packet內,然后DRAM內部整合大多數控制單元功能,每顆DRAM如同一個網絡裝置,連接一條超高速序列(Serial)總線。也因此,Rambus DRAM不能有空存儲器模組,未使用存儲器模組須安裝「假的」CRIMM(Continuity RIMM)當終端。

Protocol-Based DRAM可用更少數據線就達成更高存儲器頻寬,也會有更高存儲器有效帶寬。Rambus的缺點也很明顯,更長存取延遲、高昂制造成本、更高發熱量,以及Rambus惡名昭彰的授權費。與PC133 SDRAM相比,同容量Rambus價格多達2~3倍。日后FB-DIMM(Fully-Buffered DIMM)也繼承類似Rambus的精神,終究難逃相同的命運。

更高的數據可靠度

以電容為儲存原理的DRAM,顆粒容量及儲存密度成長,背后藏著諸多潛在風險,如像構成地球低強度背景輻射的帶電粒子,引起位元翻轉的存儲器軟錯誤(Soft Error),這也成為潛在安全攻擊目標。這也是為何高效能非揮發性存儲器一直視為遲早取代DRAM的主因之一(雖然遲遲沒有發生)。

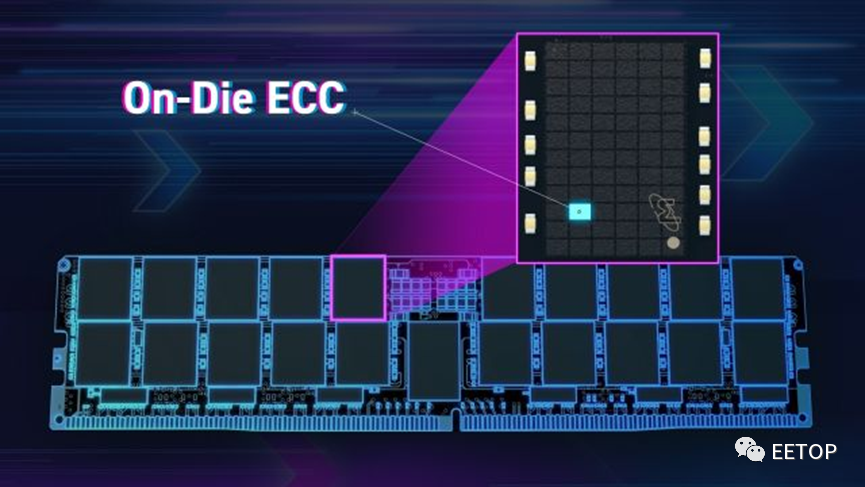

為了強化穩定性,DDR5支持晶粒內建糾錯(On-DieECC)機制,每128位元數據就附帶8位元糾錯碼。不過筆者并不認為這能取代標準ECC模組,只能說確保容量更大的DDR5顆粒可維持和過去同等級的數據可靠度。

這會增加多少潛在顆粒成本,只有原廠自己心知肚明。總之談錢傷感情,就干脆不談了。

同場加映:英特爾Atom x6000系列的In-Band ECC

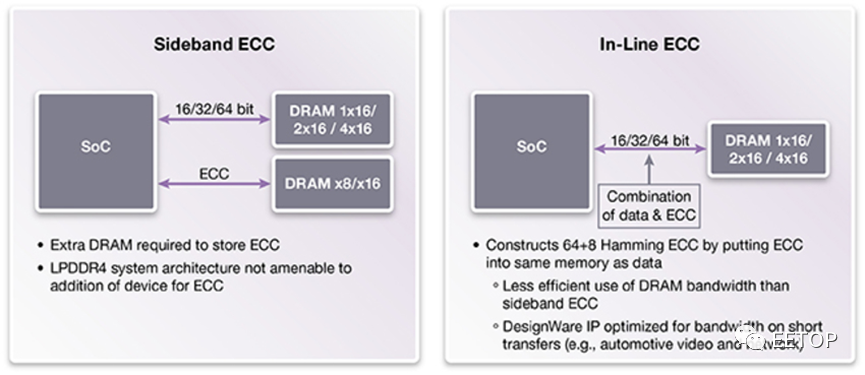

既然全文提到這么多次ECC,筆者就同場加映談談英特爾新一代Atom x6000處理器(代號Elkhart Lake)導入的In-Band ECC(或稱In-Line ECC)技術,不需要ECC存儲器模組也能達到相似數據可靠度。

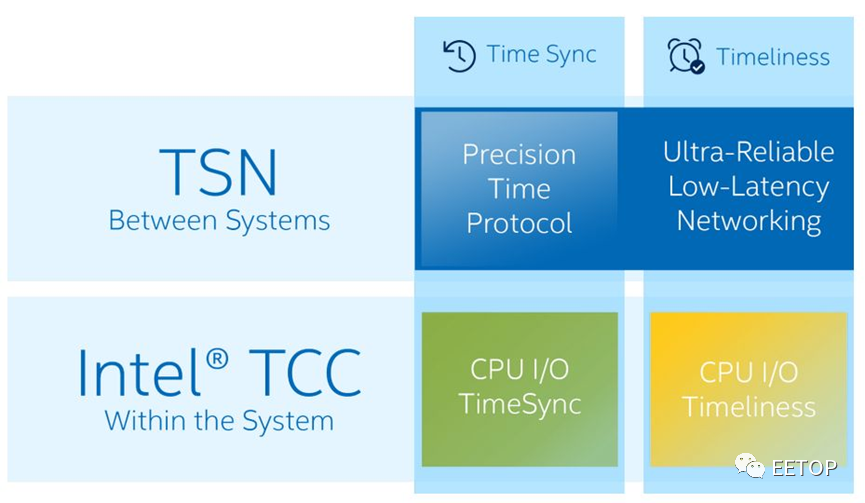

針對工業自動化的相關應用,英特爾Atom x6000系列補強不少新功能,如工業級時間敏感網絡(TimeSensitive Networking,TSN)和時間協調運算(Time Coordinated Computing,TCC),安全性和管理性也絲毫不含糊。基本上,論針對特定生態系統的解決方案完整度,也是現階段AMD依舊不及英特爾的先天弱點。

說穿了,In-BandECC藉由DRAM內分割一塊特定區域,存放存儲器數據的ECC碼。以Atom x6000為例,每64 Byte數據分配到2 Byte ECC,存儲器容量預留1/32放置后者。處理器存儲器控制也勢必多出相關后繼處理步驟。

但天底下沒有免費的午餐,In-Band ECC固然達成「低成本的高可靠度」,但前提是犧牲存儲器的讀寫性能。照英特爾官方說法,啟動In-Band ECC后,存儲器讀取效能劇降至原本一半,存儲器寫入更下探到三分之一。話說回來,這對工業物聯網應用,或許的確是值得的代價。

最后,終于是升級存儲器的好時機了嗎?

秉持勤儉持家的原則,筆者死守DDR3多年,連現在用的主機板都刻意選支持DDR3的華碩Z170M-3 D3,死撐活撐,直到最近微軟Windows 11判了確定無法升級的死刑。看在遲早得面對現實升級整臺桌機的份上,看到DDR5明顯演化,說不想直奔DDR5絕對是騙人的。

但時下世界正處于史上前所未見的「萬物缺料」,什么都漲,DDR5價格何時才能降到可負擔的水準,筆者實在毫無樂觀的理由,只能繼續看硬件測試網站的效能測試數據過過干癮了。

審核編輯 :李倩

-

半導體

+關注

關注

334文章

27714瀏覽量

222662 -

DRAM

+關注

關注

40文章

2326瀏覽量

183868 -

DDR

+關注

關注

11文章

715瀏覽量

65531 -

DDR5

+關注

關注

1文章

430瀏覽量

24209

原文標題:談談關于DDR5技術規格的那些事

文章出處:【微信號:AI_Architect,微信公眾號:智能計算芯世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DDR3/4都還沒玩夠,DDR5已經來啦

DDR4已經OUT Cadence宣布DDR5全新進展

5G時代你是等DDR5上市 還是升級DDR4內存

[譯] 盡管DDR5快來了,DDR4還是取得新進展

DDR5內存和DDR4有啥不同

專門為內存顆粒測試設計的DDR4/DDR5 Interposr測試板

DDR4和DDR5規格之間的差異

ddr5的主板可以用ddr4內存嗎 幾代CPU才能上DDR5

0706線下活動 I DDR4/DDR5內存技術高速信號專題設計技術交流活動

了解DDR5相對DDR4的優勢與可能的影響

了解DDR5相對DDR4的優勢與可能的影響

評論