PCIe的全名為PCI-Express,為一種高速串行計(jì)算機(jī)擴(kuò)充接口標(biāo)準(zhǔn),其優(yōu)勢(shì)為高速串行雙通道傳輸,且擁有高帶寬的特點(diǎn),隨著時(shí)代演進(jìn)成為最主流的接口傳輸標(biāo)準(zhǔn)之一。而在系統(tǒng)設(shè)計(jì)上,除了用于擴(kuò)充網(wǎng)卡或是顯示適配器的傳統(tǒng)PCIe插槽外,在SSD技術(shù)的蓬勃發(fā)展下,也發(fā)展出M.2以及NVMe connector作為外接SSD的媒介。為了讓顯卡和SSD能夠不受到CPU頻帶的限制無法充分發(fā)揮性能,PCIe 4.0的技術(shù)就在此背景下應(yīng)運(yùn)而生。

AMAZINGIC晶焱科技PCIe 4.0的 ESD 最佳解決方案

PCIe 3.0數(shù)據(jù)傳輸率為8Gb/s,而PCIe 4.0 數(shù)據(jù)傳輸率為16Gb/s,是PCIe 3.0的兩倍,且依舊維持PCIe可以向上和向下兼容的便利性,也就是PCIe 3.0的裝置可以與PCIe 4.0的slot連接,也可以將PCIe 4.0的裝置與PCIe 3.0的slot相連接。而傳輸速率提升兩倍(如圖一)也可以使原本需要連接的通道數(shù)減半,進(jìn)而產(chǎn)生更高的系統(tǒng)設(shè)計(jì)彈性,CPU可以空出更多的通道余裕連接至更多的裝置,例如:GPU以及NVMe SSD,消除系統(tǒng)設(shè)計(jì)的瓶頸限制,GPU或SSD直接對(duì)CPU作連接也消除了大部分延遲的影響。

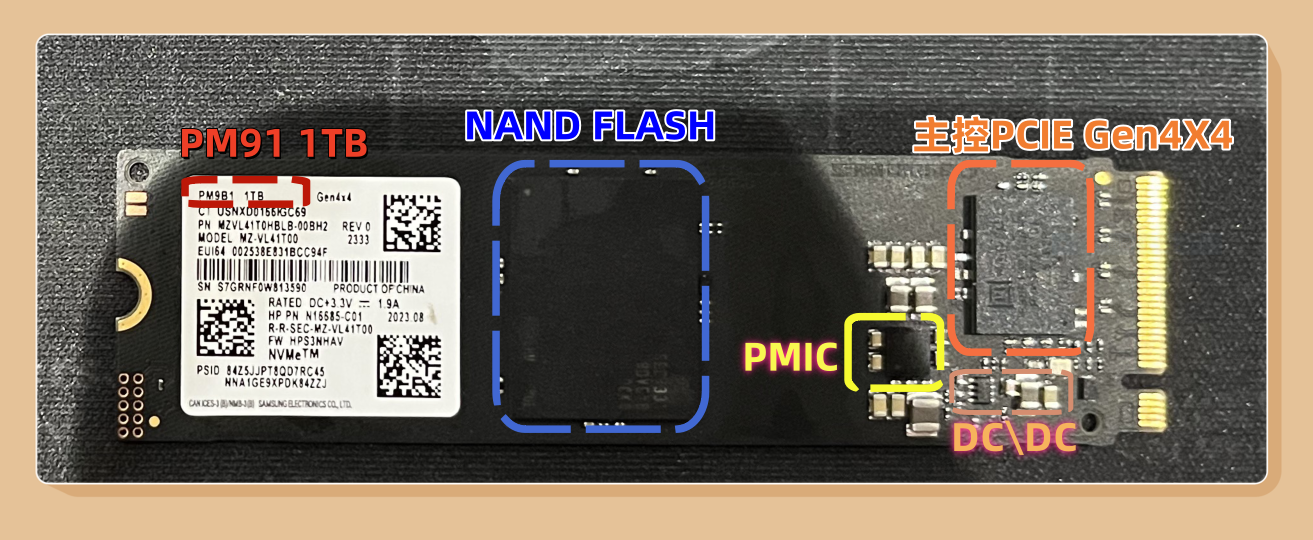

本文主要針對(duì)PCIe4.0的解決方案,而展望未來,Intel已宣布將在Alder Lake-S平臺(tái)上將PCIe接口從Rocket Lake的PCIe 4.0升級(jí)為PCIe 5.0,雖目前市場上顯示適配器尚以PCIe 4.0為對(duì)CPU的主要連接port,但Alder Lake-S已預(yù)計(jì)可對(duì)外支持x16的PCIe5.0提供給未來新版的顯示適配器使用。另一方面,也提供x4的PCIe 4.0可予NVMe SSD使用,來提高對(duì)桌上型玩家的吸引力以及更好的開機(jī)速度。而在AMD平臺(tái)方面,也將在Zen 4架構(gòu)上加入PCIe 5.0的支持。

CPU大廠競相在PCIe的接口上作升級(jí),大幅提升了對(duì)裝置連接的性能,以及滿足了現(xiàn)在消費(fèi)者對(duì)于數(shù)據(jù)串流的需求。除了消費(fèi)性市場之外,數(shù)據(jù)中心和超級(jí)計(jì)算機(jī)的數(shù)據(jù)傳輸量非常高,目前在邊緣計(jì)算、AI和5G network需求方興未艾,需要非常多的服務(wù)器作為儲(chǔ)存數(shù)據(jù)之用,其中會(huì)用到非常多的NVMe SSD,NVMe目前可以支持熱插入的使用,以方便數(shù)據(jù)中心的人員作硬盤故障的排除。然而此熱插入的使用場景會(huì)帶來對(duì)系統(tǒng)的極大的ESD突波威脅,由于SSD多藉由PICe 4.0在NVMe connector對(duì)主芯片直接作數(shù)據(jù)傳輸,而目前主芯片制程多已發(fā)展至10 nm以下的先進(jìn)制程,故此ESD突波造成系統(tǒng)內(nèi)部芯片毀損的案例已相當(dāng)困擾系統(tǒng)廠商。而在傳統(tǒng)的主板和桌面計(jì)算機(jī)市場,玩家常會(huì)自行更換顯示適配器或是擴(kuò)充網(wǎng)絡(luò)卡等等透過PCIe接口傳輸?shù)难b置,ESD突波也會(huì)透過PCIe slot的路徑造成內(nèi)部芯片發(fā)生不可回復(fù)的損傷。

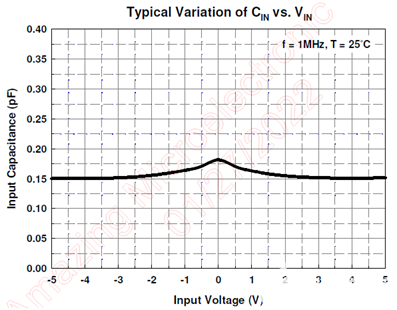

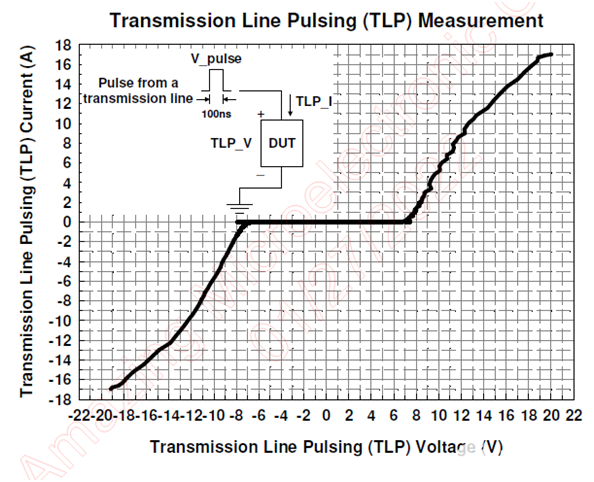

晶焱科技針對(duì)此應(yīng)用推薦使用5V 0201方案AZ5B75-01B于PCIe4.0 Tx.Rx訊號(hào)線,其極低的寄生電容值確保了PCIe 4.0的傳輸質(zhì)量(如圖二)。另市場也反應(yīng)近期在PRSNT pin以及PCIe_CLK pin有接獲返修的案例,而AZ5B75-01B亦可以用于上述兩種訊號(hào),優(yōu)異的箝位電壓(如圖三)可有效全面防護(hù)PCIe接口免于靜電的威脅,提供高速傳輸應(yīng)用更穩(wěn)定的可靠度。

| PCIe 3.0 | PCIe 4.0 | |

| Data Rate | 8 Gbit/s | 16 Gbit/s |

|

Band Width Needing Channels (Ex: 1.97 GB/s) |

x2 | x1 |

圖一、PCIe傳輸速度及電氣特性table

圖二、AZ5B75-01B 電容-電壓量測結(jié)果

圖三、AZ5B75-01B TLP量測結(jié)果

Reference: PCI-SIG

審核編輯:湯梓紅

-

ESD

+關(guān)注

關(guān)注

49文章

2065瀏覽量

173382 -

接口

+關(guān)注

關(guān)注

33文章

8694瀏覽量

151929 -

PCI

+關(guān)注

關(guān)注

4文章

671瀏覽量

130477 -

PCIe

+關(guān)注

關(guān)注

15文章

1262瀏覽量

83200

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

SCS 靜電管理計(jì)劃:用工業(yè) 4.0 解決方案克服電子行業(yè)的關(guān)鍵挑戰(zhàn)

Microchip發(fā)布全新Switchtec? PCIe 4.0交換機(jī)系列

兆芯最佳實(shí)踐應(yīng)用場景解決方案發(fā)布

“2025 IC風(fēng)云榜”揭曉,思爾芯獲“年度最佳解決方案獎(jiǎng)”

PCIe信號(hào)完整性問題解決方案

PCIe 4.0與3.0的區(qū)別 PCIe設(shè)備的故障排除方法

pcie 4.0與pcie 5.0的區(qū)別

PCIe 4.0與PCIe 3.0的性能對(duì)比

Cadence展示完整的PCIe 7.0 IP解決方案

pcie4.0插在3.0的主板上會(huì)怎么樣

pcie4.0和pcie3.0接口兼容嗎

晶振如何選型?確定這6大特性,以保證最佳解決方案

千視榮獲2023年度DAV數(shù)字音視工程網(wǎng)年度最佳解決方案獎(jiǎng)!

PCIe 4.0的ESD最佳解決方案

PCIe 4.0的ESD最佳解決方案

評(píng)論