異步計數(shù)器是那些輸出不受時鐘信號影響的計數(shù)器。由于異步計數(shù)器中的觸發(fā)器提供有不同的時鐘信號,因此在產(chǎn)生輸出時可能會有延遲。設計異步計數(shù)器所需的邏輯門數(shù)量非常少,所以它們的設計很簡單。異步計數(shù)器的另一個名稱是“波紋計數(shù)器”。

異步計數(shù)器中使用的觸發(fā)器數(shù)量取決于計數(shù)器的狀態(tài)數(shù)量(例如Mod 4、Mod 2等)。計數(shù)器的輸出狀態(tài)數(shù)稱為計數(shù)器的“模數(shù)”或“MOD”。計數(shù)器可以擁有的最大狀態(tài)數(shù)為2n,其中n表示計數(shù)器中使用的觸發(fā)器數(shù)量。例如,如果有2個觸發(fā)器,則計數(shù)器的最大輸出數(shù)為4,即 2*2。因此,它被稱為“MOD-4計數(shù)器”或“模數(shù)4計數(shù)器”。

主要類型

數(shù)字電子產(chǎn)品中有多種類型的異步計數(shù)器可用,常見的例如:

4 位異步UP計數(shù)器

4位異步DOWN計數(shù)器

4位異步UP/DOWN計數(shù)器

1、異步4位UP計數(shù)器

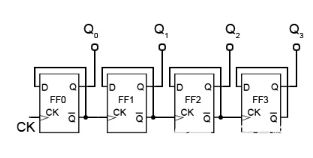

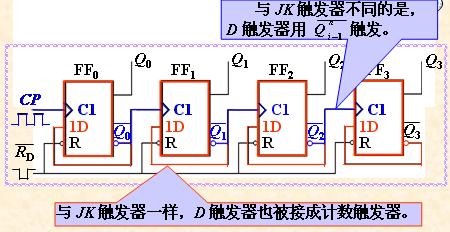

帶D觸發(fā)器的4位異步UP計數(shù)器如下圖所示,它能夠計數(shù)從0到15的數(shù)字。所有觸發(fā)器的時鐘輸入級聯(lián),每個觸發(fā)器的D輸入(DATA輸入)連接到觸發(fā)器的狀態(tài)輸出。

這意味著觸發(fā)器將在時鐘信號的每個有效邊沿或上升沿觸發(fā)。時鐘輸入連接到第一個觸發(fā)器,而計數(shù)器中的其他觸發(fā)器接收從前一個觸發(fā)器的 Q' 輸出輸入的時鐘信號。當時鐘信號出現(xiàn)上升沿時,第一個觸發(fā)器的輸出將發(fā)生變化。

在異步4位UP計數(shù)器中,觸發(fā)器以切換模式連接,因此當時鐘輸入連接到第一個觸發(fā)器FF0時,其在一個時鐘脈沖后的輸出將變?yōu)?0。

每個觸發(fā)器的Q輸出的上升沿觸發(fā)其下一個觸發(fā)器的時鐘輸入,它將下一個時鐘頻率觸發(fā)到其應用輸入的一半,每個觸發(fā)器(Q0、Q1、Q2、Q3)的Q輸出表示 4 位UP計數(shù)器的計數(shù),例如20 (1) 到23 (8)。

工作原理如下:

現(xiàn)在假設觸發(fā)器的4個Q輸出最初為0000。當時鐘脈沖的上升沿施加到FF0時,輸出Q0將變?yōu)檫壿?,下一個時鐘脈沖將Q0輸出變?yōu)檫壿?。這意味著時鐘脈沖的輸出狀態(tài)在一個周期內(nèi)切換(從0變?yōu)?)。

由于FF0的Q'連接到FF1的時鐘輸入,那么第二個觸發(fā)器的時鐘輸入將變?yōu)?。這使得FF1的輸出為高電平(即Q1=1),表示值為20。這樣下一個時鐘脈沖將使Q0再次變高。

所以現(xiàn)在Q0和Q1都為高,這導致4位輸出11002。現(xiàn)在如果應用第四個時鐘脈沖,它將使Q0和Q1變?yōu)榈蜖顟B(tài)并切換FF2。因此輸出Q2將變?yōu)?0102。由于該電路是4位向上計數(shù)器,因此輸出是從0、1、2、3….15即00002到11112(0到1510)的二進制值序列。

例如,如果當前計數(shù)=3,則遞增計數(shù)器將計算下一次計數(shù)為4。

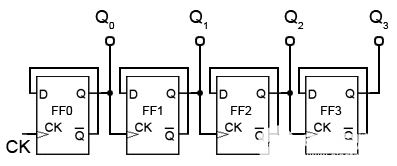

2、異步4位DOWN計數(shù)器

下圖顯示了一個4位異步DOWN計數(shù)器。這是對UP計數(shù)器的簡單修改。4位向下計數(shù)器將從15到0向下計數(shù)。所有觸發(fā)器的時鐘輸入級聯(lián),每個觸發(fā)器的D輸入(DATA輸入)連接到邏輯1。

這意味著觸發(fā)器將在時鐘信號的每個有效邊沿(正邊沿)處切換。時鐘輸入連接到第一個觸發(fā)器。計數(shù)器中的其他觸發(fā)器接收來自前一個觸發(fā)器的Q輸出而不是Q' 輸出的時鐘信號。

這里Q0、Q1、Q2、Q3代表4位遞減計數(shù)器的計數(shù)。當時鐘信號的上升沿出現(xiàn)時,第一個觸發(fā)器的輸出將發(fā)生變化。例如,如果當前計數(shù)=3,則向上計數(shù)器將計算下一個計數(shù)為2。輸入時鐘將導致下一個觸發(fā)器的輸出(計數(shù))發(fā)生變化。

異步遞減計數(shù)器的操作與異步遞加計數(shù)器的操作完全相反。在這里,輸入端的每個時鐘脈沖都會減少單個觸發(fā)器的計數(shù)。因此,遞減計數(shù)器從15、14、13…0計數(shù),即(0到1510)或11112到00002。

另外,UP/DOWN計數(shù)器都是使用異步設計的,基于時鐘信號,目前還沒有廣泛的使用,因為它們在高時鐘速度下并不可靠。

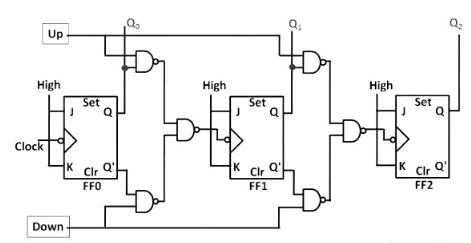

異步3位UP/DOWN計數(shù)器

通過將UP計數(shù)器和DOWN計數(shù)器的概念相加,便可以設計出異步3位UP/DOWN計數(shù)器。3位異步加/減計數(shù)器如下所示。

它可以根據(jù)時鐘信號輸入以任何一種方式計數(shù),從上到下或從下到上。

向上計數(shù);如果UP輸入和DOWN輸入分別為1和0,則第一個觸發(fā)器到第三個觸發(fā)器之間的NAND門會將FF0的非反相輸出傳遞到FF1的時鐘輸入。類似地,F(xiàn)F1的Q輸出將傳遞到FF2的時鐘輸入。因此向上 / 向下計數(shù)器執(zhí)行向上計數(shù)。

向下計數(shù);如果DOWN輸入和UP輸入分別為1和0,則第一個觸發(fā)器到第三個觸發(fā)器之間的NAND門會將FF0的反相輸出傳遞到FF1的時鐘輸入。同樣,F(xiàn)F1的Q輸出將通過FF2的時鐘輸入。因此UP/DOWN計數(shù)器執(zhí)行向下計數(shù)。

UP/DOWN計數(shù)器比UP計數(shù)器或DOWN計數(shù)器慢,因為加法傳播延遲將添加到NAND門網(wǎng)絡。

關于時鐘紋波

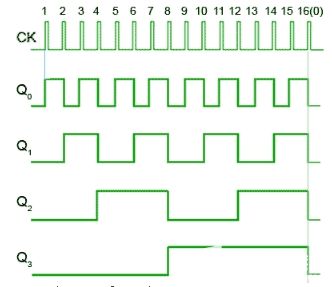

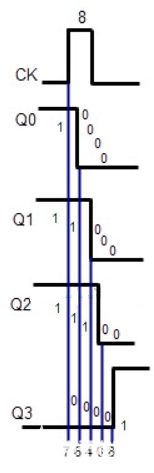

驅(qū)動電路的各個時鐘脈沖的時間延遲之和稱為“時鐘紋波”,下圖可以清楚的解釋邏輯門如何在每個觸發(fā)器中產(chǎn)生傳播延遲。

邏輯門的傳播延遲用藍線表示,它們中的每一個都會增加下一個觸發(fā)器的延遲,所有這些單獨的觸發(fā)器的總和稱為電路的傳播延遲。

由于所有觸發(fā)器的輸出以不同的時間間隔變化,并且對于時鐘信號的每個不同輸入,每次輸出都會出現(xiàn)一個新值。例如,在時鐘脈沖8處,輸出應從11102 (710) 變?yōu)?0012 (810),時間延遲為400到700ns(納秒)。

對于8個以外的時鐘脈沖,序列將發(fā)生變化。雖然該瓶頸問題阻礙了該電路用作可靠的計數(shù)器,但它作為簡單有效的分頻器仍然很有價值,其中高頻振蕩器提供輸入,鏈中的每個觸發(fā)器將頻率除以2。

主要優(yōu)點

異步計數(shù)器可以很容易地用T觸發(fā)器或D觸發(fā)器設計。

異步計數(shù)器也稱為紋波計數(shù)器,用于低速電路。

它們用作除以N計數(shù)器,將輸入除以N,其中N是整數(shù)。

異步計數(shù)器也用作截斷計數(shù)器。這些可用于設計任何Mod編號計數(shù)器,即偶數(shù)Mod(例如:Mod4)或奇數(shù)Mod(例如:Mod3)。

主要缺點

有時“重新同步”可能需要額外的觸發(fā)器。

要計算截斷計數(shù)器的序列(Mod不等于2n),可能需要額外的反饋邏輯。

在計數(shù)大量位時,異步計數(shù)器的傳播延遲非常大。

對于高時鐘頻率,由于傳播延遲,可能會出現(xiàn)計數(shù)錯誤。

主要應用

異步計數(shù)器用作分頻器,用作除以N的計數(shù)器。

用于低功率應用和低噪聲發(fā)射。

用于設計異步十進制計數(shù)器。

用于環(huán)形計數(shù)器和約翰遜計數(shù)器。

異步計數(shù)器用于Mod N紋波計數(shù)器。例如Mod 3、Mod 4、Mod 8、Mod 14、Mod 10等。

總結(jié)

簡單來說,異步計數(shù)器可以說成是異步時序電路,其主要特點是每個觸發(fā)器的時鐘脈沖端CP不全都連接在一起,所以觸發(fā)器的翻轉(zhuǎn)時刻有先有后,其輸出可能會產(chǎn)生干擾延遲現(xiàn)象,但其電路結(jié)構(gòu)設計相對簡單。

-

觸發(fā)器

+關注

關注

14文章

2003瀏覽量

61347 -

異步計數(shù)器

+關注

關注

0文章

10瀏覽量

8074

發(fā)布評論請先 登錄

相關推薦

100進制計數(shù)器

基于Multisim的計數(shù)器設計仿真

計數(shù)器同步清零和異步清零的區(qū)別

同步計數(shù)器和異步計數(shù)器是什么 同步計數(shù)器和異步計數(shù)器的主要區(qū)別?

時序邏輯電路設計之異步計數(shù)器

異步計數(shù)器的主要類型

異步計數(shù)器的主要類型

評論