年度ITC活動于9月的最后一周舉行,我們一直在關注來自EDA供應商的所有新聞亮點,因為花在測試器上的時間可能是一個主要成本,而在生產(chǎn)過程中發(fā)現(xiàn)缺陷芯片的價值是非常關鍵的。小芯片、2.5D和3D IC設計已經(jīng)引起了測試界的關注,我們了解到西門子EDA剛剛宣布用他們的DFT方法來解決新的測試需求。Vidya Neerkundar是DFT產(chǎn)品Tessent系列的產(chǎn)品經(jīng)理,她介紹了最新情況。

DFT的挑戰(zhàn)

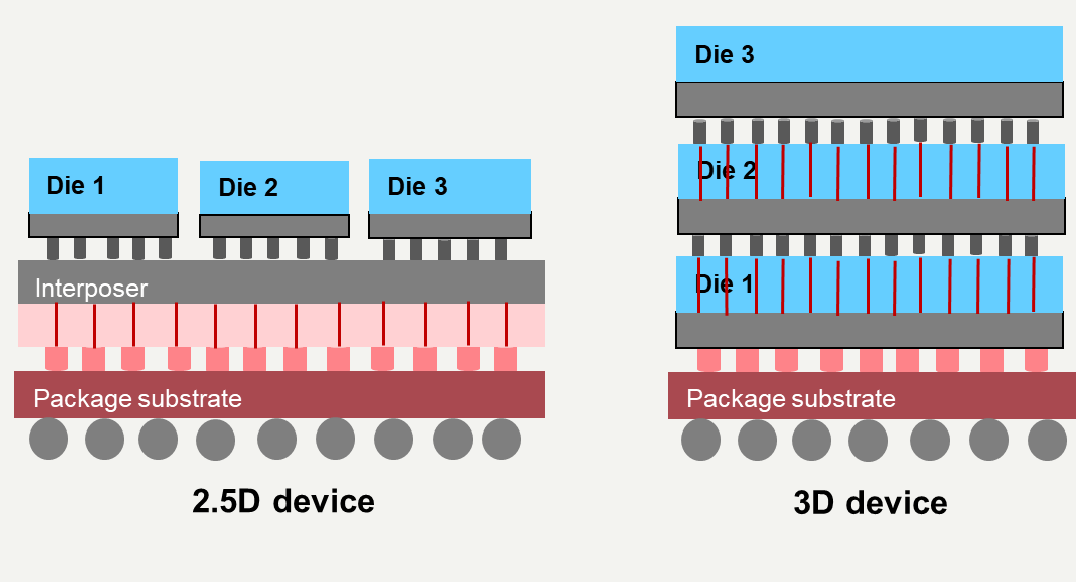

在IC設計的大部分歷史中,一個封裝中都只有一個Die,或者是多芯片模塊(MCM)。對于有多個Die的2.5D和3D IC,如何進行單獨的Die測試,然后使它們適用于最終的封裝?

如果其中每個Die的DFT架構彼此不同呢?

是否有一種最佳的方法來進行封裝內(nèi)的Die測試,以減少測試時間?

2.5D和3D小芯片

Tessent Multi-die

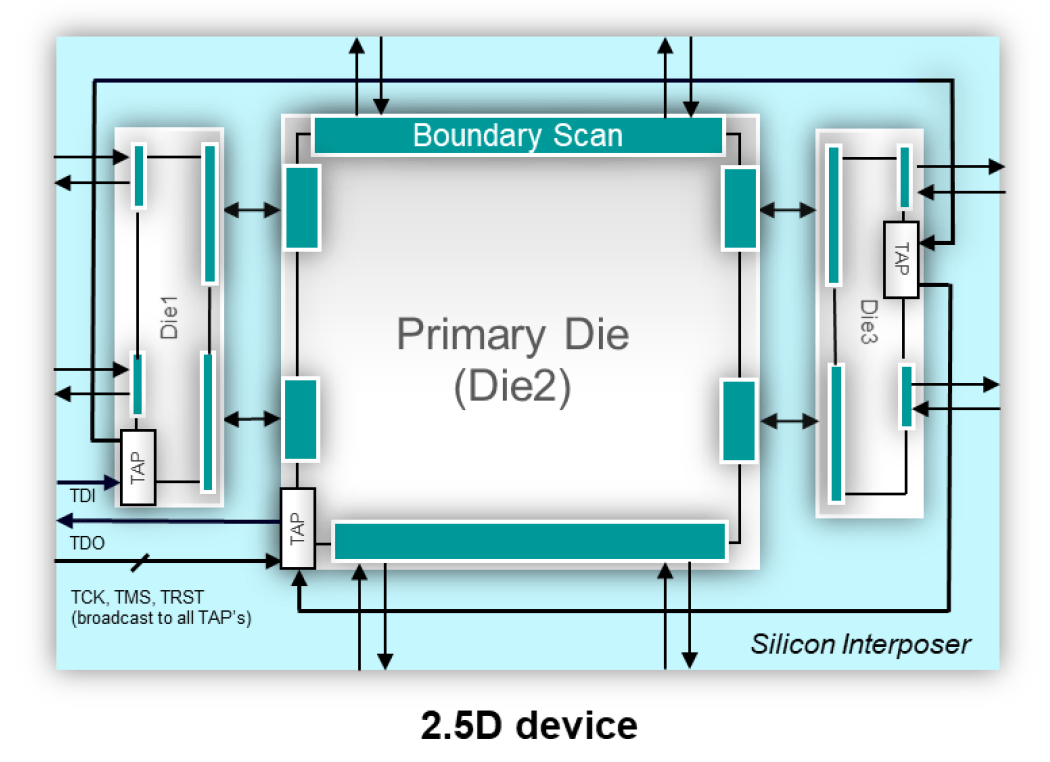

西門子的開發(fā)團隊擴展了他們的技術,支持使用Tessent Multi-die 的2.5D和3D IC封裝。Tessent流掃描網(wǎng)絡使用2D分層掃描測試。現(xiàn)在,這種方法將2D分層DFT擴展到2.5D和3D IC。以下是2.5D設備中三個小芯片的情況:

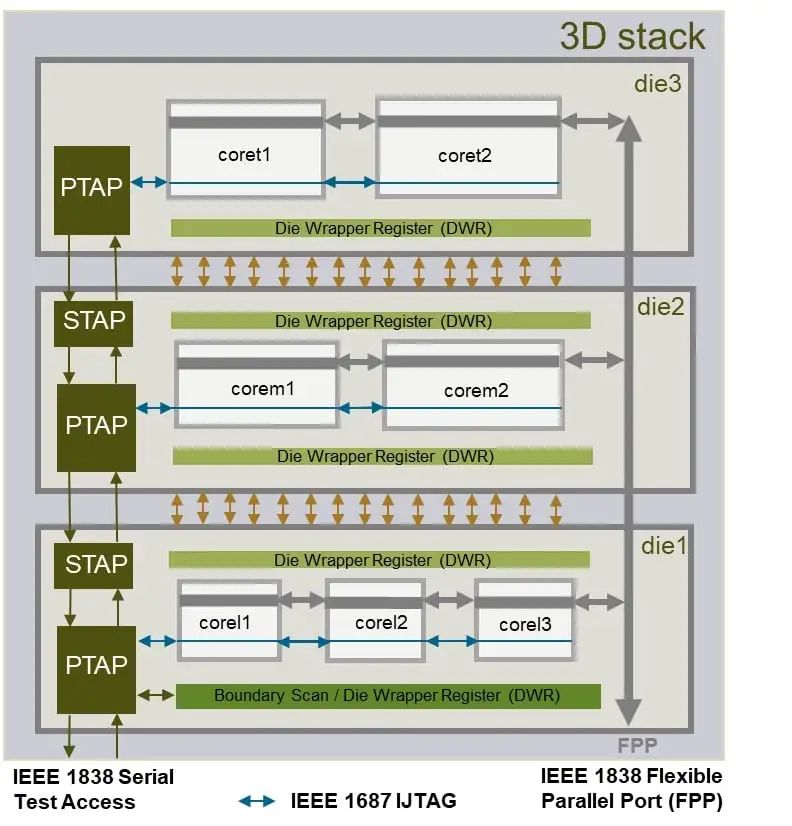

IEEE為3D堆疊集成電路的測試訪問架構創(chuàng)建了一個標準,稱為IEEE 1838-2019。IEEE 1687使用另一個標準IEEE 1149.1定義了集成電路內(nèi)嵌入儀器的訪問和控制,該標準帶有測試訪問端口。Tessent Multi-die支持所有這些標準。

芯片設計中的每個Die都有一個邊界掃描描述語言(BSDL)文件,然后Tessent Multi-die將創(chuàng)建包級BSDL。

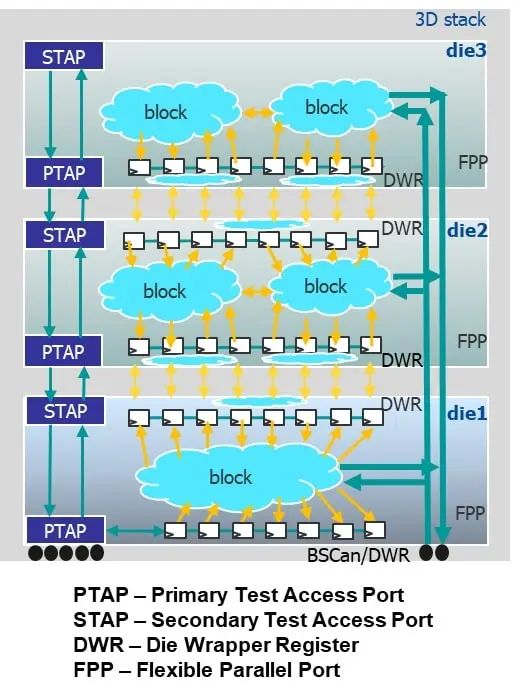

IEEE 1838標準

該以Die為中心的測試標準于2019年11月獲得委員會批準,并允許將一個Die作為多Die堆棧的一部分進行測試。為了測試目的,使用一個柔性并行端口(FPP)、Die包裝寄存器(DWR)和測試訪問端口(TAP)連接Die的3D堆棧:

用于測試的3D堆棧

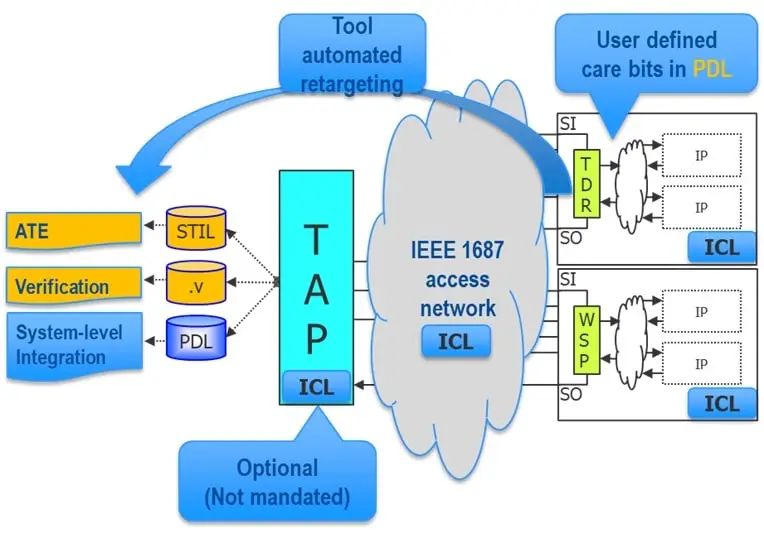

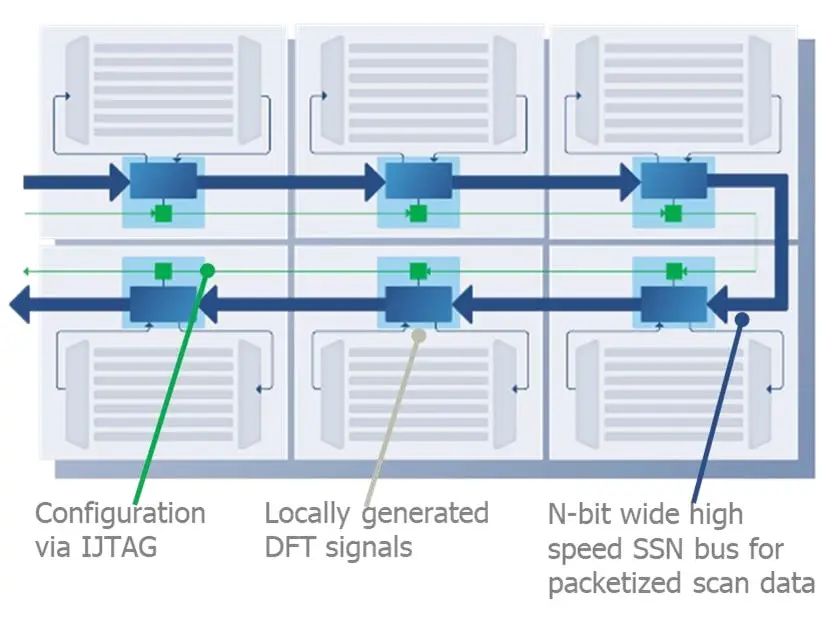

IEEE 1687 -內(nèi)部JTAG

這個2014年的標準有助于簡化嵌在每個Die內(nèi)的儀器的使用。有一種儀器連接語言(ICL)和過程描述語言(PDL)來定義儀器。ATE系統(tǒng)和內(nèi)部JTAG之間的流程如下所示:

IEEE 1687流

IEEE 1149.1 JTG

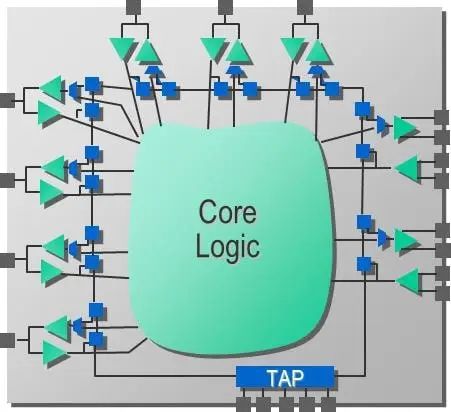

帶有測試訪問端口的邊界掃描標準可以追溯到1990年,邊界掃描描述語言(BSDL)出現(xiàn)于2001年。該標準定義了指令和測試數(shù)據(jù)如何在芯片內(nèi)部流動。

IEEE 1149.1 JTAG

將所有這些測試標準放在一起,我們可以看到Tessent Multi-die如何連接到3D堆棧中的每個芯片。每個Die內(nèi)核的測試模式和測試調(diào)度是通過Tessent流掃描網(wǎng)絡(SSN)完成的。

Tessent流掃描網(wǎng)絡

SSN基本上是將測試數(shù)據(jù)傳輸分組,從而將核心DFT和芯片DFT解耦,允許同時測試的核心獨立移動。實際的好處是為DFT規(guī)劃節(jié)省時間,更容易進行路由和定時關閉,并最多可以減少4倍的測試時間。

總結

代工廠、設計、測試和IEEE之間的密切合作創(chuàng)造了一個充滿活力的2.5D和3D生態(tài)系統(tǒng),所有的技術都已到位,以推進半導體創(chuàng)新。西門子EDA在使用IEEE標準的同時擴展了他們的Tessent軟件,以接受新的測試挑戰(zhàn)。Tessent Multi-die與所有其他的Tessent產(chǎn)品和平臺集成在一起,因此我們不必將工具和流程拼湊在一起。

審核編輯:劉清

-

IC設計

+關注

關注

38文章

1302瀏覽量

104286 -

MCM

+關注

關注

1文章

68瀏覽量

22375 -

tap

+關注

關注

0文章

8瀏覽量

2674

原文標題:DFT如何用于2.5D和3D IC?

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

什么是電纜測試以及如何完成電纜測試

什么是保護裝置測試以及如何完成

是否有一種方法來確定GPIF接口在等待GPIF主機的數(shù)據(jù)時干還是空

天線測試及評估有哪些方法?

天線測試有哪些方法?

如何使用Die-to-Die PHY IP 對系統(tǒng)級封裝 (SiP) 進行高效的量產(chǎn)測試?

軟件驅(qū)動程序是否有一種相當簡單的方法來檢測安裝了哪個rtc設備?

ESP32C3射頻測試,是否需要使用Wi-Fi Adaptivity方法來進行Wi-Fi范圍測試?

用自動測試方法來替代手工接線測試,對網(wǎng)分測試端口進行擴展

QT原生的QJson是否有更優(yōu)雅的方法來封裝一些Json對象

一種簡單的方法來將振蕩器相位噪聲轉(zhuǎn)換為時間抖動

是否有一種最佳的方法來進行封裝內(nèi)的Die測試以減少測試時間

是否有一種最佳的方法來進行封裝內(nèi)的Die測試以減少測試時間

評論