I2C和SPI不足之處

I2C不足之處

從設(shè)備無法主動向主設(shè)備發(fā)起通訊

SPI不足之處

需要四根通訊線路來進(jìn)行較大的數(shù)據(jù)通訊

沒有明確的定義標(biāo)準(zhǔn)

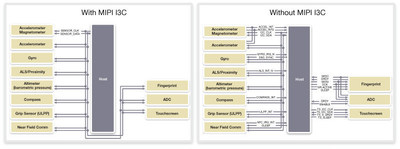

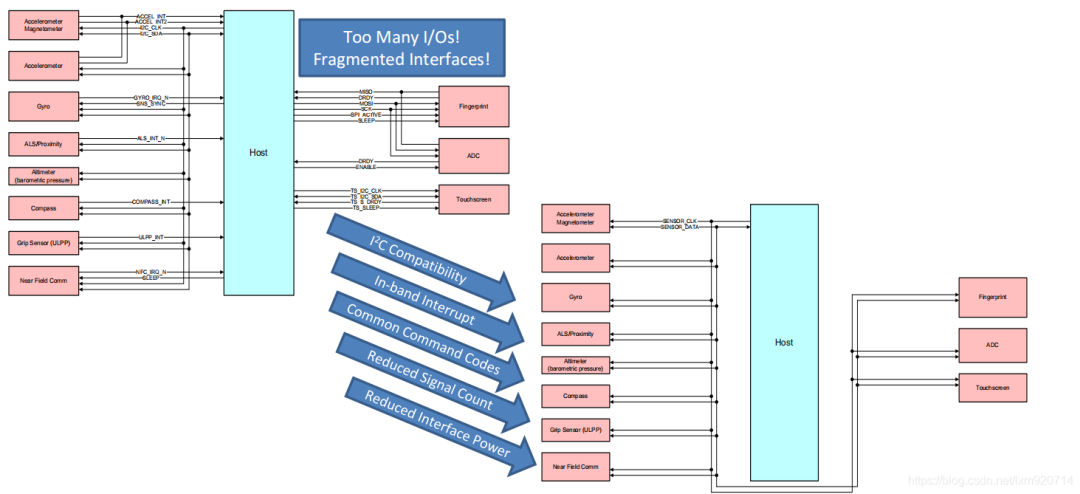

隨著移動設(shè)備對于傳感器數(shù)量的增加以及對性能的提高,I2C和SPI逐漸達(dá)到瓶頸,而I3C可以在同一根主線上支持更多的傳感器設(shè)備,而且不會因為要支持中斷或睡眠模式而增加額外的邏輯信號。

并且I3C可以在更低功耗的情況下提供更快的傳輸速率。

MIPI I3C概述

MIPI I3C (MIPI Alliance Improved Inter Integrated Circuit) 是一種可擴(kuò)展的中速串行控制總線接口,用于將外圍設(shè)備連接到應(yīng)用處理器,簡化集成并提高成本效率,適用于廣泛的設(shè)備互連應(yīng)用,包括傳感器和存儲器接口,為移動產(chǎn)品(從智能手機、可穿戴設(shè)備到汽車系統(tǒng))提供創(chuàng)新設(shè)計。

MIPI I3C 結(jié)合了傳統(tǒng)I2C和SPI接口的關(guān)鍵屬性,以提供統(tǒng)一的、高性能、極低功耗的解決方案。

I3C v1.0 提供了集成機械、運動、生物識別、環(huán)境和任何其他類型傳感器的新功能;

MIPI I3C v1.1(現(xiàn)為 v1.1.1)通過添加外圍命令、控制和通信的新功能來構(gòu)建該功能到短距離的主機處理器和系統(tǒng)可管理性。

MIPI I3C技術(shù)在標(biāo)準(zhǔn)CMOS I/O上實現(xiàn)。它使用兩線接口,與4線SPI相比,可減少引腳數(shù)和信號路徑,有助于在設(shè)備中集成更多傳感器,為設(shè)計人員提供更低的復(fù)雜性和更大的靈活性。它還可以用作邊帶接口,以進(jìn)一步減少引腳數(shù)。

MIPI I3C 支持 10Mbps的最低數(shù)據(jù)速率,并提供更高性能的高數(shù)據(jù)速率模式選項,與以前的選項相比,在性能和能效方面實現(xiàn)了大幅飛躍。

最新版本提供額外總線通道的可擴(kuò)展使用,以提高接口速度;

支持帶內(nèi)中斷(IBI),使存在于2線MIPI I3C總線上的設(shè)備能夠發(fā)出中斷,無需使用額外的I / O引腳信號。(I2C和SPI接口通常需要額外的邏輯信號來實現(xiàn)中斷功能);

MIPI I3C基本原理

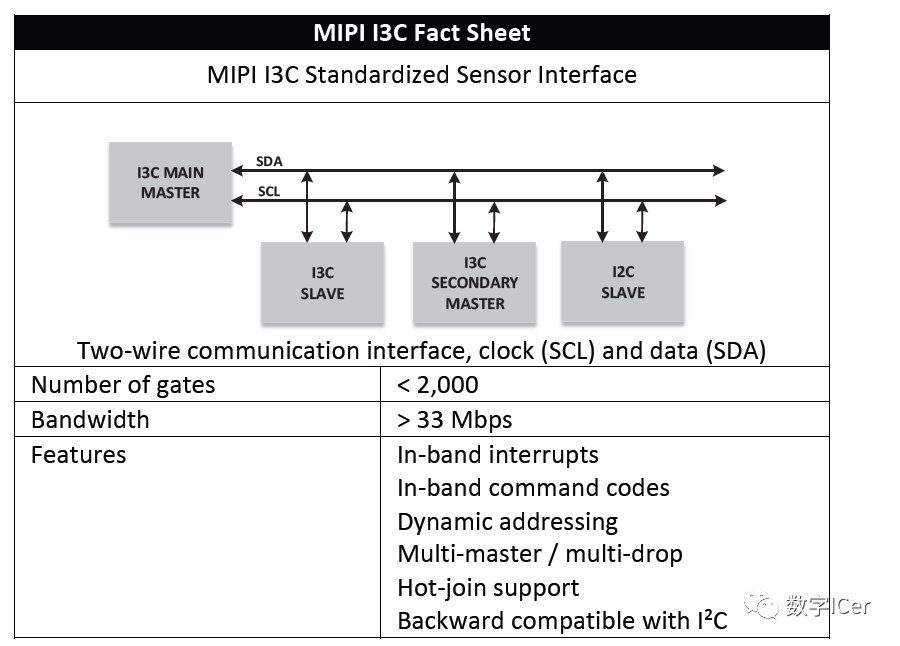

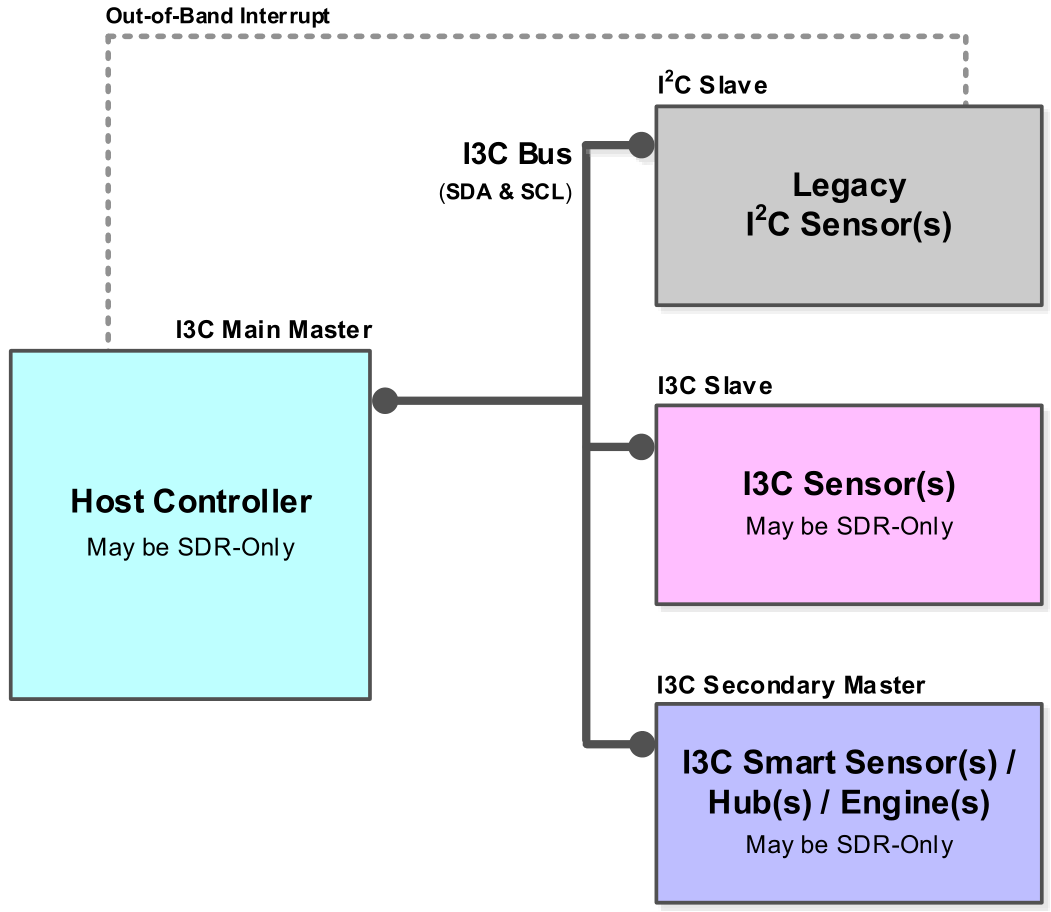

I3C接口使用的跟I2C類似,也是一根漏級數(shù)據(jù)線(SDA)和一根推挽式時鐘線(SCL),該SDA線上的從設(shè)備可以控制數(shù)據(jù)總線,并且可以啟動中斷。

主控通過該SCL線可以將總線的時鐘頻率調(diào)節(jié)到12.5MHZ。

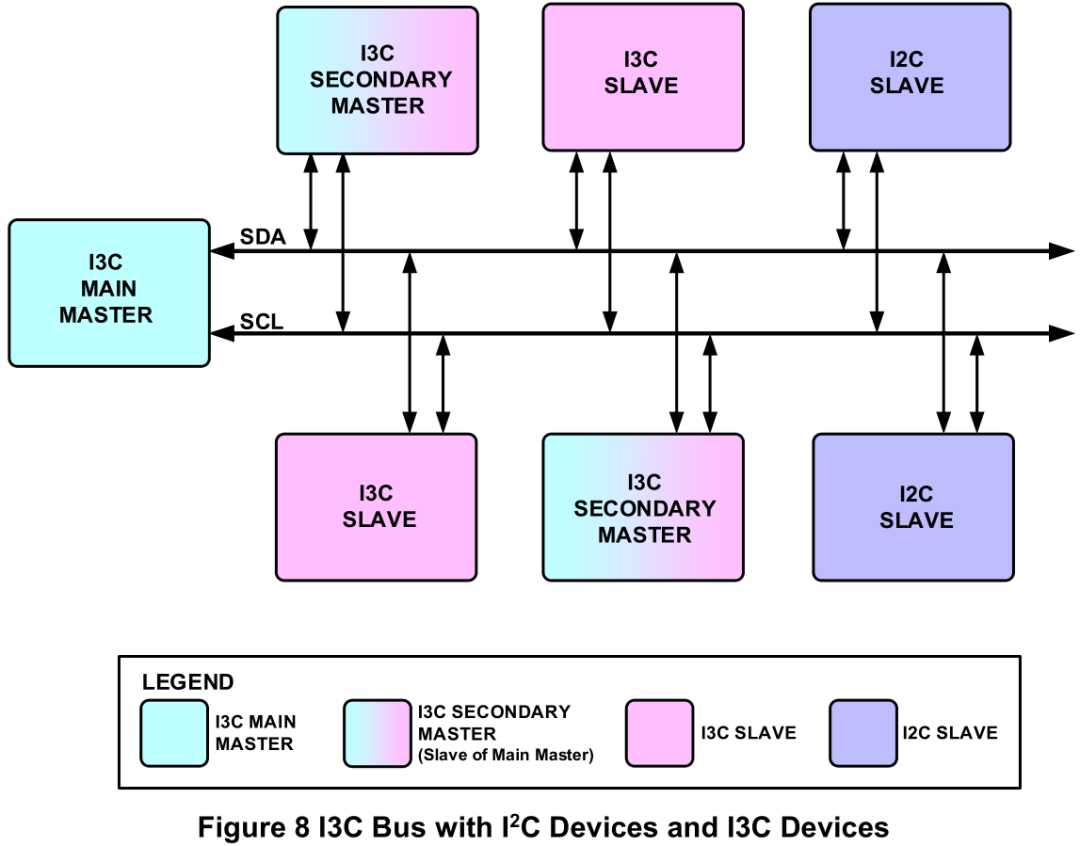

I3C支持多種類型設(shè)備,包括Main Master(當(dāng)前主設(shè)備),secondary master(輔助主設(shè)備)、I3C Slave、I2C Slave。

圖1

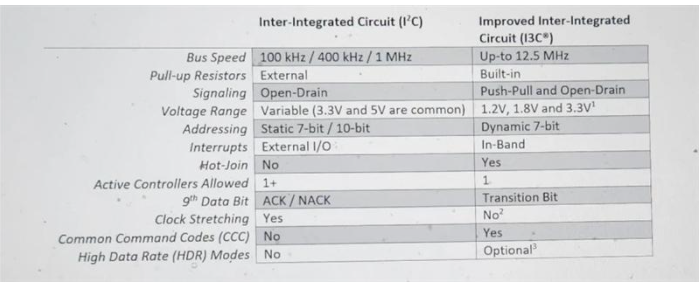

主設(shè)備可以動態(tài)為I3C分配7-bit地址,同時也支持為傳統(tǒng)I2C設(shè)備靜態(tài)的分配地址。這樣就使得I3C兼容I2C。而且相比I2C功耗降低了一個等級,但是傳輸速率提升了一個數(shù)量級。

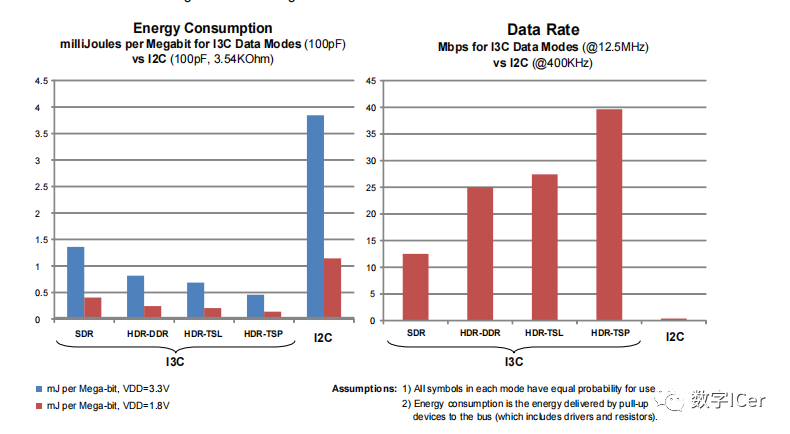

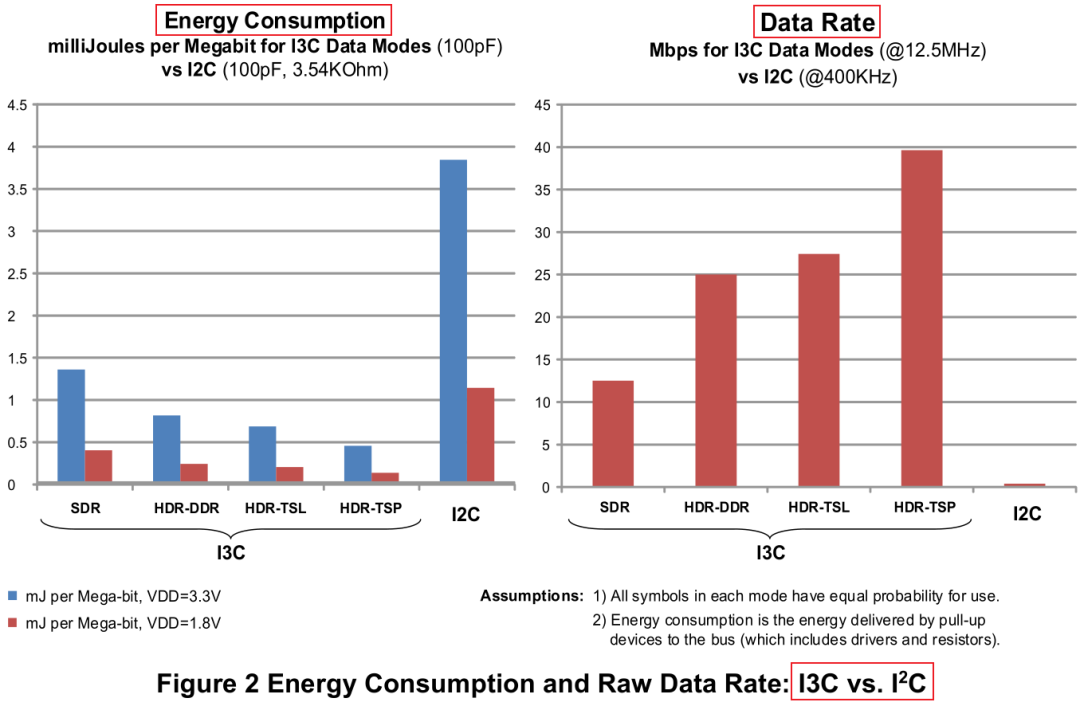

I3C提供了四種數(shù)據(jù)傳輸模式,在時鐘速率達(dá)到12.5MHz時,默認(rèn)的SDR模式下數(shù)據(jù)傳輸速率可以達(dá)到12.5Mbps,在HDR模式下可以達(dá)到25/27.5/39.5Mbps。除去控制字節(jié),可有效提供 11.1、20、23.5 和 33.3 Mbps 的數(shù)據(jù)比特率;

圖2 I3C 與 I2C能耗和數(shù)據(jù)速率對比

上圖左側(cè)顯示了不同 I3C 模式下給定數(shù)據(jù)量與 I2C 相比的能耗(單位為毫焦每兆比特),而右側(cè)是數(shù)據(jù)吞吐量。兩者都顯示出 I3C 的顯著優(yōu)勢。

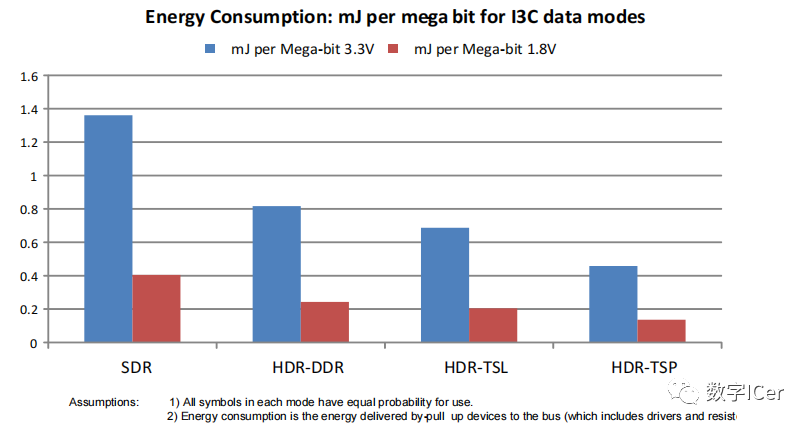

圖3 I3C在不同模式下消耗的能量對比

從上圖來看,I3C的HDR_TSP模式的功耗最低,從圖2右側(cè)可以看出HDR_TSP模式的數(shù)據(jù)速率最快,能夠支持超過33Mbps的有效數(shù)據(jù)比特率。

在數(shù)據(jù)傳輸?shù)倪^程中有I3C糾錯機制進(jìn)行保護(hù);

I3C允許從設(shè)備啟動帶內(nèi)中斷,這對于I2C和SPI設(shè)備來說都需要一根額外的信號線才能實現(xiàn)。當(dāng)總線處于空閑狀態(tài)時,從設(shè)備可以通過中斷機制發(fā)送一個"START"信號,然后主設(shè)備會為從設(shè)備提供一個時鐘信號,從設(shè)備可以通過主設(shè)備提供的分配地址將設(shè)備驅(qū)動到總線上來啟動中斷。

如果此時有多個從設(shè)備嘗試啟動中斷,則地址最小的從設(shè)備獲得此次仲裁。同時主設(shè)備發(fā)出ACK信號響應(yīng)此次中斷并重新啟動總線或者繼續(xù)從從設(shè)備接收數(shù)據(jù),也可以發(fā)出NACK信號來結(jié)束通信。

例如:I2C和SPI的缺陷是無法主動的與主設(shè)備進(jìn)行通訊,如果傳感器需要反饋數(shù)據(jù),需要額外添加一個中斷管腳,隨著移動設(shè)備上傳感器數(shù)量的增加,使得GPIO數(shù)增加。

而I3C可以通過帶內(nèi)中斷,使從設(shè)備可以主動發(fā)起中斷進(jìn)行通訊,大大減小了對GPIO中斷的依賴;

I3C允許從設(shè)備在總線配置完成之后再連接到總線上,即熱接入特性。連接在同一總線上的傳感器可以暫時關(guān)閉,直到需要喚醒的時候才激活喚醒。熱連接應(yīng)遵守特定的電氣限制,不得干擾MIPI I3C線路。

已為啟用和禁用事件、管理MIPI I3C特定功能(動態(tài)尋址、定時控制等)等標(biāo)準(zhǔn)操作定義了一組通用命令代碼(CCCs)。

該通用命令代碼可以發(fā)送廣播(發(fā)送給所有設(shè)備)或者可以指向總線上的特定設(shè)備。在使用傳感器時功耗和性能是必須考慮的,因為即使主程序處理器處于空閑狀態(tài)(低功耗模式或者深度睡眠),Always-on 傳感器 和 傳感器 hubs也會不斷的累積數(shù)據(jù),累積的傳感器數(shù)據(jù)通常是有規(guī)律的,需要在傳感器、傳感器 hub和應(yīng)用處理器之間定期快速傳輸,從而最大限度地降低功耗。

主要亮點

將 I2C 和 SPI 的關(guān)鍵功能整合到先進(jìn)的綜合規(guī)范中;

減少引腳數(shù)和信號路徑,兩條通訊線路(SCL和SDA);

高性能;

低功耗;

低電磁干擾 (EMI);

支持多主設(shè)備,同時向后兼容 I2C;

其他技術(shù)亮點包括多控制器支持、動態(tài)尋址、命令代碼兼容性以及用于高級電源管理功能(如睡眠模式)的統(tǒng)一方法。

用例

將外圍設(shè)備連接到任何移動設(shè)備中的應(yīng)用處理器

傳感器管理功能,簡化設(shè)備中多個傳感器的連接和管理

MIPI Touch over I3C 為已處理和原始觸摸數(shù)據(jù)提供融合接口選項

MIPI CCI over I3C 提供更快、更低延遲和更高效的相機控制

支持多種新應(yīng)用

內(nèi)存邊帶信道

“Always-on”imaging

服務(wù)器系統(tǒng)管理

調(diào)試應(yīng)用程序通信

觸摸屏命令和通信

傳感器設(shè)備命令、控制和數(shù)據(jù)傳輸

功耗管理

它提供同步和異步時間戳,可以有效的把握外設(shè)傳感器通訊的準(zhǔn)確性和先后時間,以提高使用來自各種傳感器的信號的應(yīng)用程序的準(zhǔn)確性。

它還可以快速批處理和傳輸數(shù)據(jù),以最大限度地減少主機處理器的能耗。

I3C應(yīng)用場景

適合低成本、現(xiàn)成標(biāo)準(zhǔn)化總線解決方案,該解決方案具有小型電路板 (PCB) 占位面積以及定義明確且易于使用的外圍設(shè)備、傳感器和應(yīng)用生態(tài)系統(tǒng)。

隨著時間的推移,I3C有可能在觸摸、低分辨率camera、音效、環(huán)境傳感器和變頻器等領(lǐng)域取代傳統(tǒng)的I2C,SPI,UART等接口。

審核編輯:劉清

-

CMOS

+關(guān)注

關(guān)注

58文章

5735瀏覽量

236095 -

SoC設(shè)計

+關(guān)注

關(guān)注

1文章

148瀏覽量

18817 -

I2C

+關(guān)注

關(guān)注

28文章

1495瀏覽量

124587 -

SDA

+關(guān)注

關(guān)注

0文章

124瀏覽量

28264

原文標(biāo)題:SOC設(shè)計之MIPI I3C

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

MIPI-I3C總線接口簡述

Gowin I3C SDR IP的參考設(shè)計

基于MIPI I3C規(guī)范從I2C無縫連接I3C的關(guān)鍵優(yōu)點

MIPI聯(lián)盟公開其傳感器接口規(guī)范MIPI I3C

關(guān)于MIPI I3C Sensor接口標(biāo)準(zhǔn)制定的介紹和應(yīng)用

符合最新MIPI I3C規(guī)范的DesignWare IP提供高帶寬和可擴(kuò)展性

Arasan宣布現(xiàn)貨供應(yīng)PHY I/O IP

MIPI I3C主機控制器接口加速傳感器集成

Gowin I3C SDR IP參考設(shè)計

I3C協(xié)議規(guī)范的詳細(xì)內(nèi)容

I3C Introduction是什么意思

I2C和I3C的區(qū)別有哪些

I2C和I3C關(guān)于功耗和傳輸速率的對比

什么是I3C接口 I3C和SPI接口有什么區(qū)別

I3C接口通信基礎(chǔ)

MIPI I3C的基本原理及其應(yīng)用概述

MIPI I3C的基本原理及其應(yīng)用概述

評論