大家在進行PCB設計時過孔肯定是要接觸的,那么大家知道過孔對于我們PCB的信號質量影響有多大嗎?在搞清楚上面這個這個問題之前我們先給大家介紹一下我們在PCB設計時過孔應該如何選取。

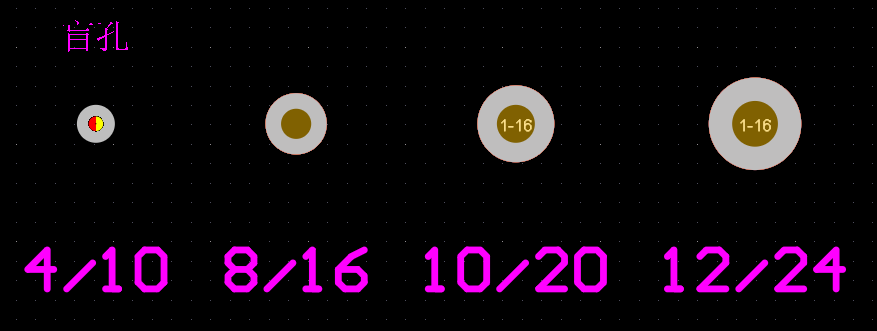

一般過孔種類有以下三種可以進行選擇:(單位是mil)

8/16±2mil 10/20±2mil 12/24±2mil

通常我們在板子比較密的情況下會用8/16±2mil(8/14, 8/16, 8/18都可以)大小的過孔,板子比較空曠的時候可以選取12/24±2mil(12/22, 12/24, 12/26都可以)大小的過孔,那板子器件密度在兩者之間則可以采用10/20±2mil(10/18, 10/20, 10/22都可以)大小的過孔。

站在經濟效益上來講我們過孔越大成本越低,所以我們要控制板子的成本的話,在滿足我們設計的同時盡量把過孔設置大一點。

當然在HDI板子當中我們通常是需要用到盲埋孔,通常我們的盲孔可以設置的大小范圍是4/10±2這樣子,通常打在焊盤上面就可以了,但是需要注意的是不要打在焊盤的正中心,通常打在焊盤的邊緣就可以了,這樣在工藝處理方面會好一點。

那么我們的過孔是不是越大越好或者說越小越好呢,很顯然并不是這樣子的。

在工藝的角度下我們的過孔內徑是不能小于板厚的1/7,為什么呢?

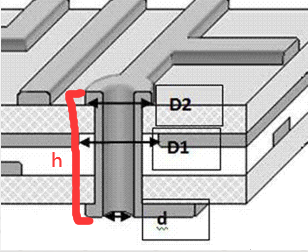

因為在我們的過孔小于1/7的情況下,受工藝技術的影響,無法做到過孔孔壁均勻鍍銅,在不能均勻鍍銅的情況下我們板子的電氣性能就會受到影響。所以在我們在板子厚度較大時也要加大我們的過孔,通常板厚和最小過孔的關系如下表所示:

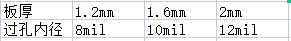

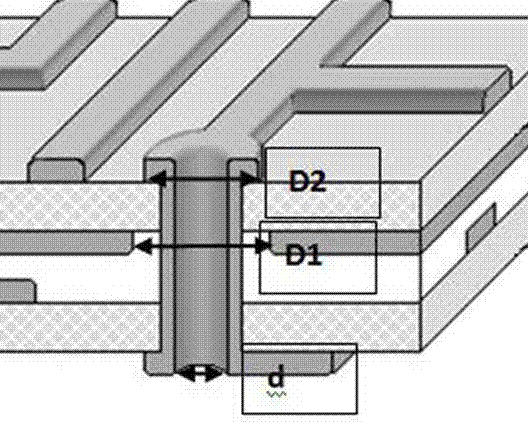

我們上面的出來的結論是通常過孔要大一點會更好,那么我們這個時候需要向大家介紹兩個公式,一個是過孔寄生電容的計算公式:C=1.41εTD2/(D1-D2)另一個是寄生電感的計算公式:L=5.08h[ln(4h/d)+1]。

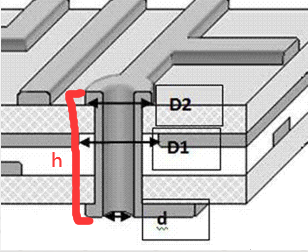

附圖1

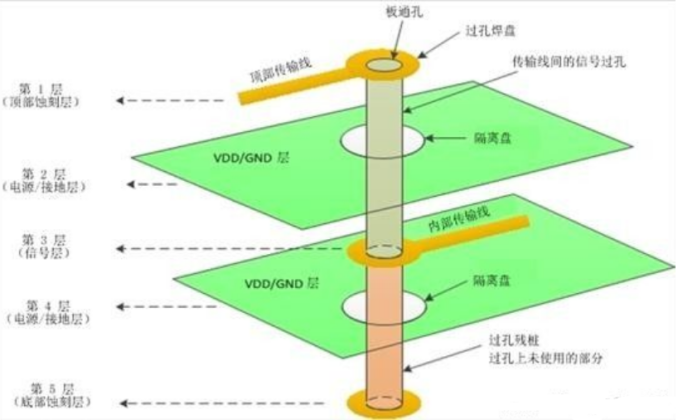

附圖2

我們首先看一下過孔寄生電容計算公式:

ε:板子的介電常數,通常不同的板材他們的介電常數也不一樣,T:指的是板子的厚度。

假設過孔是在GND層的情況下,D1值是過孔邊緣與銅皮的避讓距離(反焊盤),D2:指的是過孔的外徑。

由上面的公式我們可以得出一下結論:

1、在板材和板厚不變的情況下D1越大則寄生電容越小,C與D1成反比關系。

2、在板材和厚度不變的情況下D2越大則寄生電容越大,C與D2成正比關系。

3、在板厚和D2,D1不變的情況下,板材的介電常數越大則寄生電容越大,C與ε成正比關系。

4、在介電常數以及D2,D1不變的情況下,板厚T越大則寄生電容越大。

然后我們再分析一下寄生電感計算公式:

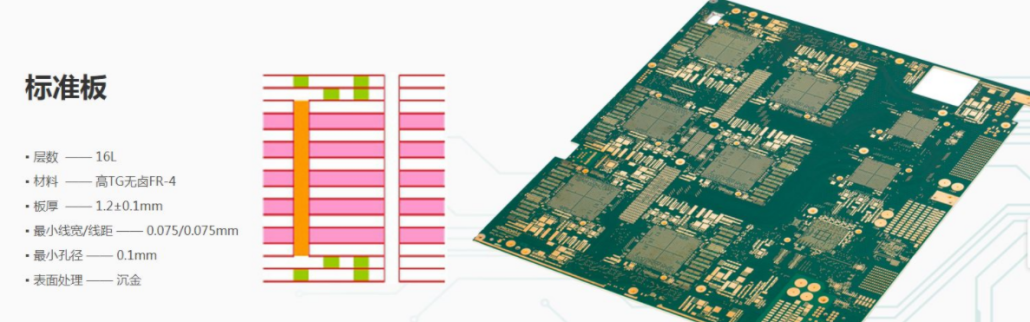

附圖三

h:指的是過孔的長度(板子的厚度)d:指得是過孔的內徑

由此我們可以得出以下結論:

1)板子厚度越薄寄生電感越小,L與h成正比關系。

2)過孔的內徑越大寄生電感越小,L與d成反比關系。

在普通PCB 設計中,過孔的寄生電容和寄生電感對PCB設計的影響較小,進行常規選擇即可。但在高速PCB中的過孔設計,通過上面對過孔寄生特性的分析,我們可以看到,在高速PCB設計中,看似簡單的過孔往往也會給電路的設計帶來很大的負面效應。為了減小過孔的寄生效應帶來的不利影響,在設計中可以盡量做到:

1)選擇合理的過孔尺寸。對于多層一般密度的PCB 設計來說,選用10/20/36(鉆孔/焊盤/POWER 隔離區)的過孔較好;對于電源或地線的過孔則可以考慮使用較大尺寸,以減小阻抗;

2)POWER隔離區越大越好;

3)PCB信號走線盡量不換層,也就是說盡量減少過孔;

4)使用較薄的PCB有利于減小過孔的兩種寄生參數;

當然,在設計時還需具體問題具體分析。從成本和信號質量兩方面綜合考慮,在高速PCB 設計時,設計者總是希望過孔越小越好,這樣板上可以留有更多的布線空間,此外,過孔越小,其自身的寄生電容也越小,更適合用于高速電路。

在高密度PCB設計中,采用非穿導孔(盲埋孔)以及過孔尺寸的減小同時帶來了成本的增加,而且過孔的尺寸不可能無限制地減小,它受到PCB 廠家鉆孔和電鍍等工藝技術的限制,在高速PCB 的過孔設計中應給以均衡考慮。

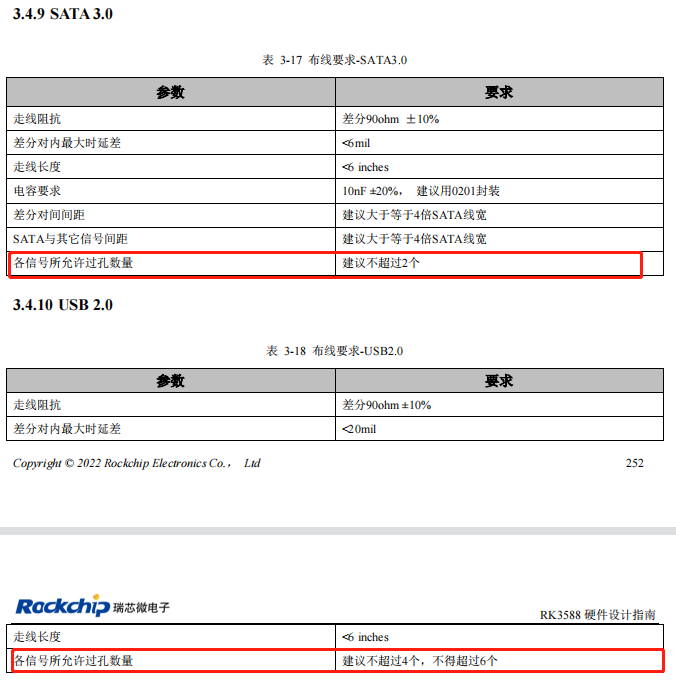

那么我們了解完了上面這些信息之后我們就知道為什么在高速PCB設計當中我們一根導線不能打過多的過孔了,過孔本身會帶來寄生電容和寄生電感,過孔打的越多所帶來的寄生電容和寄生電感的值也越大,所以這就是為什么很多數據手冊上面會寫我們布線時過孔的數量不能超過多少個(附圖三),一般我們的高速信號線采取不能超過三個過孔的原則,能不打孔就不打孔。

(附圖四)

聲明: 本文凡億教育原創文章,轉載請注明來源!投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207 ?

?

為什么電路里要擺這兩個電容?

掃碼添加客服微信,備注“入群”拉您進凡億教育官方專屬技術微信群,與眾位電子技術大神一起交流技術問題及心得~

分享點贊在看“三連”支持! 點擊“閱讀原文”查看更多干貨文章

原文標題:為什么在高速PCB設計當中信號線不能多次換孔

文章出處:【微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

-

pcb

+關注

關注

4326文章

23160瀏覽量

399951

原文標題:為什么在高速PCB設計當中信號線不能多次換孔

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

深度解析:PCB高速信號傳輸中的阻抗匹配與信號完整性

差分信號線的選擇與處理

高速PCB設計EMI防控手冊:九大關鍵步驟詳解

使用總線別名(Bus Alias)實現信號線束的功能

為什么在高速PCB設計當中信號線不能多次換孔

為什么在高速PCB設計當中信號線不能多次換孔

評論