作者:Abhilasha Kawle and Roberto Maurino

在本文中,我們將重點介紹新型連續時間Σ-Δ(CTSD)精密ADC最重要的架構特征之一:易于驅動的阻性輸入和基準電壓源。實現最佳信號鏈性能的關鍵是確保輸入源或基準電壓源本身在與ADC接口時不會損壞。對于傳統ADC,需要復雜的信號條件電路設計(稱為前端設計)來實現ADC的輸入和基準電壓源的無縫接口。CTSD ADC獨特的架構特性使該ADC與輸入和基準電壓源的接口方式得以簡化和創新。首先,讓我們快速回顧一下傳統的ADC前端設計。

傳統ADC的前端設計

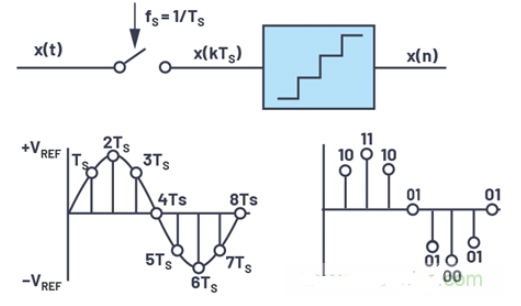

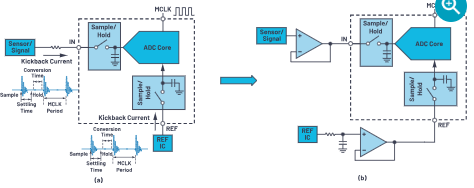

在本文中,我們將交替使用術語“傳感器”或“輸入信號”來表示ADC信號鏈的任何類型的電壓輸入。ADC信號鏈的輸入信號可以是傳感器、來自某個源的信號或控制環路的反饋。眾所周知,在傳統的離散時間Σ-Δ(DTSD)ADC和逐次逼近寄存器(SAR)ADC中,輸入和基準電壓源處的采樣網絡是開關電容負載。當開關導通時,電容器向輸入充電,當開關關閉時,電容器保持采樣值。在每個采樣時鐘邊沿,當開關將電容重新連接到輸入端時,需要一種稱為反沖電流的有限電流,將電容充電或放電至新的采樣值。電流曲線如圖1a所示。大多數傳感器和基準電壓源IC都無法驅動如此大的反沖電流,如果直接與ADC接口,輸入信號或基準電壓源損壞的可能性很高。避免這種損壞的已知解決方案之一是使用驅動緩沖放大器將輸入傳感器和基準電壓源與ADC隔離。驅動放大器應能夠吸收這些反沖電流,如圖1b所示。這就需要高壓擺率和高帶寬放大器,以支持所需的輸入充電/放電電流,并在一個采樣時間段內建立反沖。這些嚴格的要求限制了傳統ADC可用于輸入和基準電壓源路徑的緩沖放大器的選擇。

圖1.(a) 傳統ADC輸入和基準電壓源上的反沖電流,以及(b)輸入和基準電壓源上的緩沖器對反沖電流的隔離。

另一方面,輸入端需要低通抗混疊濾波器,以確保高頻噪聲和干擾源嚴重衰減,以便當它們因采樣到目標頻帶而折返時,性能不會下降。現有ADC信號鏈設計人員面臨的挑戰是微調混疊抑制和輸出建立的相反要求。DTSD ADC的前端設計帶有驅動器和抗混疊濾波器,如圖2所示。

輸入路徑由儀表放大器(儀表放大器)組成,該儀表放大器將傳感器連接到全差分放大器(FDA),最終驅動ADC。儀表放大器將輸入傳感器環境與ADC電路隔離開來。例如,傳感器的共模(CM)信號可能非常高,高達10伏。但大多數FDA和ADC不支持這種高輸入共模電壓。通用儀表放大器能夠支持寬輸入共模,同時提供適合FDA和ADC的輸出共模。儀表放大器的另一個優點是它具有高輸入阻抗。這意味著,如果傳感器不能直接驅動FDA的輸入電阻,則可以使用儀表放大器將傳感器與FDA連接。FDA本身需要高帶寬和壓擺率,以實現更快的輸出建立。干擾源抗擾度所需的有源抗混疊濾波器(AAF)圍繞FDA構建。

輸入或基準電壓源的驅動器具有相互沖突的要求:一方面,建立需要高帶寬,但另一方面,需要低帶寬來濾除噪聲和干擾源。在基準路徑上,DTSD ADC信號鏈的前端設計如圖2所示,該基準電壓源IC連接到驅動ADC基準負載的緩沖器。它還包括一個噪聲濾波器,可將基準電壓源IC和緩沖器的噪聲切斷到特定頻率以上。此濾波器的設計要求將在后面的部分中討論。基準電壓緩沖器具有高帶寬和壓擺率要求,以便更快地建立采樣事件干擾。

本系列的第1部分證明,使用精密CTSD ADC的新信號鏈可能比傳統ADC的復雜信號鏈小68%。這種尺寸減小降低了BOM,簡單性有助于信號鏈設計人員加快上市時間。

CTSD ADC 的優勢:阻性輸入和基準電壓源

在第2部分中,向信號鏈設計人員介紹了CTSD ADC架構,采用非常規的反相閉環放大器方法。如第2部分所述,CTSD ADC可以設想為具有阻性輸入和基準負載的Σ-Δ型ADC。輸入和基準結構是一個簡單的阻性負載,這意味著沒有高帶寬或高壓擺率驅動要求。第3部分展示了CTSD的獨特優勢,由于其固有的混疊抑制,CTSD具有抗干擾能力。在傳統的信號鏈設計中,衰減干擾源所需的外部混疊抑制濾波器是一個額外的挑戰,而CTSD ADC不需要外部AAF。由于CTSD ADC固有的混疊抑制特性,調制器環路的信號傳遞函數相當于衰減高頻干擾的抗混疊濾波器。由于采用阻性輸入和固有的AAF,簡化了輸入網絡,傳感器可以直接連接到ADC。在傳感器可能不具備驅動這種阻性負載的能力的情況下,可以使用儀表放大器將傳感器連接到ADC。同樣,在基準電壓源側,由于阻性負載,CTSD ADC信號鏈中消除了基準電壓緩沖器。帶儀表放大器的簡化原理圖如圖3b所示。

圖2.離散時間Σ-Δ型ADC的前端設計。

圖3.(a) CTSD 架構提供阻性輸入和基準負載,以及 (b) 直接儀表放大器,基準電壓源驅動 CTSD ADC。

圖4.(a) DTSD ADC 的輸入電流反沖,以及 (b) CTSD ADC 的連續輸入電流曲線。

圖4顯示了對CTSD ADC如何幫助簡化輸入前端設計的進一步支持。對于DTSD ADC,當輸入采樣開關改變狀態時,由于反沖而導致的輸入電流不連續性明顯可見。使用CTSD ADC,觀察到輸入電流是連續的,從而保持信號連續性。

簡化的輸入驅動設計

我們已經確定CTSD ADC的輸入驅動是阻性的。本節將討論輸入阻抗R的值在規劃ADC的輸入驅動。R在是ADC指定的噪聲性能的函數。例如,AD4134是一款精密CTSD ADC,動態范圍為108 dB,基準電壓源為4 V,輸入阻抗為6 kΩ差分。這表明,當滿量程8 V p-p差分輸入信號施加到ADC時,峰值電流要求為1.3 mA p-p。如果傳感器可以支持輸入電流V在/R在,然后可以直接連接到ADC。需要一個簡單的放大器來驅動這種阻性負載的情況是:

當傳感器不具備驅動能力以提供 V 峰值電流時在/R在.

信號鏈設計要求傳感器輸出需要增益或衰減。

將輸入傳感器環境與ADC電路隔離。

傳感器具有較大的輸出阻抗。

傳感器遠離ADC,走線可能會給輸入增加很大的電阻。

在場景 4 和 5 中,額外的外部電阻 R 兩端會出現壓降s,表示ADC輸入端的信號丟失。這會導致信號鏈的增益誤差和誤差隨溫度的漂移,從而導致性能下降。溫度增益漂移是由外部電阻和內部電阻的不同溫度系數引起的。這個問題可以通過一個簡單的放大器來解決,以隔離額外的外部電阻。由于該放大器的驅動負載是阻性的,因此該放大器的選擇標準為:

輸入阻抗:為避免信號衰減或丟失,傳感器的阻抗應與放大器輸入阻抗相匹配。

輸出阻抗:輸出阻抗應足以驅動ADC的阻性輸入負載。

輸出類型:作為一般信號鏈設計準則,建議采用差分信號策略以獲得最佳信號鏈性能。差分輸出型放大器或單端至差分輸出的設計技術最適合此任務。此外,為了獲得最佳性能,最好將此差分信號的共模設置為 V裁判/2.

可編程增益:輸入信號通常被增益或衰減,以將其映射到ADC的滿量程范圍。這是因為當使用ADC的整個輸入范圍時,可以從ADC信號鏈獲得最大性能。

根據應用的不同,該放大器可以是儀表放大器或FDA,也可以是構成差分輸出放大器的兩個單端運算放大器的組合。由于沒有高壓擺率或高帶寬的嚴格要求,ADI的放大器產品組合有多種選擇,可根據應用要求驅動該CTSD ADC。此外,放大器性能參數通常由阻性負載指定,這使得選擇更加簡單。

例如,對于AD4134,LTC6373是具有可編程增益選項和全差分輸出的性能兼容型儀表放大器的一個選項。該儀表放大器為輸入源提供高阻抗,可輕松驅動差分6 kΩ阻抗,噪聲和線性度性能與ADC相當。憑借其廣泛的輸入共模支持和可編程增益選項,任何具有寬信號幅度范圍的傳感器或輸入信號都可以與ADC接口。采用這種直接儀表放大器驅動器的輸入前端設計示例如圖4所示。

圖5.輸入前端設計,CTSD ADC 直接連接到儀表放大器。

另一個例子是采用全差分驅動器放大器(如 LTC6363-0.5 / LTC6363-1 / LTC6363-2)的低電壓簡單前端設計,基于所需的增益或衰減,如圖 6 所示。可以使用 FDA 的情況是,傳感器能夠驅動 FDA 的阻性負載,但為單端類型,或者具有 ADC 不支持的共模,或者信號鏈中的增益/衰減要求很小。

圖6.輸入前端設計,CTSD ADC直接連接到全差分放大器。

另一個示例包括一個低BOM選項,用于使用兩個單端運算放大器在ADC上將單端輸入轉換為全差分信號,如圖7所示。

圖7.輸入前端設計,帶有一個帶有兩個單端放大器的CTSD ADC。

還有許多其他例子,例如使用單端儀表放大器和單端運算放大器的組合來構建差分輸出前端,用于非常高的輸入CM或低驅動強度的單端型傳感器。可以根據性能、面積和 BOM 要求選擇任何此類組合,以更好地適應應用。

與AD4134兼容的其他放大器列表包括:

運算放大器:ADA4625-2、ADA4610-2、AD8605和ADA4075-2。

全差分放大器:ADA4940-2、LTC6363 和 ADA4945-1。

儀表放大器:AD8421。

ADI公司的放大器選擇指南可用于選擇適合應用的最佳放大器。例如,對于音頻測試設備等高線性度應用,建議使用ADA4945-1。對于光電二極管應用,最重要的考慮因素是非常高的輸入阻抗,可以使用ADA4610-2等跨阻放大器(TIA)。

CTSD ADC大大簡化了輸入前端,讓我們來看看參考驅動器的類似簡化。

簡化的參考設計

ADC輸出表示其輸入和基準電壓源,如公式1所示。

其中 V在= 輸入電壓電平,VREF模數轉換器= ADC 的基準電壓源,N = 位數,D外= ADC 數字輸出。

公式1表明,為了獲得最佳ADC性能,干凈、無損壞的基準電壓源非常重要。受基準電壓源誤差影響的ADC信號鏈的三個主要性能指標是:

信噪比:影響SNR的主要噪聲因素是輸入路徑、ADC本身和基準電壓源。對于ADC輸出端的目標總噪聲(考慮其他噪聲貢獻因素),基準噪聲的預算通常為獨立ADC輸出噪聲的1/3或1/4。基準電壓源或基準電壓緩沖器的噪聲通常高于ADC。如果我們查看任何數據手冊,了解基準電壓源或基準電壓緩沖器IC、頻譜噪聲密度或噪聲密度,是規范之一。如果我們重新審視噪聲計算基礎知識,則基準電壓源或基準電壓緩沖器輸出端的總噪聲由下式

給出 我們無法控制噪聲

密度因為它對于所選的引用或緩沖區是固定的。唯一可控的參數是噪聲帶寬(NBW)。為了達到低基準電壓源噪聲,我們降低了基準電壓源或基準電壓緩沖器的噪聲帶寬。這通常通過將一階低通RC濾波器連接到ADC來完成,如圖8所示。對于一階RC濾波器,NBW由

ADC基準電流I

模數轉換器,流過濾波電阻R會導致壓降,從而改變ADC的實際基準值。因此,建議選擇較小的R值和較大的C值,以滿足NBW對低參考噪聲的要求。

增益誤差:從公式1中可以明顯看出,VREF是模數轉換器確定輸出到輸入傳遞函數的斜率,就像在直線方程中一樣,例如 y = mx。該斜率也稱為ADC的增益。因此,如果基準電壓源發生變化,ADC的增益也會發生變化。

線性:對于傳統的DTSD ADC和SAR ADC,基準電流和伴隨的反沖取決于輸入信號。因此,如果基準電壓源在下一個采樣時鐘邊沿之前沒有完全建立,則基準電壓源上的誤差將取決于輸入并導致非線性。在數學上,VREF模數轉換器然后表示為

參考公式1,ADC輸出D

外將具有基于ADC輸入的各種高階依賴性,這種依賴性會導致諧波和積分非線性。因此,對于傳統ADC,很難要求基準電壓緩沖器的高壓擺率和帶寬在采樣時間段內建立基準電壓輸出。

如果我們仔細分析SNR和線性度,就會發現基準電壓源或基準電壓源緩沖器需要滿足相當相互沖突的要求。噪聲的帶寬要求較低,而建立速度較快的帶寬要求較高。調整這兩個要求之間的精細平衡一直是信號鏈設計人員面臨的一個由來已久的挑戰。一些最新的DTSD ADC和SAR ADC片內集成了基準電壓緩沖器,以簡化信號鏈設計的一個步驟,但這些解決方案需要額外的功率或會帶來一定的性能損失。由于CTSD ADC不需要快速建立緩沖器,并且具有阻性輸入,無需快速建立驅動器,因此能夠避免這些性能問題。

CTSD ADC 通過以下特性和設計改進解決了參考驅動器挑戰:

當阻性負載在基準上時,每個采樣時鐘邊沿都沒有建立要求。這允許設計人員將基準電壓源IC直接連接到ADC,而無需專用基準電壓緩沖器。

專利設計技術使基準電流獨立于輸入,并強制ADC的基準電流I模數轉換器基本恒定。當可能需要RC濾波器來降低基準噪聲時,這是有益的,如圖8所示。結果是電阻兩端的壓降恒定,VREF中沒有增加輸入相關項模數轉換器.設計用于根據R值和基準引腳處測得的電壓,在系統級對增益誤差進行數字校正。因此,這個簡單的參考接口不會有增益或線性誤差。

圖8.阻性基準負載,可通過無源濾波器直接連接到基準 IC。

盡管已經實施了一項規定,以數字方式校正R兩端壓降引起的誤差,但人們可能想知道這是否會限制CTSD ADC作為實際基準電壓源(VREF模數轉換器) 的 ADC 將小于應用的 VREF。

例如,如果基準電壓源IC的VREF經過修整并設置為4.096 V,ADC基準電流(I模數轉換器) = 6 mA,則,對于R = 20 Ω的濾波器電阻,ADC的實際基準電壓源(VREF模數轉換器) 為 3.967 V。如公式5所示。在這種情況下,在這種情況下,當規格V p-p(其大于2 × VREF模數轉換器) 施加在 ADC 的輸入端,是否有可能使 ADC 的輸出飽和?答案是否定的。CTSD ADC 設計用于支持 ADC 引腳 REFIN 處超出基準電壓源幾 mV 的輸入幅度。在我們的AD4134示例中,這種擴展范圍將電阻值限制為最大值25Ω。然后選擇噪聲濾波器的C值以滿足計算的噪聲帶寬。

簡化參考驅動器設計

CTSD ADC簡化了基準電壓源驅動的設計,但在為濾波器選擇正確的R,然后對電阻兩端的壓降進行數字增益誤差校正時,還需要考慮其他因素。數字增益誤差校正(也稱為校準)是許多ADC的常見特性,它使信號鏈設計人員能夠自由地補償ADC數字輸出端信號鏈中的誤差。因此,它可能不需要增加設計步驟,而是重復使用相同的算法,這在許多信號鏈中很常見。從表面上看,電阻的選擇似乎并不是一個特別復雜的設計步驟,但有一個警告:壓降的溫度依賴性。外部濾波電阻和I模數轉換器隨溫度漂移不同,進而導致 VREF模數轉換器以及ADC的增益隨溫度漂移。對于具有嚴格增益漂移要求的應用,粗略的解決方案包括定期校準信號鏈。但是,由于CTSD技術,一個更好和創新的解決方案成為可能。由于ADC基準負載電流是片內所用電阻材料的常數和函數,因此可以在片內為濾波電阻R提供20 Ω,如圖9所示。

圖9.片內基準噪聲濾波器電阻,簡化了CTSD ADC的基準前端設計。

在新的前端設計中,基準IC連接在REFIN引腳上,濾波電容連接在REFCAP引腳上,形成基準IC噪聲的噪聲濾波器。由于片上電阻R和I的電阻模數轉換器兩種功能都是同一電阻材料,REFCAP 上沒有溫度漂移 (VREF模數轉換器).AD4134還采用獲得專利的片內基準電壓源校正算法,對片內電阻兩端的壓降進行數字自校準。因此,參考驅動器設計現在簡化為根據性能要求選擇基準IC和電容值。

ADR444是低噪聲基準電壓源IC之一,可用作CTSD ADC的配套產品。AD4134的數據手冊提供了有關電容值選擇以及內部和外部數字增益校準的更多詳細信息。

結論

CTSD ADC消除了實現最佳精密性能和簡化前端設計的許多障礙。在接下來的文章中,我們將介紹如何將CTSD ADC調制器內核的輸出處理成最終的數字輸出格式,以供外部數字控制器使用,以實現最佳處理。根據本系列中解釋的Σ-Δ基礎知識,我們知道調制器輸出不能直接處理,因為它的采樣速率要高得多。需要將采樣速率降低到應用所需的輸出數據速率(ODR)。接下來,我們將介紹一種新穎的異步采樣速率轉換(ASRC)技術,使信號鏈設計人員能夠在任何所需的ODR下調整最終ADC輸出,并超越將ODR限制為采樣頻率倍數的古老限制。

審核編輯:郭婷

-

傳感器

+關注

關注

2553文章

51395瀏覽量

756602 -

放大器

+關注

關注

143文章

13630瀏覽量

214213 -

adc

+關注

關注

99文章

6533瀏覽量

545758

發布評論請先 登錄

相關推薦

如何使用連續時間Σ-ΔADC,簡化信號鏈來解決采樣問題

CTSD精密ADC—第4部分:輕松驅動ADC輸入和基準電壓源,簡化信號鏈設計

轉換器簡化RF信號鏈-汽車收音機的演變歷程

驅動ADC輸入時簡化設計流程的方法

高速轉換器如何簡化RF信號鏈?

AD8275 ADC驅動器,具有電平轉換功能,可簡化信號調理

簡化RF組件評估和信號鏈設計

緩沖的 8 通道 ADC 輸入簡化了傳感器接口

具 Easy Drive 輸入電流消除功能的 24 位、16 通道增量累加 ADC 簡化前端信號調節

LTC2480 - 采用 Easy Drive 輸入電流消除技術的 16 至 24 位 ?∑ ADC 系列簡化前端信號調節

CTSD精密ADC:輕松驅動ADC輸入和基準電壓源,簡化信號鏈設計

利用ADS125H02簡化±10V PLC模擬輸入模塊信號鏈

簡化ADC輸入和基準驅動,簡化信號鏈設計

簡化ADC輸入和基準驅動,簡化信號鏈設計

評論