在當今的數據采集系統(DAQ)中,性能界限不斷被突破。系統設計人員需要更高的速度、更低的噪聲和更好的總諧波失真(THD)性能,所有這些都是可能的,但沒有一個是免費的。這些性能改進通常以更高的工作電流為代價,進而導致更大的功耗。然而,在許多應用中,對功耗的敏感性也是一個日益受到關注的問題。原因多種多樣。它可能是一個由紐扣電池運行的遠程系統,其中主要關注的是電池壽命,或者可能是一個多通道系統,其中來自高通道數和高電路密度的熱量集中會導致溫度引起的漂移問題。無論哪種情況,最小化電流消耗和功耗都至關重要。系統設計人員必須在高性能和低功耗的競爭優先級之間取得平衡。實現解決方案的一種途徑是通過稱為動態功率縮放 (DPS) 的過程。

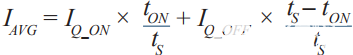

簡單地說,DPS是在需要時動態啟用電子元件并在不需要時禁用它的過程。圖1所示為典型的基于SAR ADC的數據采集子系統。SAR ADC的關鍵屬性之一是其功率與吞吐速率成比例,使其成為功耗敏感型應用非常有吸引力的選擇。從歷史上看,ADC驅動器和基準電壓緩沖器沒有共享SAR所享有的自動功率調節功能。它們通常在系統運行時通電并啟用,從而消耗多余的功率。假設使能時間足夠快,則可以動態驅動放大器掉電引腳,以在ADC轉換之間禁用放大器。這就是動態功率縮放。通過將DPS施加到放大器上,可以大大降低其平均電流消耗。對于DPS,放大器靜態電流是驅動掉電引腳占空比的函數。理論平均靜態電流由下式給出

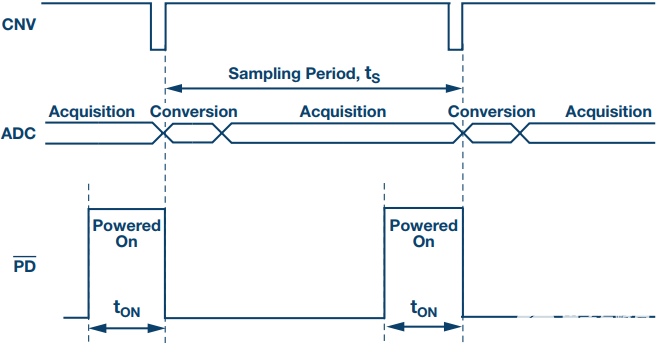

哪里:

我平均是平均DPS靜態電流

我Q_ON放大器的靜態電流是否已啟用

我Q_OFF放大器的靜態電流是否被禁用

t上是放大器使能的時間

tS是采樣頻率周期

圖1.基于SAR ADC的數據采集子系統框圖

在本文的其余部分,ADC驅動放大器將是重點,但DPS概念也可以應用于基準電壓緩沖器,結果類似。

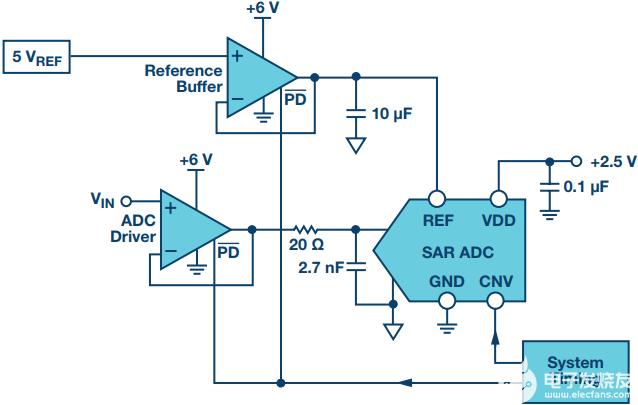

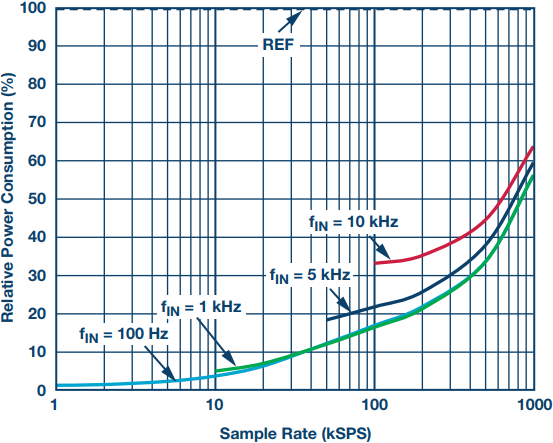

圖2顯示了ADC驅動放大器持續使能時的理論效率改進情況。f 處的垂直參考線R表示ADC的功耗等于持續使能的驅動放大器的功耗時的采樣頻率。在較低的采樣速率下,放大器主導功耗,在較高的采樣速率下,ADC主導功耗。參考頻率(fR) 將根據放大器和所選 ADC 的功耗而變化,但基本概念保持不變。顯示了功率調節的同一放大器在三個不同值的t下相對效率改進上.正如預期的那樣,較短的t上在給定采樣率下提高效率,并允許在更高的采樣率下使用 DPS。陰影區域表示,增量縮短的改進面積最大 t上通常向下延伸至低于f的十年左右R.當采樣率繼續降低到該點以下時,實現了最大的整體節能,但進一步縮短了上可以忽略不計,因為功耗逐漸接近掉電或禁用狀態的功耗。

圖2.選定溫度下DPS的理論放大器功耗上(相對于放大器持續啟用)。

為了使用DPS實現最佳性能,系統定時和最小值的確定上至關重要。

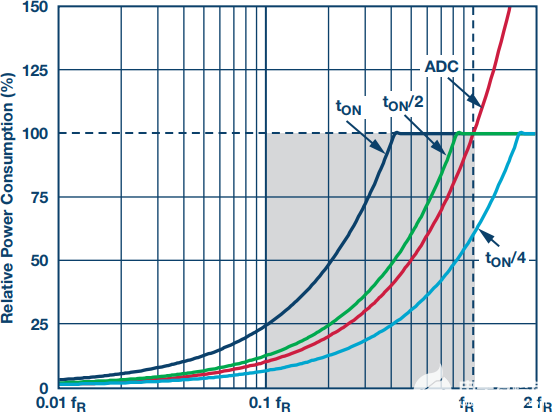

圖3顯示了ADC和驅動器放大器的簡化時序圖。圖1所示的系統時序模塊(FPGA、DSP和微控制器)提供適當定時的ADC轉換啟動(CNV)和放大器關斷(PD)信號。SAR ADC在CNV的上升沿啟動轉換。放大器在ADC采集階段上電一段時間(t上)之前,然后與CNV的上升沿同步斷電。但是正確的時間段是多少上?

圖3.放大器和ADC控制信號的簡化時序圖。

雖然圖 2 說明了使用任意時間對 t 進行的概念上,它清楚地表明,只有當最小值上被使用。這是放大器在ADC轉換之前必須使能的最短時間,以確保獲得準確的結果。任何短于此時間都會導致SNR或THD的侵蝕,而任何更長的時間都不會導致任何性能改進。在實踐中,最小值 t上在采樣率范圍內不是恒定的,必須根據經驗確定的獨特應用。最小值 t上將因放大器和系統而異。例如,在圖1電路中使用ADA4805-1和AD7980的放大器/ADC組合,最小值為”上隨著采樣速率的增加而降低,在1 kSPS時通常需要~4 μs,在1 MSPS時只需要~600 ns。在低采樣速率下,由于掉電狀態的時間延長,較長的周期為內部放大器節點提供了更多的放電時間,從而導致更長的導通時間。相反,較短的較高采樣率周期不允許進行盡可能多的內部放電。事實上,隨著采樣速率的增加,放大器的有限關斷時間將變得比掉電狀態下的時間更長。實際上,放大器在完成關閉之前重新打開。這看起來像是人為地快速開啟時間,但在性能數據顯示沒有下降時會得到驗證。

預測潛在的節能時要考慮的最后一點是輸入信號頻率的影響。到目前為止,DPS的概念已經使用給定放大器的靜態電流計算出來。將信號施加到放大器輸入端時,動態電流也會隨著輸入信號頻率的增加而增加。如果輸入頻率足夠低,則影響無關緊要。隨著頻率的增加,放大器輸出端的RC網絡呈現出更重的負載,需要放大器提供更多的電流來處理信號。

使用前面提到的ADA4805-1和AD7980,將這些概念放在一起,得到圖4中的曲線。該圖顯示了動態功率調節的ADC驅動器放大器在持續使能時相對于同一放大器的功耗(以百分比表示)。繪制了所選輸入頻率的DPS效率圖,以說明較高輸入頻率對功耗的影響。最小值 t上針對從 1 kSPS 到 1 MSPS 的多個采樣速率確定,定義為最短的上這會導致放大器持續使能的情況下SINAD(信噪比和失真)衰減<0.5 dB。該圖顯示,在低采樣率下處理慢速輸入信號時,可實現高達95%的節能。但更重要的是,對于更高吞吐量的系統,潛在的節省仍然很大,在100 kSPS時高達65%,在1 MSPS時高達35%。需要注意的是,圖4反映了連續采樣系統中單個單位增益緩沖器的性能。但是,如前所述,這些DPS概念可以很容易地應用于基準電壓緩沖器,并期望獲得類似的結果。

圖4.具有動態功率縮放的相對放大器功率—實驗結果。

雖然DPS是一個相對較新的概念,并且需要考慮設計和時序考慮因素,但初步結果是有希望的。有一點非常清楚,對更高性能和更低功耗的渴望將持續到未來,這將進一步增加對創造性低功耗解決方案的需求。

審核編輯:郭婷

-

放大器

+關注

關注

143文章

13634瀏覽量

214226 -

驅動器

+關注

關注

53文章

8272瀏覽量

147075 -

DAQ

+關注

關注

6文章

92瀏覽量

32289

發布評論請先 登錄

相關推薦

《Visual C# 2008程序設計經典案例設計與實現》---動態打開、顯示和縮放圖像

8168縮放問題,請問mpsclr是不是固定縮放到1920*1080?

是否可以針對WiFi調整PHY的動態速率縮放算法呢?

用TPS62200作為OMAP1510的動態電壓縮放器

基于概率隨機裁剪的圖像縮放算法

AN-1289:在無動態功率控制的應用中使用AD5755和類似的動態功率控制DAC

AD7768-1:DC至204 kHz,動態信號分析,帶電源縮放功能的精密24位ADC數據表

使用縮放布局案例效果演示

使用HLS封裝的縮放IP來實現視頻圖像縮放功能

具有動態電壓縮放功能的雙同步降壓DC-DC變換器LM3370數據表

動態功率縮放簡介

動態功率縮放簡介

評論