1.前言

bind是systemverilog中一個重要的知識點,很多時候能夠在驗證中發揮重要的作用,今天就針對這個知識點做一個梳理,希望能幫助到大家。

2. 為什么需要bind

當RTL已經編寫完畢,驗證工程師有責任添加斷言時。RTL設計者不希望驗證工程師為了添加斷言而修改其RTL,于是SystemVerilog的綁定特性應運而生。bind可以實現驗證和設計的分離,將module/interface/program綁定到任意的設計模塊或者其特定例化中,可以將interface直接bind到top module中進行例化。bind可以使得驗證工程師不改動或最小的改動原有設計代碼和文件結構,就能夠實現對設計代碼的檢查。

SystemVerilog斷言(SVA)可以直接添加到RTL代碼中,也可以通過bindfile間接添加。實踐表明,大多數的斷言最好是使用bindfile添加。在獨立的文件中寫入所有必需的斷言,使用bind就可以將斷言文件的端口與測試代碼中RTL的端口/信號綁定。這是多么酷的一個功能。

3. bind的語法

bind用于指定module、interface、program的一個或多個實例化,而無需修改目標文件的代碼。因此,封裝在module、interface、program中的插入代碼或斷言可以以非侵入方式(non-intrusive manner)在目標模塊或模塊實例中實例化。類似地,封裝在接口中的檢測代碼可以綁定到目標接口或接口實例。

SVA檢驗器通過關鍵字bind可以與設計中的任何模塊(module)或者實例(instance)綁定。將SVA檢驗器可以與模塊、模塊的實例或者一個模塊的多個實例進行bind綁定。實現綁定時,使用的是設計中的實際信號,語法如下:

bind ;

這里注意以下幾點:

[1] 通過bind語句將SVA的checker與設計模塊綁定,等價于將SVA例化到設計模塊中。

[2] bind不僅可以將斷言與設計module綁定,也可以將任意兩個模塊之間進行綁定。

[3] bind功能可用于以下位置:

4. bind的具體應用實例

4.1 通過模塊名實現綁定

語法:bind module_name sva_name sva_inst;

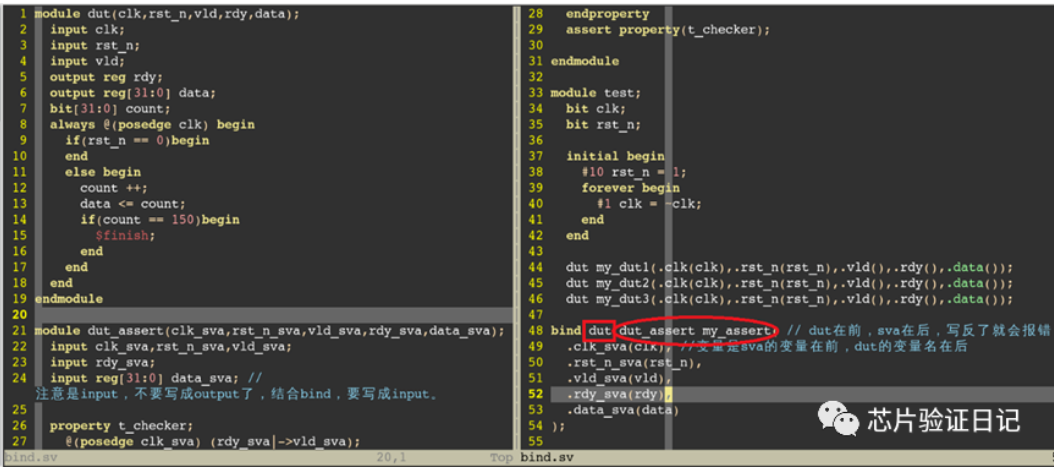

具體實例的代碼如下圖所示:

針對上圖中代碼的一些解釋:

[1] dut 是module的名字

[2] dut_assert 是內部包含 property 以及斷言的模塊,可以是 module 或者 interface

[3] my_assert是dut_assert的實例化名字

[4] 括號中的信號clk/rst_n/vld/rdy是dut的端口信號,并且連接到dut_assert的對應端口

[5] 包含斷言的interface/module,其端口信號的方向均為input,也就是說property中包含的信號都是從該interface/module外部給進來的。

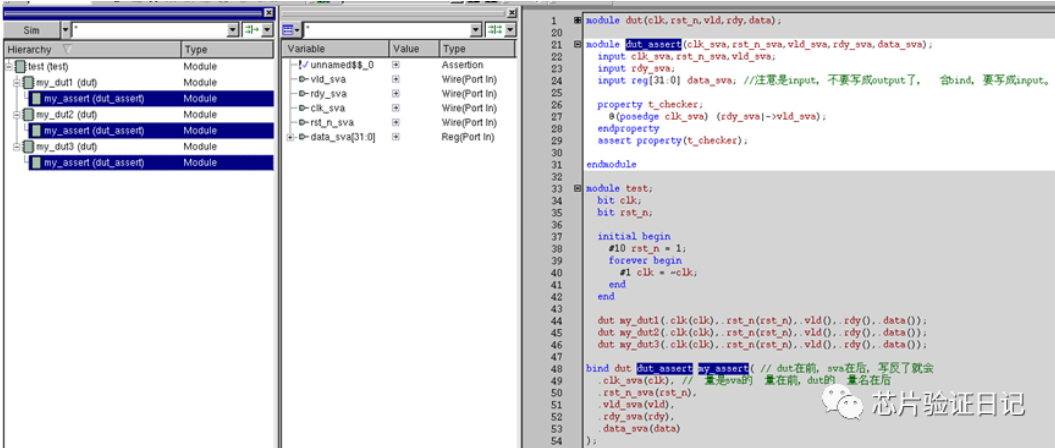

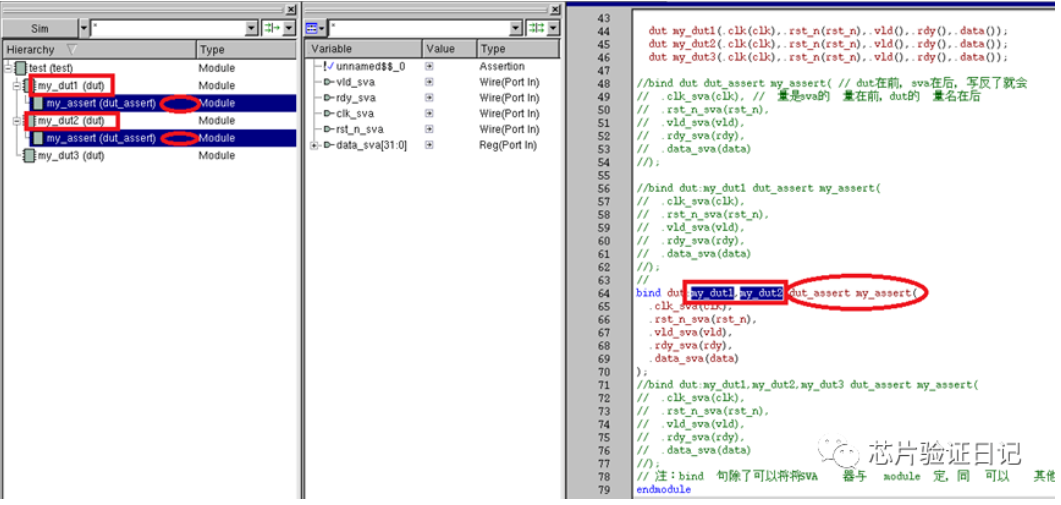

bind成功后,斷言會關聯到module_name的所有例化示例,sva_inst路徑位于rtl_inst下一層,參考下面仿真器中的hierarchy結構:

具體的實驗源代碼和腳本,請參考分享的網盤鏈接中的basic目錄。

4.2 通過模塊實例化名實現綁定

語法:bind module_name:mudule_inst_name sva_name sva_inst;

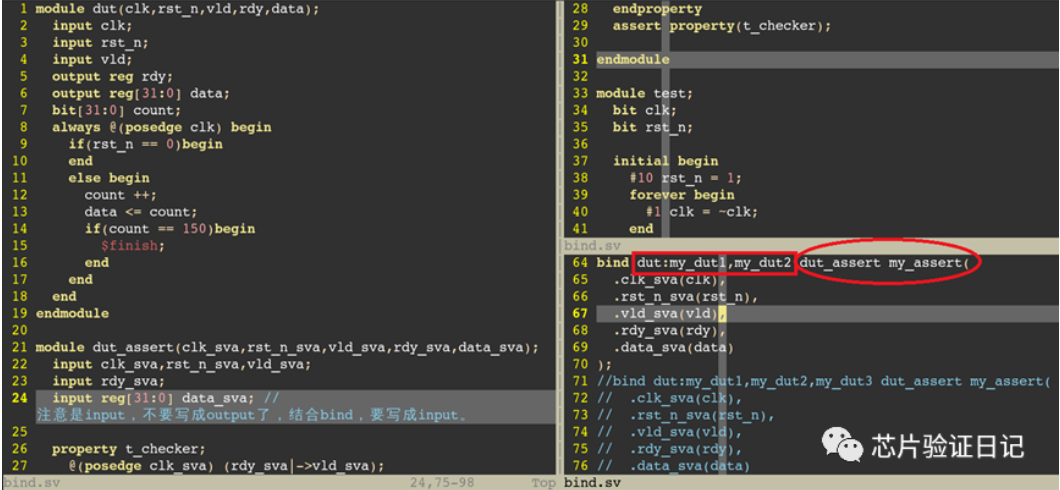

具體實例的代碼如下圖所示:

注意跟4.1的區別:

上圖中第64行中,對dut的實例化my_dut1和my_dut2進行bind。

下圖中的hierarchy結構圖和上圖中的代碼是正確對應的,這也很好理解。

具體的實驗源代碼和腳本,請參考分享的網盤鏈接中的basic目錄。

4.3 通過模塊名實現bind的另一個例子

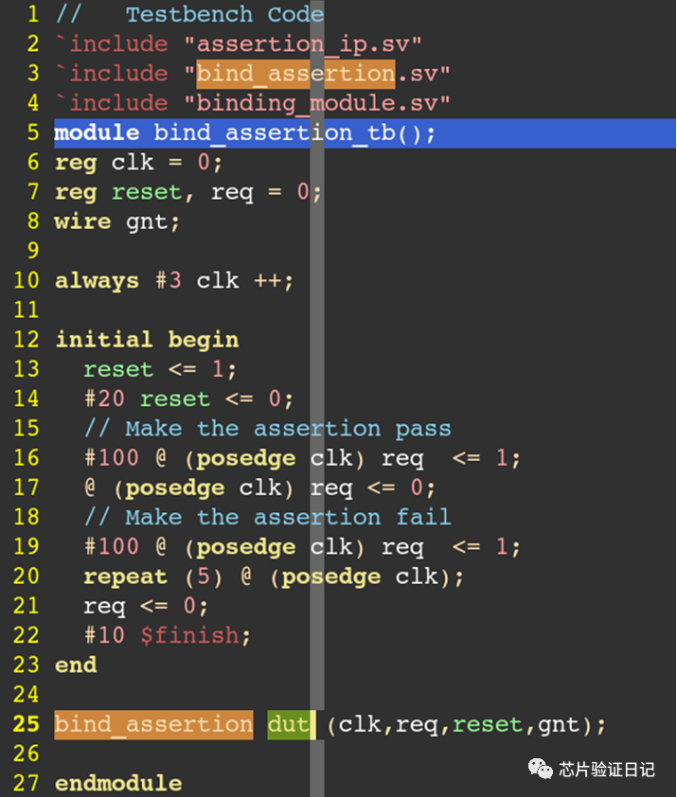

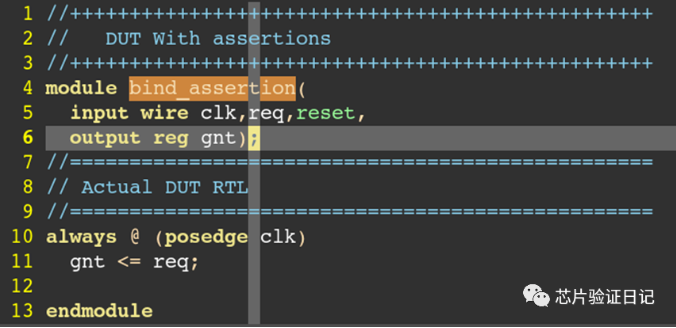

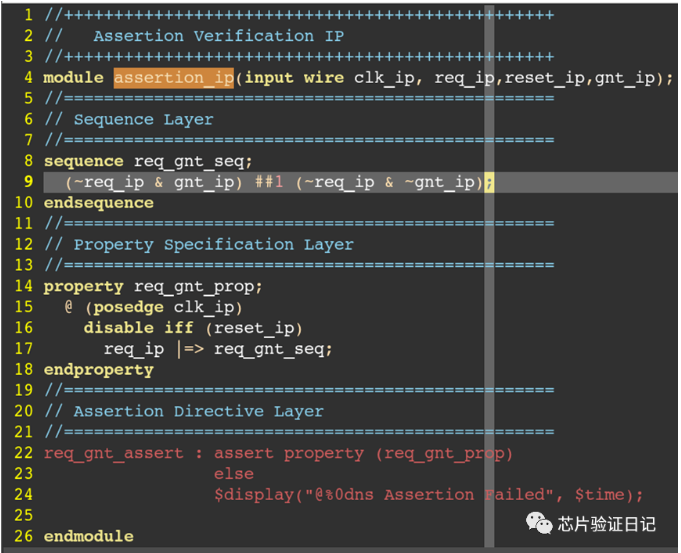

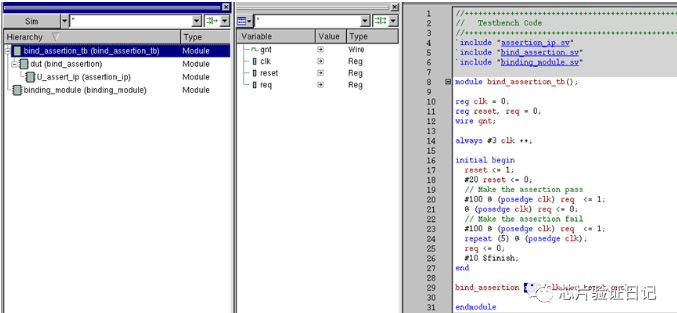

前面的例子對bind的基本用法已經講的很清楚了,下面的例子只是想說明下面這一點:可以將需要的所有斷言寫入獨立的文件中,使用bind也可以將斷言文件的端口與測試臺代碼中RTL的端口/信號綁定。下面是這個例子的詳細代碼截圖。

下圖是testbench(最大的module)的代碼截圖:

下圖是DUT代碼的截圖:

下圖是斷言模塊:

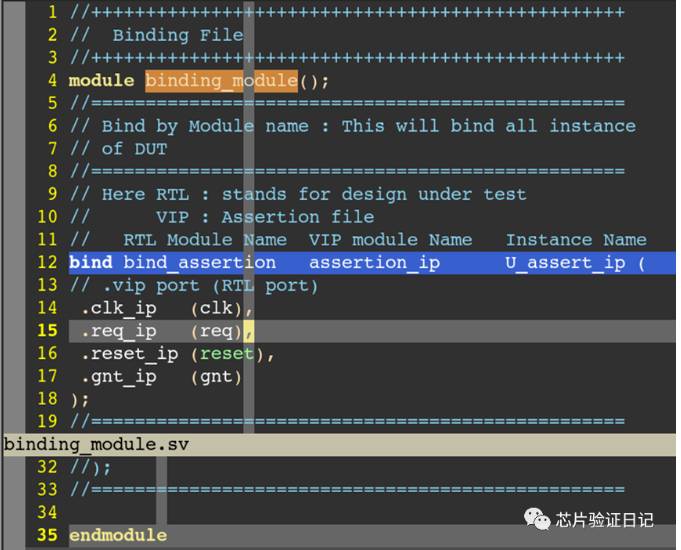

如下圖所示,bind功能單獨寫在一個獨立module中,這種用法EDA工具也是支持的,這是這個例子跟上面例子的最大區別。

注意理解下圖中的hierarchy結構,

具體的實驗源代碼和腳本,請參考分享的網盤鏈接中的asic-world目錄。

4.4 參數化bind的實例

從前面的例子,我們可以很好的理解SV中的綁定命令允許向模塊添加新功能,通常用于向RTL模塊添加新的檢查。再往深里研究一下,bind還可以繼承參數,綁定模塊可以根據其使用位置參數化自身。

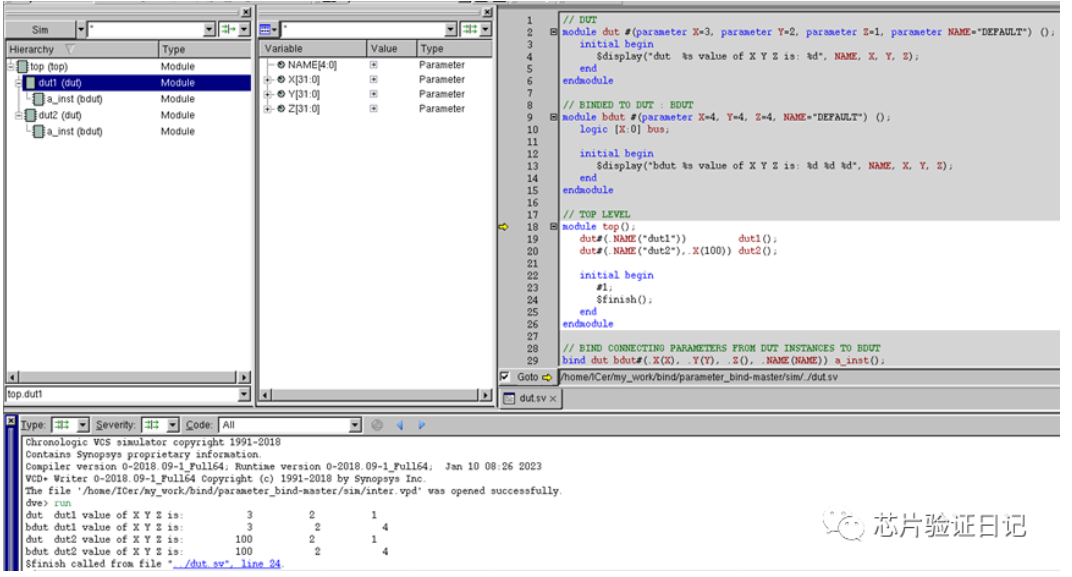

下面的代碼用于演示bind的參數化特性,該特性允許綁定模塊(bdut模塊)根據其使用位置參數化自身。

當查看bind語句(下圖中第29行)時,它使用的所有參數都沒有在第29行定義,但當綁定被激活時,它就有了參數化自身的作用域。其實也很好理解,我們可以想象把第29行粘貼到“dut”中;在那里所有的定制參數都將流到“bdut”的實例化中。

需要注意的一個特殊情況是,第29行的“.Z()”參數化為空。這允許“bdut”的默認值接管。第10行根據參數化在“bdut”中創建“邏輯[X]總線”。這可用于生成參數化覆蓋點或其他需要參數化的功能。

具體的實驗源代碼和腳本,請參考分享的網盤鏈接中的parameter_bind-master目錄。

5. 通過interface實現bind功能

這在用法上跟上面模塊的例子一模一樣,只是把module換成interface即可,這里就不再贅述了。

6. 贈送實驗源碼和Makefile腳本

關注微信公眾號《芯片驗證日記》,后臺回復”bind”,可得本文所有的源碼和Makefile腳本對應的百度鏈接,目錄如下圖所示,這樣你就可以在本地復現本文中的所有。

-

Verilog

+關注

關注

28文章

1351瀏覽量

110400 -

System

+關注

關注

0文章

165瀏覽量

37078 -

源碼

+關注

關注

8文章

652瀏覽量

29458 -

Bind

+關注

關注

0文章

5瀏覽量

7618

發布評論請先 登錄

相關推薦

關于typedef的用法總結

Bind源代碼包安裝

SystemVerilog中枚舉類型的使用建議

SystemVerilog中ifndef如何避免重復編譯

SystemVerilog中bind用法總結+送實驗源碼和腳本

SystemVerilog中bind用法總結+送實驗源碼和腳本

評論