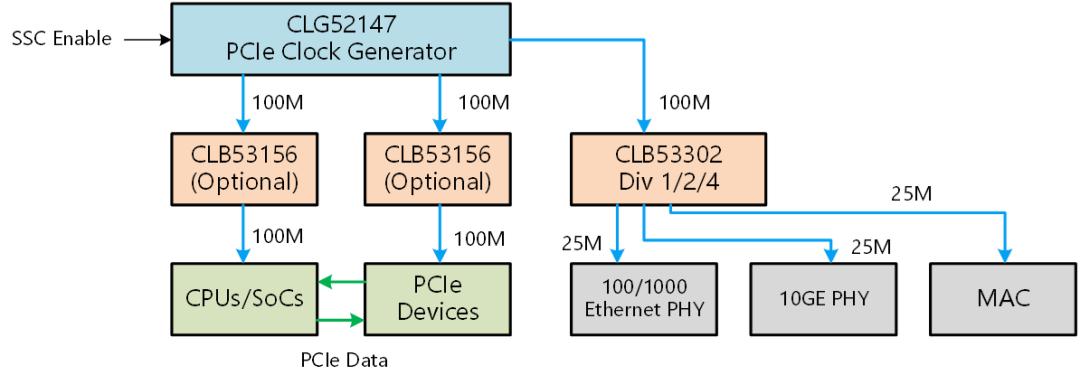

核芯互聯日前推出了滿足PCI Express(PCIe)5.0規范的完整時鐘解決方案,全系列產品完全兼容 PCIe Gen 5 通用時鐘、分離參考無展頻(SRNS)和分離參考獨立展頻(SRIS)架構,整體方案能夠提供同類產品領先的抖動性能,留有顯著的設計余量,同時向下兼容PCIe Gen1/2/3/4。

核芯互聯日前推出了滿足PCI Express(PCIe)5.0規范的完整時鐘解決方案,全系列產品完全兼容 PCIe Gen 5 通用時鐘、分離參考無展頻(SRNS)和分離參考獨立展頻(SRIS)架構,整體方案能夠提供同類產品領先的抖動性能,留有顯著的設計余量,同時向下兼容PCIe Gen1/2/3/4。

方案的所有器件全面支持SSC擴頻技術以顯著地降低EMI。方案的所有器件都可以工作在-40~125℃溫度范圍,并在AEC-Q100認證中。

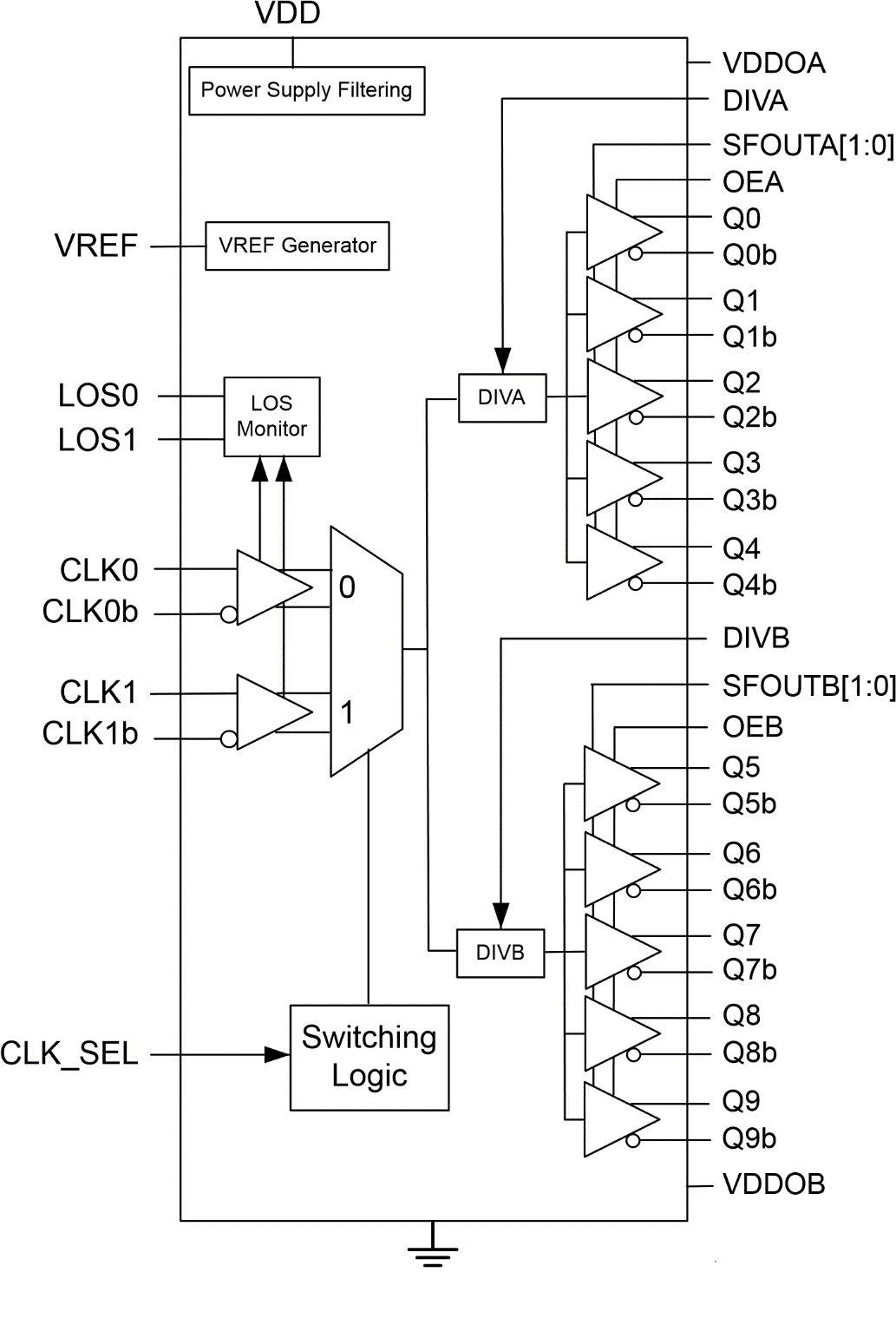

其中時鐘生成器CLG52147 PCIe可以提供9路100MHz獨立的LP-HCSL時鐘輸出,在PCIe Gen 5.0 Common Clock架構下,RMS Jitter典型值僅為10fs;時鐘Buffer CLB53156可以提供6路PCIe 5.0兼容輸出,在PCIe Gen 5.0 Common Clock架構下附加抖動僅為6fs;時鐘Buffer CLB53302/53305可以提供多達10路任意形式差分或者20路任意形式單端輸出,并且提供兩組獨立的1/2/4分頻,在100MHz輸入時鐘的條件下,可以獨立地輸出兩組(每組5個差分或者10個單端)100MHz、50MHz或者25MHz時鐘,充分簡化了了PCB設計。

CLG52147

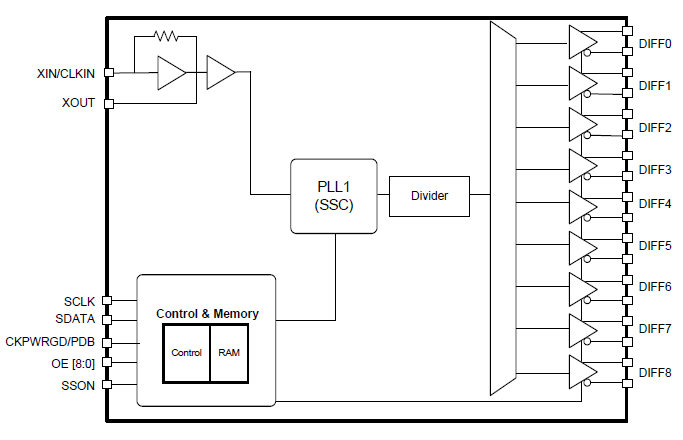

CLG52147是一顆高性能的PCIe參考時鐘發生器,使用25MHz晶振或時鐘輸入,采用3.3V供電,符合PCIe Gen1/2/3/4/5規范,支持SRNS和Common Clock架構,支持SSC以降低EMI。CLG52147具有業界領先的抖動指標,PCIe Gen 5 CC的RMS Jitter 典型值為10fs。CLG52147有9個獨立的控制引腳用來開啟或關斷輸出以降低功耗。

CLG52147功能框圖

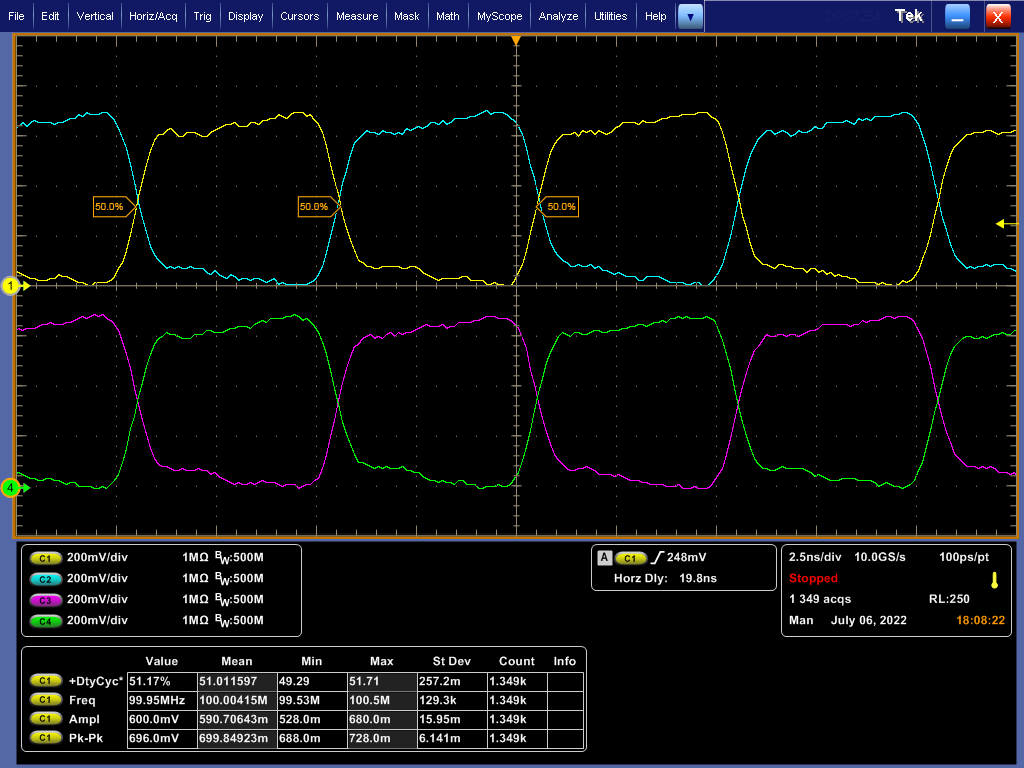

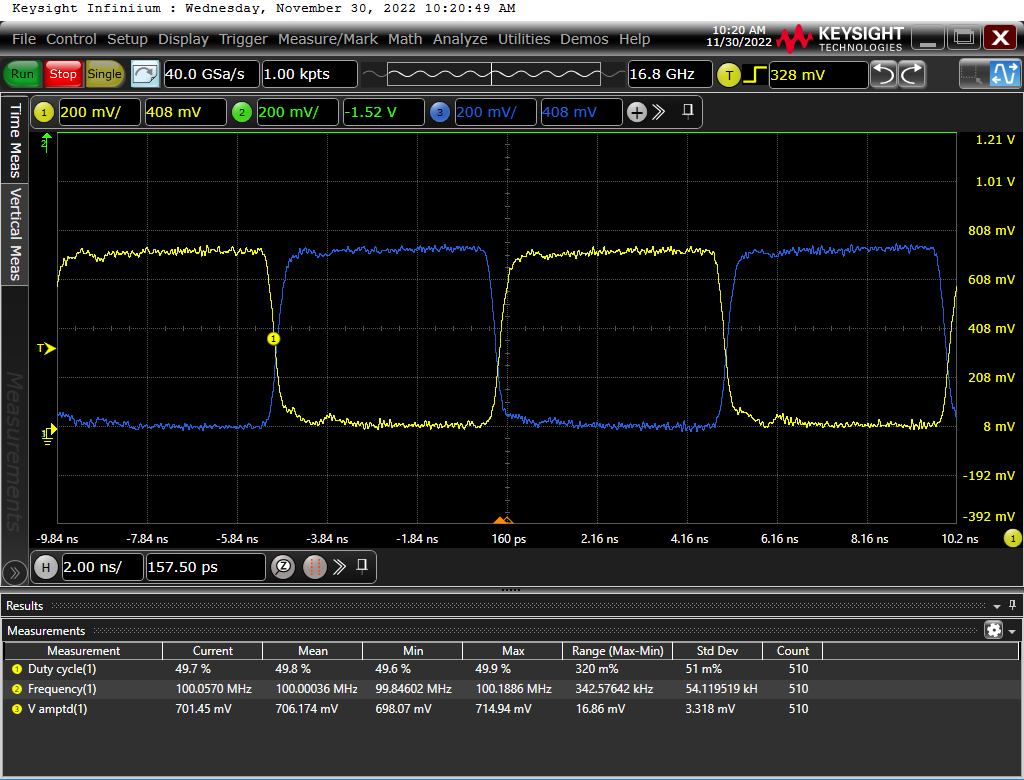

CLG52147差分輸出波形

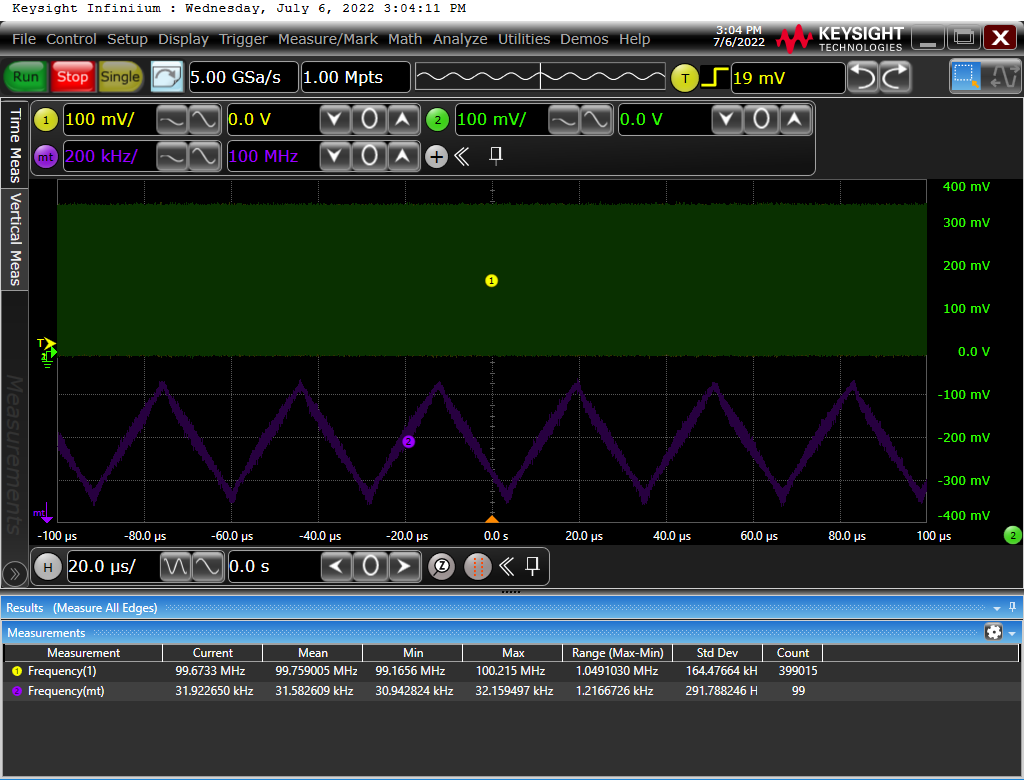

CLG52147 SSC展頻

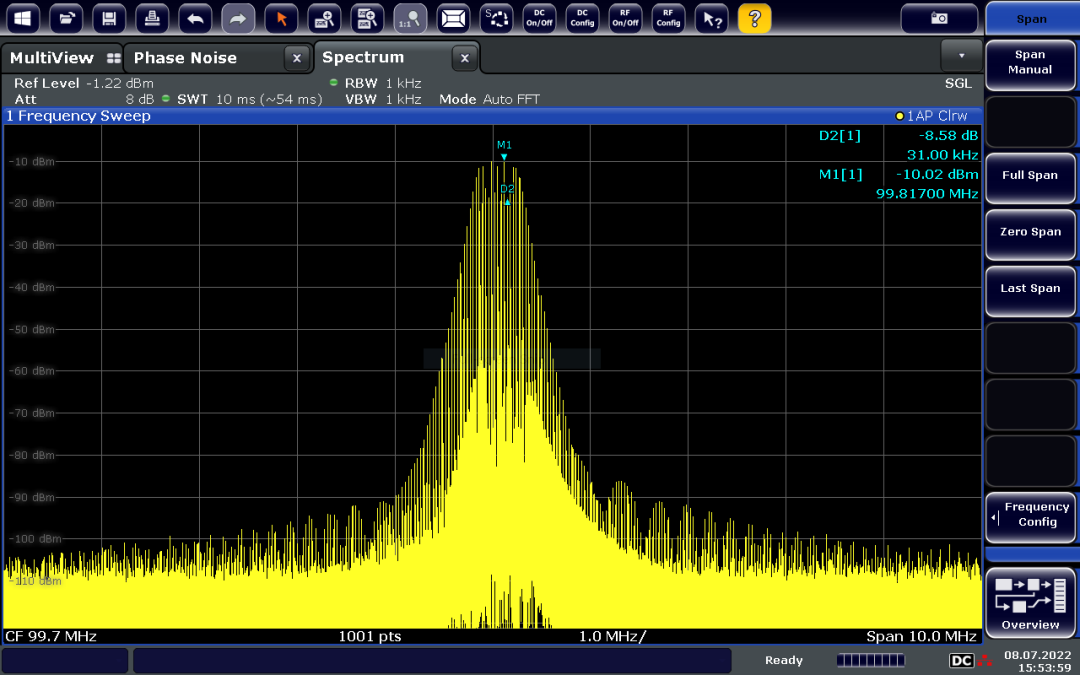

CLG52147 SSC展頻頻譜

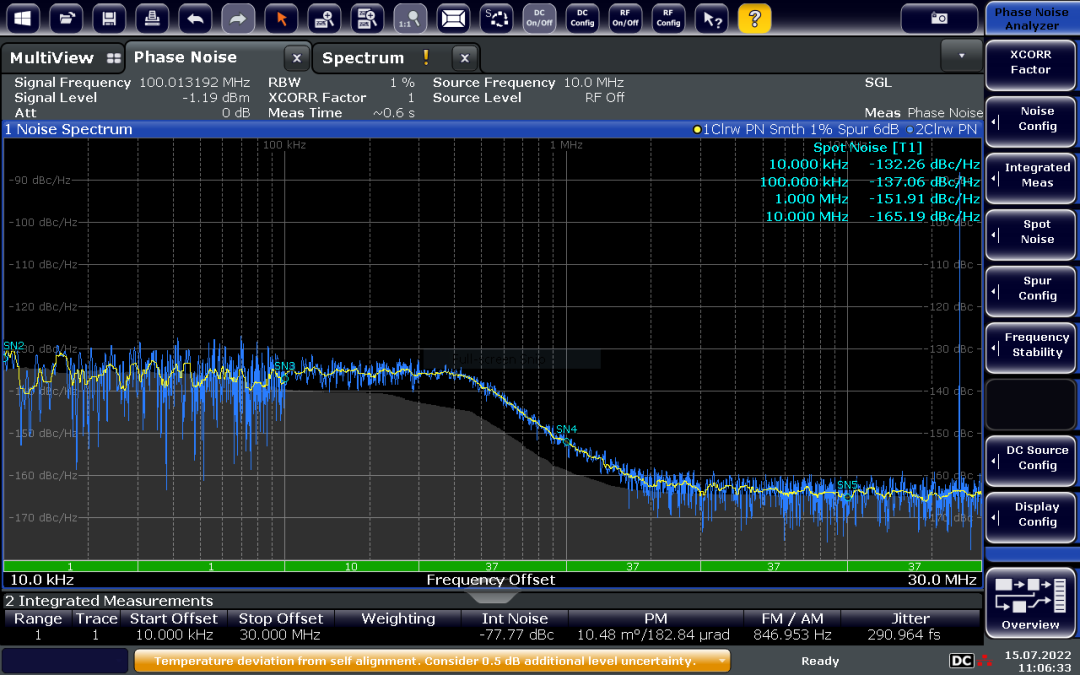

CLG52147典型相噪測試

CLB53156

CLB53156是一顆6路LP-HCSL輸出的,滿足PCIe 5.0規范的低抖動時鐘Buffer芯片,該芯片同時也提供PCIe Gen 1/2/3/4的前向兼容性。CLB53156在PCIe Gen 5.0時附加抖動僅為6 fs,優秀的性能可以為設計人員提供更多的冗余而使整機獲得更高的性能。

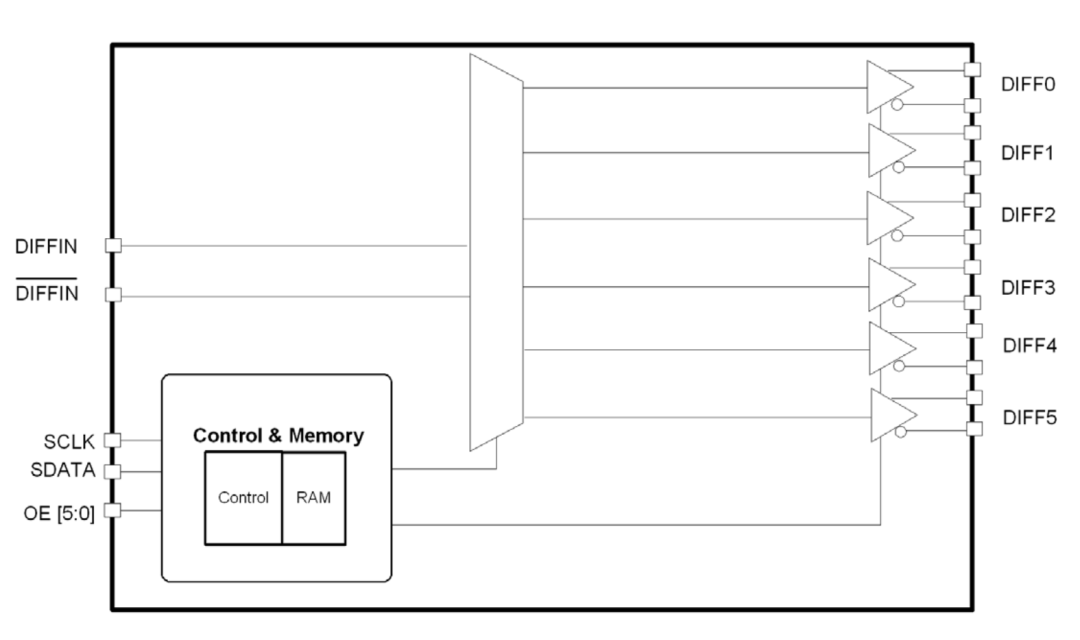

CLB53156功能框圖

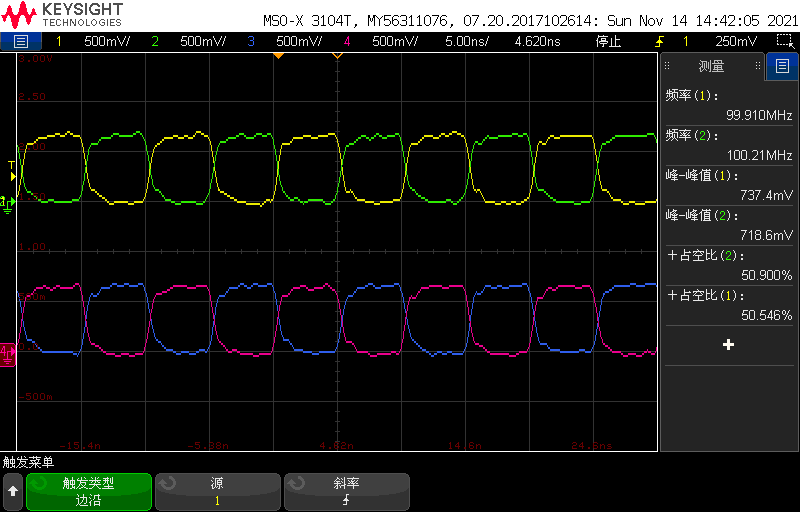

CLB53156差分輸出波形

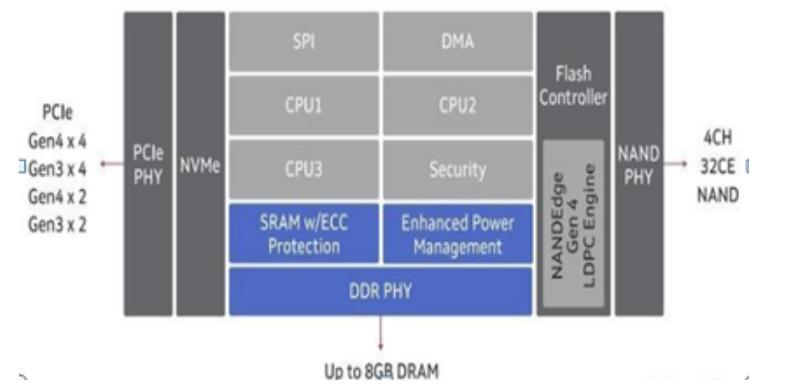

CLB53302/53305

CLB53302是一顆支持1/2/4分頻的時鐘通用時鐘Buffer,可以支持20路任意形式單端輸出或者10路任意形式差分輸出,同時輸入輸出可以支持1.8V/2.5V/3.3V任意電壓轉換,可以用在包括PCIe 1/2/3/4/5、基站、存儲、服務器、汽車等在內的任意場合,該芯片具有以下特性:

支持PCIeGen1/2/3/4/5

支持1–750MHz工作頻率

支持任意輸入輸出格式:LVPECL, High Swing

CML,LVDS,CML,HCSL,LVCMOS

內置LDO以提高電源抑制比

支持20路單端或者10路差分輸出

輸出支持1/2/4分頻

輸入輸出支持任意電壓轉換:1.8V/2.5V/3.3V

CLB53302功能框圖

CLB53302 HCSL輸出波形

審核編輯:劉清

-

emi

+關注

關注

53文章

3602瀏覽量

128193 -

PCB設計

+關注

關注

394文章

4698瀏覽量

86340 -

時鐘發生器

+關注

關注

1文章

202瀏覽量

67403 -

PCIE總線

+關注

關注

0文章

58瀏覽量

13455

原文標題:核芯互聯推出滿足PCIe 5.0規范的完整時鐘方案

文章出處:【微信號:gh_0dbe96735e9d,微信公眾號:核芯互聯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

求一種PCI Express(PCIe)5.0規范的完整時鐘解決方案

求一種PCI Express(PCIe)5.0規范的完整時鐘解決方案

評論