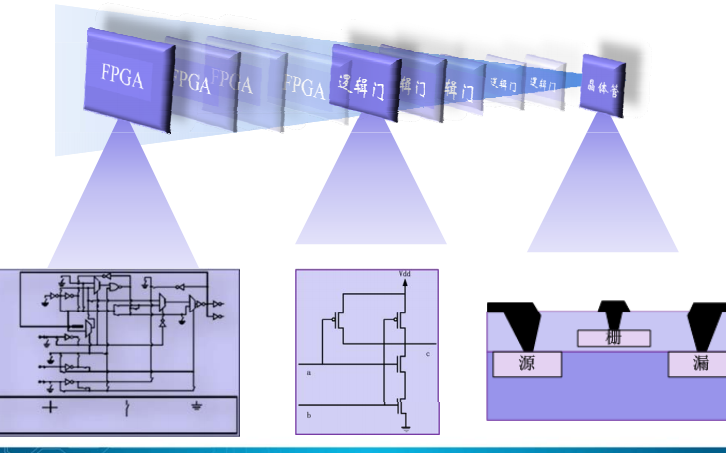

FPGA的本質是設計一顆芯片,其開發劉成是通過verilog等硬件描述語言通過EDA工具編譯、綜合、布局布線成為下載文件,最終加載到FPGA器件中去,完成所實現的功能。而硬件描述語言描述的就是組合邏輯和時序邏輯電路,度和邏輯就是與、非、或組成的電路,而時序電路就是觸發器。在FPGA中,組合邏輯的變成了查找表的工作,于是所有的數字電路轉化成為查找表和寄存器,這便是FPGA的基礎,查找表負責邏輯實現,寄存器存儲電路狀態。現代FPGA內部除了查找表和寄存器之外,還有RAM塊,用于存儲大量的數據塊,這樣可以節省芯片實現的面積。FPGA內部的時序電路需要時鐘的輸入,通常FPGA內部需要的時鐘種類較多,因此需要在片內產生相關的時鐘,因此時鐘管理單元DCM/PLL也是必不可少的內部部件。除此之外,FPGA內部還包括接口I/O,可分為普通I/O和高速I/O,次外還有各種各樣的硬核。

FPGA的英文翻譯過來是現場可編程門陣列,這是相對于ASIC來說的,ASIC硬件也可以可做是門陣列,但是它是非可編程的器件,流片完成之后功能就固化了。但是FPGA 的可編程性在于其能夠重新下載配置文件,來改變其內在的功能。兩者在前端開發流程上并無二致。FPGA作為一種器件,技術主要壟斷在ALTERA和XILINX這兩大公司手中。

(一)FPGA架構

一個完整的嵌入式系統中由單獨一個FPGA組成的情況較少,通常由多個器件組合完成,例如CPU+FPGA。通常是由一個FPGA+ARM,ARM負責軟件配置管理,界面輸入外設操作,FPGA負責大數據量運算,可看做CPU的專用協處理器來使用,也常會用于擴展外部接口。常用的架構有ARM+FPGA,DSP+FPG A,或者網絡處理器+FPGA等,這些架構形成構成整個高速嵌入式設備的處理形態。實現高速處理方面,CPU的發展趨勢是多核。FPGA的熱門應用有:

1)網絡存儲產片

2)高速網絡設備

3)4G通信等設備:對于新一代通信基站的信號處理,FPGA+DSP陣列的架構就是絕配。

總之,沒有完美的架構,只有合適的組合。

(二)器件互聯

系統架構確定之后,下一步就是FPGA和各器件的互聯問題。通常來說,CPU和FPGA的互聯問題主要取決于兩個要素:

1)CPU所支持的接口

2)交互的業務

通常FPGA一般支持與CPU連接的數字接口,其常用的有EMIF,PCI,網口,DDR等接口。作為總線類接口,FPGA通常作為從設備與CPU連接,CPU作為主設備通過訪問直接映射的地址對FPGA進行訪問。通常總線訪問分為同步訪問和異步訪問。CPU手冊中會對信號定義時序控制有著詳細的說明,FPGA根據這些詳細的說明來說實現相應的邏輯。同時CPU還會對訪問時序進行設置,例如設置建立時間、保持時間、最快時鐘。對于總線型的訪問來說,數據信號通常為三態,用于輸入輸出,這種設計目的減少外部連線的總數。總線訪問優勢是直接映射到系統的地址區間,訪問較為直觀,但相對傳輸速率不高,主要原因如下:

1)受制總線訪問間隔,即兩次訪問中間的空閑狀態

2)不支持雙向傳輸,并且FPGA主動對CPU發起操作是,只有中斷處理一種方式。

這種總線型操作特點可以使其用作系統的管理操作,例如FPGA內部寄存器的配置,運行過程中所需參數配置,以及數據量較小的信息交互等操作。這些操作數據量和所需帶寬合適,可應對普通的嵌入式系統的需求處理。而對于大數據流量的數據交互,一般采用專用的總線交互,其特點支持雙向傳輸,總線傳輸速率較快。

(三)FPGA特點

FPGA最大的特點在于其靈活性:

1)I/O的靈活性,可以通過其I/O組成各種接口與各種器件連接,并且支持不同的電器特性。

2)內部存儲器靈活,可以通過IP生成工具生成各種深度和寬度的RAM和FIFO

3)邏輯的靈活性,內部邏輯可生成各種類型IP

(四)架構設計

1)流驅動式

對于一個FPGA的架構設計,其首先需要考慮的就是性能,其次就是接口設計。一般架構設計是采用數據流驅動方式實現的,通常來說應用于IP領域、存儲領域、數字處理領域等較大型FPGA設計都是數據流驅動式架構,主要包括輸入接口單元,主處理單元,輸出接口單元,還可能包括輔助處理單元、外部存儲單元,這些單元之間一般采用流水式處理,即數據處理完之后數據打包發下一級處理。其中數據輸入輸出可能有多個,此時需要架構內部實現數據的交換。

2)穩定性:設計一定能夠進行正常工作

3)時鐘域復位:復位一般采用異步復位同步釋放的方式。

4)并行與復用:并行可以提過處理速度,復用可以節省資源。最終的設計取決于對設計處理能力和邏輯數量的權衡。

5)流水線處理:簡化設計;時序優化。但是流水設計對于帶反饋的設計無能為力,強加流水設計的話有可能會浪費邏輯和設計。

(五)FPGA中一些常用內部資源

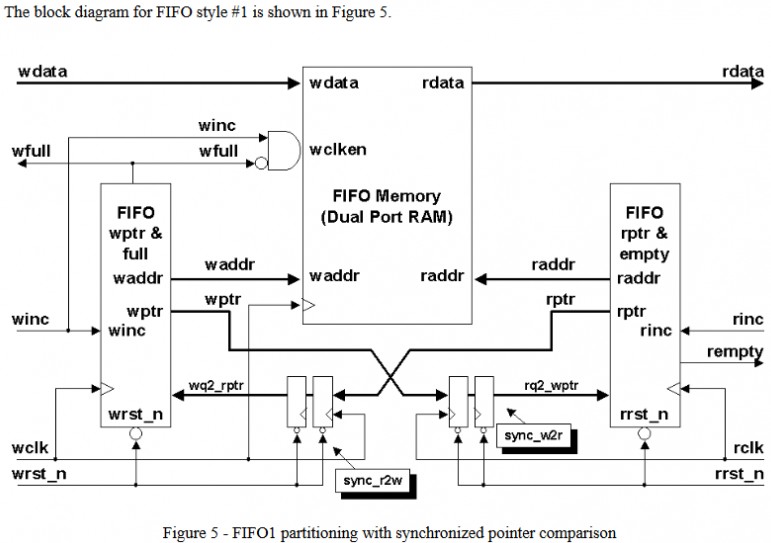

1)FIFO設計:作為FPGA中內部資源的一個常用器件,最常見與異步時鐘域劃分和緩沖數據,但不僅限于此。簡化設計、減少耦合、輸入輸出接口固定,便于仿真和驗證,都是使用FIFO的好處。

2)RAM:通常實例化RAM中,一種是BLOCK RAM,一種是分布式RAM,前者可以提供較大的存儲空間,后者提供較小的存儲空間。

(五)coding原則

1)注釋:好的代碼必須有注釋,注釋至少包括文件注釋、端口注釋和功能語句注釋。好的注釋,可以提高代碼的可讀性,可維護性。

2)語句:所寫語句一定是可綜合的,在FPGA設計中無外乎就是時序邏輯和組合邏輯。組合邏輯是即可生效的,時序邏輯是時鐘的下一拍起效。

3)阻塞與非阻塞賦值:一般情況下,組合邏輯用的是阻塞賦值,時序邏輯用的是非阻塞賦值。

4)注意避免鎖存器的生成:鎖存器最容易產生在always(*)模塊,所有的分支條件都要描述并且賦值,狀態機中的default狀態也不要忘記。

(六)接口設計

在進行設計的時候,需要一個接口模塊,首先需要明確以下問題:

1)同步接口還是異步接口?

2)有哪些信號,功能是什么?

3)信號之間的時序關系是什么?

4)傳遞的效率什么?

這些問題的答案一般都會在datasheet中給出,一般設計一個接口模塊,必然與其他硬件電路相連接。加入外部連接接口是總線接口,至少包括以下卻不限于以下信號:

1)地址:能夠支持的最大地址空間,數據和地址是否復用?

2)數據:一般讀數據和寫數據復用同一接口

3)讀寫命令

4)是否支持突發傳輸

5)同步還是異步

6)控制信號之間的相位關系以及建立時間和保持時間的要求

(6)學會總線設計

PC時代,壟斷江湖的是微軟和INTel,而在移動互聯網時代,最具有潛質的就是谷歌的ANDROID系統和ARM芯片。因此作為ARM處理做片上互聯的AMBA總線標準成為業界應用最廣泛的標準。

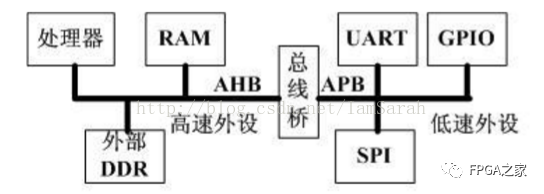

AMBA總線實際是三個標準的集合,分別為AHB,ASB,APB。ASB已經逐漸被AHB取代,現在使用最廣泛的是AHB和APB總線,以及最新擴展的AXI總線。如圖為AHB和APB在一個嵌入式系統中的應用場景。

??

審核編輯:湯梓紅

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606041 -

cpu

+關注

關注

68文章

10905瀏覽量

213030 -

接口

+關注

關注

33文章

8694瀏覽量

151928 -

時序電路

+關注

關注

1文章

114瀏覽量

21742 -

觸發器

+關注

關注

14文章

2003瀏覽量

61350

原文標題:FPGA相關知識系統介紹

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA入門知識介紹

CentOS系統的知識介紹

介紹UG編程的基本操作及相關加工工藝知識

手機電池相關知識介紹

FPGA基礎知識培訓教程免費下載

基于FPGA 以及數字電路設計相關高級技巧介紹

FPGA相關知識系統介紹

FPGA相關知識系統介紹

評論