在我工程生涯的早期,我認為并行通信通常比串行通信更可取。我很欣賞同時移動所有 8 個(或 16 個或 32 個...)數據位的簡單性和效率,使用一個或兩個控制信號進行握手,并且不需要精心設計的同步方案。

不過,不久之后,流行的數字通信協議( UART、SPI、I2C等)使用串行接口變得很明顯,而且我還注意到專門應用程序的高級協議支持串行傳輸。盡管微控制器和中央處理器單元 (CPU)需要并行數據來進行內部存儲、檢索和處理操作,但這意味著串行通信涉及額外的序列化和反序列化硬件。

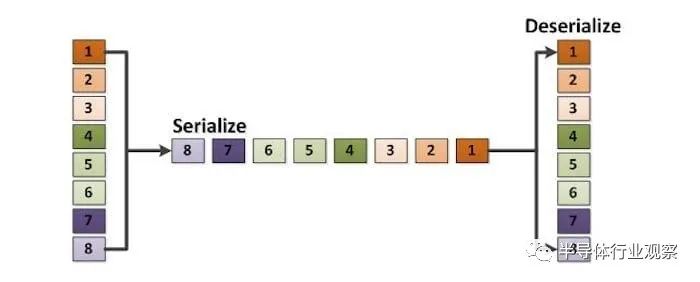

SerDes 是空間到時間到空間的轉換。并行數據同時傳輸但占用不同的物理互連,串行數據共享相同的物理空間但占用不同的時間時刻(圖 1)。

圖 1. 顯示序列化和反序列化的示例圖。

考慮到所有這些,讓我們看一下并行數據傳輸的局限性,然后我將討論一些重要的 SerDes 概念。

為什么串行通信優先于并行通信?

并行傳輸的一個更直接的缺點是涉及的導體數量。如果您仍在 8 位世界中工作,相對于簡單的同步數據傳輸的好處,使用大量互連似乎是合理的;然而,隨著總線寬度擴展到 16 位或 32 位范圍,PCB 布局任務變得越來越低效和難以管理。當您不僅要將數據從一個組件移動到另一個組件,還要將數據從一個 PCB 移動到另一個時,問題會變得更加嚴重。

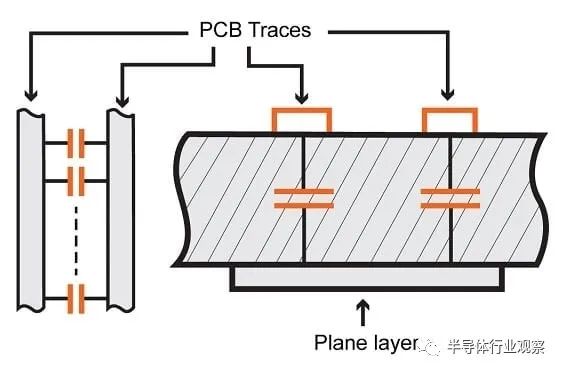

此外,這些并行數據線中的每一條都不僅僅是布局和布線人員所關心的問題。緊密間隔的電線或 PCB 跡線(如圖 2 所示)容易受到串擾的影響,尤其是數字信號的高能邏輯轉換特性,并且導體越多,越難以屏蔽環境電磁干擾 (EMI)。

圖 2. 走線在原理圖中是線時具有完美的電氣隔離,但在真實的 PCB 上,它們與附近的走線和平面層電容耦合。

對于串行,一些互連足以傳輸任何位寬的數據字,并且您可以降低偽邏輯轉換的可能性,這種邏輯轉換會通過破壞數據或需要重新傳輸來降低通信質量。

從理論上講,并行確實允許更快的數據傳輸,但即使是這種優勢也比最初看起來更偶然。更長的跡線或電線意味著信號將花費更多時間從發送器傳播到接收器,并且隨著數據速率的增加,通過匹配跡線長度來均衡整個總線的延遲變得更加重要。高速 32 位總線的跟蹤長度匹配并非微不足道——如果我進行布局,這將是支持序列化/反序列化的一個非常有力的論據。圖 3 顯示了一個曲折的示例,如果您需要均衡走線長度,它會很有幫助,但在您試圖最小化電路板面積時就沒有那么有用了。

高速并行總線的另一個問題是功耗過大。串行化可以通過將標準邏輯信號轉換為低壓差分信號來降低功耗。

SerDes 是什么?SerDes 功能和特性概述

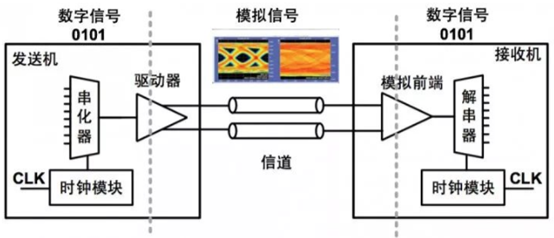

SerDes 是一個涉及兩個獨立電路塊的過程:在其基本形式中,串行器將由多個同步數字信號(例如,由微處理器或 ASIC 輸出)表示的數據轉換為沿一根導體傳輸的邏輯電平的時間序列. 解串器將這種邏輯電平的時間序列轉換回一組沿多條導體同時傳輸的信號。

除了這個基本功能之外,SerDes 實現還有各種細節和附加功能。

多個串行導體

并串轉換不一定將多根導線壓縮成只有一根導線。更一般地說,序列化的目標是顯著減少導體的數量。

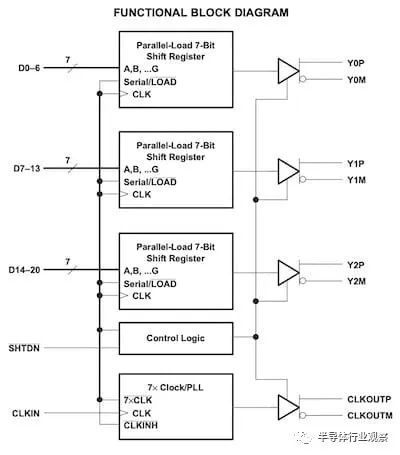

首先,單條串行通信線路通常需要兩條物理導體,因為許多串行接口(例如RS-485和USB)使用差分信號。此外,吞吐量和接口復雜性之間的最佳平衡可能需要多個串行通道。例如,在下面圖 4 的框圖中,TI 的 SN65LVDS95?LVDS串行器的數據表中,21 位并行數據被轉換為三個獨立的串行輸出流。

圖 4. 數據表中 SN65LVDS95 串行器的功能框圖。

如果串行器以特定頻率接收并行字,則它必須提高輸出比特率以使輸出字率與輸入字率相匹配。由于串行傳輸比并行傳輸更適合高位頻率,因此串行化不需要降低吞吐量。如上圖所示,鎖相環 (PLL)可用于根據并行到串行轉換中實現的壓縮因子來倍增輸入時鐘。

與任何數字通信接口一樣,SerDes 需要一些同步機制來確保接收器知道如何采樣和解析傳入的邏輯電平。某些系統(包括上圖中描述的系統)會隨數據一起發送時鐘信號。

解串器也可以從傳入的串行比特流中獲得同步:PLL 可以鎖定比特流并產生采樣時鐘。但是,如果輸入信號的轉換密度不足,PLL 將會漂移。例如,傳感器信號可能在正電源軌處飽和,并被數字化和串行化為一長串邏輯高位。為防止與低轉換密度相關的問題,您可以將 SerDes 系統與標準(例如 8b/10b)或自制編碼方案相結合。

將并行數據作為串行數據傳輸可為您提供物理傳輸選項,否則這些選項將不可行。即使當您的所有信號都位于同一個 PCB 上并且一切都使用普通走線進行布線時,序列化也可以極大地促進電路板布局。如果您要在板與板、模塊與模塊或系統與系統之間移動數據,您可能更愿意使用同軸電纜或光纖鏈路。如果您有序列化數據,則可以從普通電線升級到同軸電纜或光纖。

SerDes 已成為數字電子產品不可或缺的一部分。使用并行傳輸無法類似地實現視頻接口、電信互連和各種其他應用所需的極高數據速率。

審核編輯:劉清

-

微控制器

+關注

關注

48文章

7649瀏覽量

152107 -

pcb

+關注

關注

4326文章

23160瀏覽量

399949 -

電磁干擾

+關注

關注

36文章

2330瀏覽量

105645 -

解串器

+關注

關注

1文章

107瀏覽量

13327 -

SerDes

+關注

關注

6文章

201瀏覽量

35043

原文標題:你真的懂Serdes嗎?

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

GMII、SGMII和SerDes的差異總結

SerDes的技術原理 SerDes的重要概念和技術概述

請問6678中的srio的serdes和以太網的serdes是共用還是各自有自己的serdes?

主serdes和奴隸serdes,如果我使用主人,奴隸能使用嗎

SerDes是怎么工作的

參考時鐘對SERDES性能的影響

SERDES的優勢 SERDES演變的看法

SerDes是怎么設計的?(一)

為什么我們需要SERDES?SERDES的優點有哪些?

SerDes是什么?SerDes功能和特性概述

SerDes是什么?SerDes功能和特性概述

評論