帶復位的SR觸發器

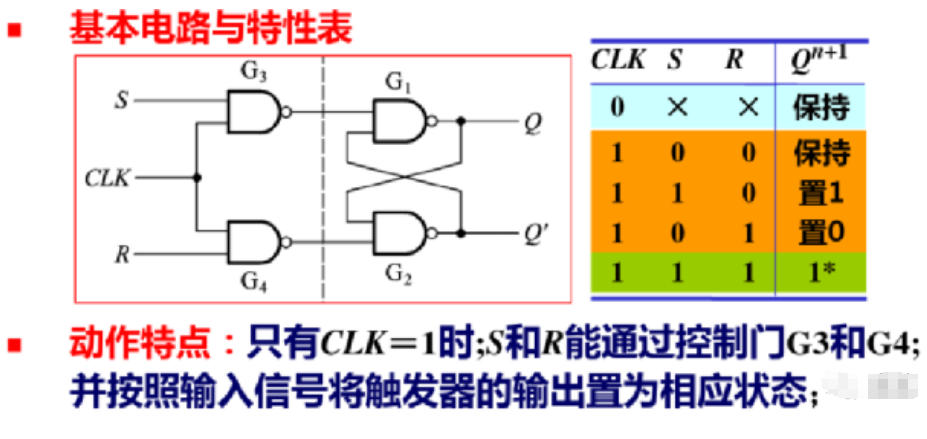

圖1是基本SR觸發器及其真值表。

圖1 基本SR觸發器及其真值表

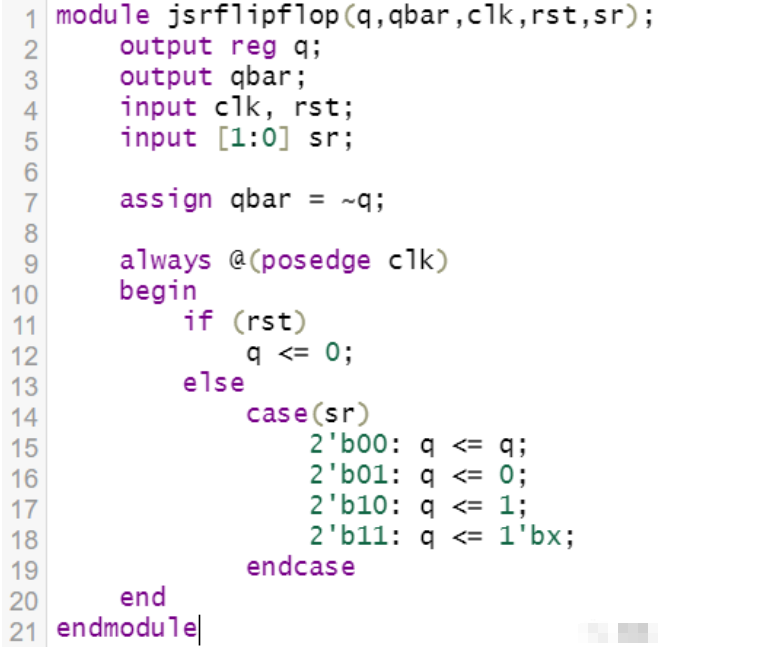

圖2 異步復位SR觸發器的verilog描述

圖2的SR觸發器在圖1的基本SR觸發器的基礎上添加了異步復位,所以多了一個rst信號,當rst為高電平,則SR觸發器復位到0。當rst為低電平時,那么此時該觸發器的功能和基本SR觸發器一致。

另外該module將SR觸發器中的S和R信號合并為一個2bit位寬的一個信號input [1:0] sr,在綜合工具編譯的時候應該會編譯成sr[0]和sr[1](高低位)。

帶復位的JK觸發器

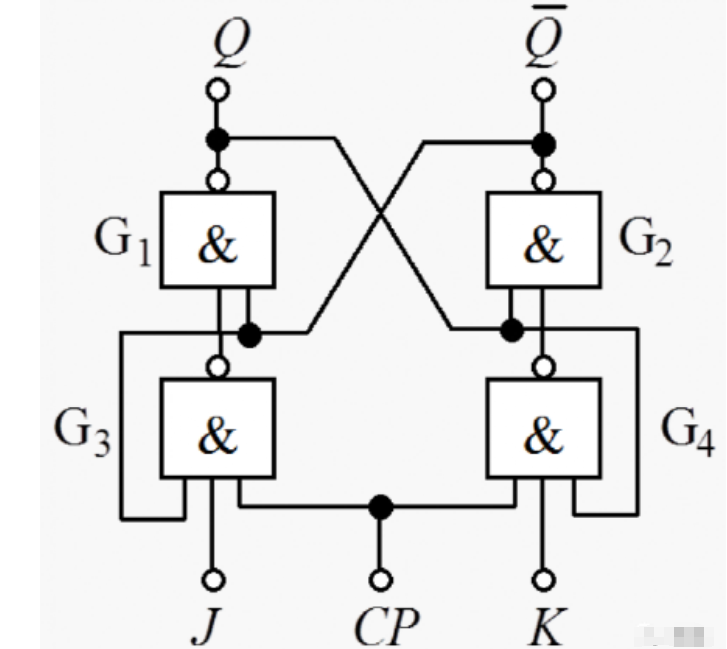

JK觸發器是數字電路觸發器中的一種基本電路單元。JK觸發器具有置0、置1、保持和翻轉功能。在各類集成觸發器中,JK觸發器的功能最為齊全。在實際應用中,它不僅有很強的通用性,而且能靈活地轉換其他類型的觸發器。由JK觸發器可以構成D觸發器和T觸發器。

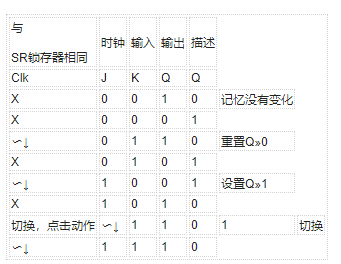

圖3 基本JK觸發器

圖4 基本JK觸發器真值表

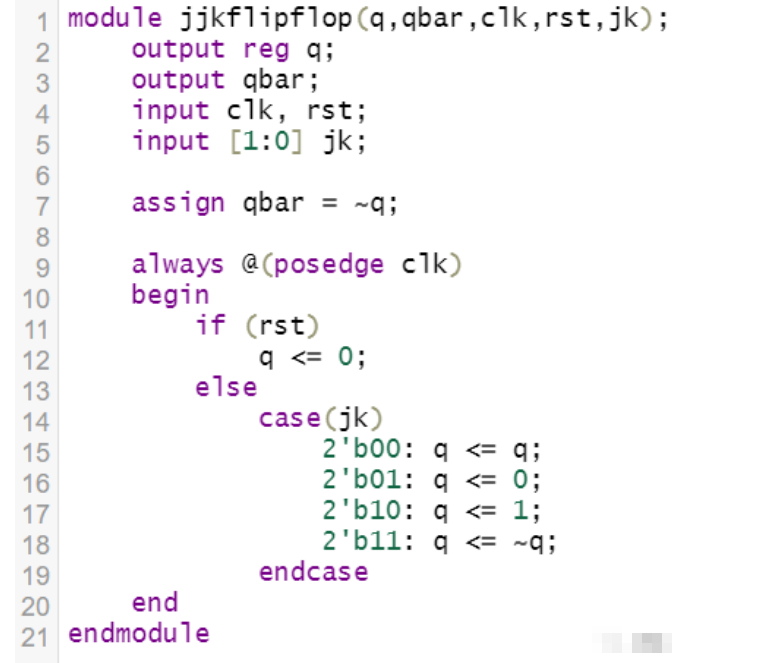

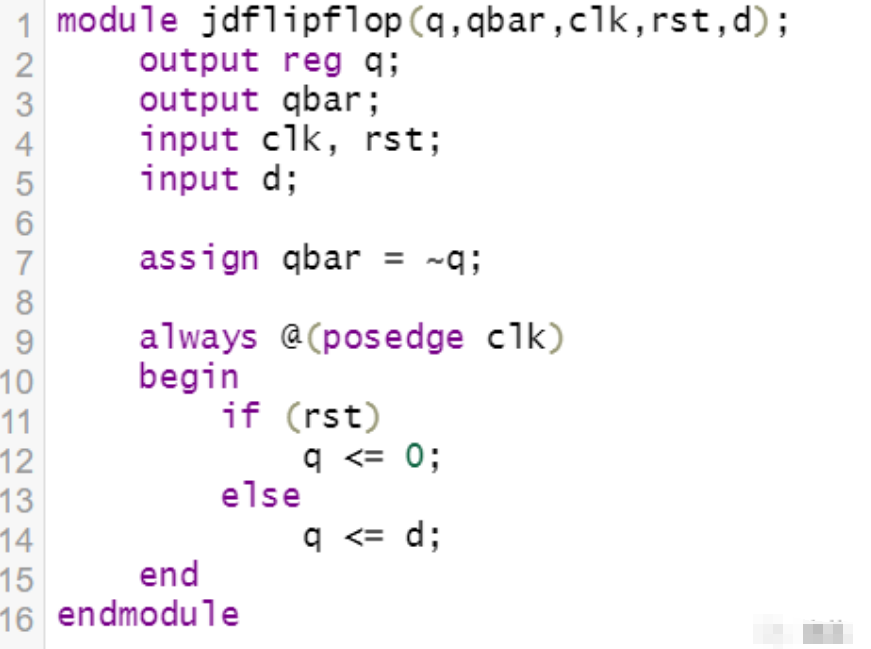

圖5 帶復位的JK觸發器的verilog描述

該JK觸發器module描述與上述的SR觸發器類似,唯一的區別在于真值表的不同。

D觸發器

D觸發器是常用的觸發器,時鐘高電平下,D端數據賦值給Q端。

圖6 D觸發器verilog描述

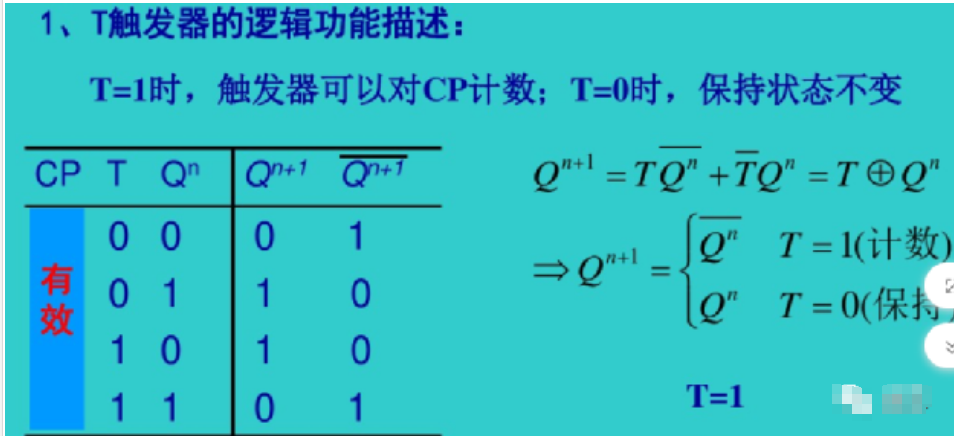

T觸發器

圖7是基本T觸發器。

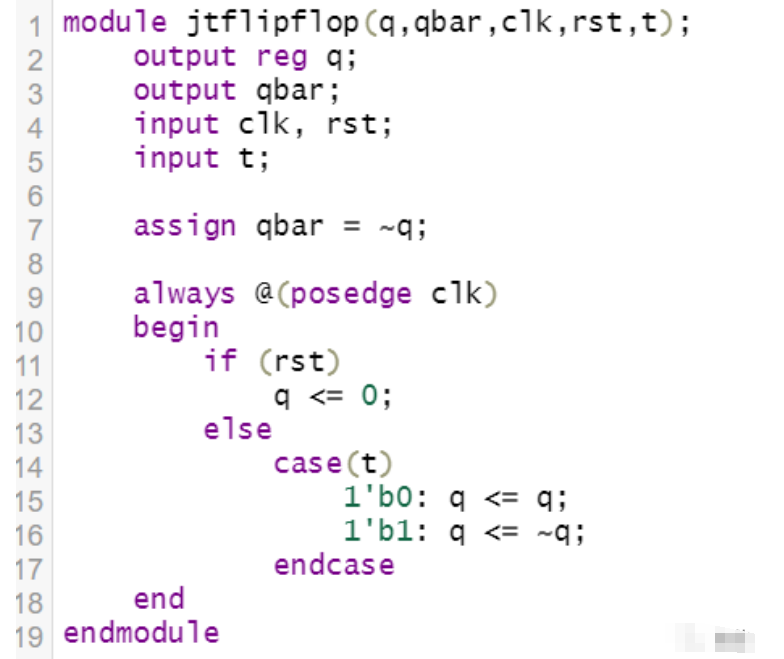

圖7 T觸發器

圖8 T觸發器的verilog描述

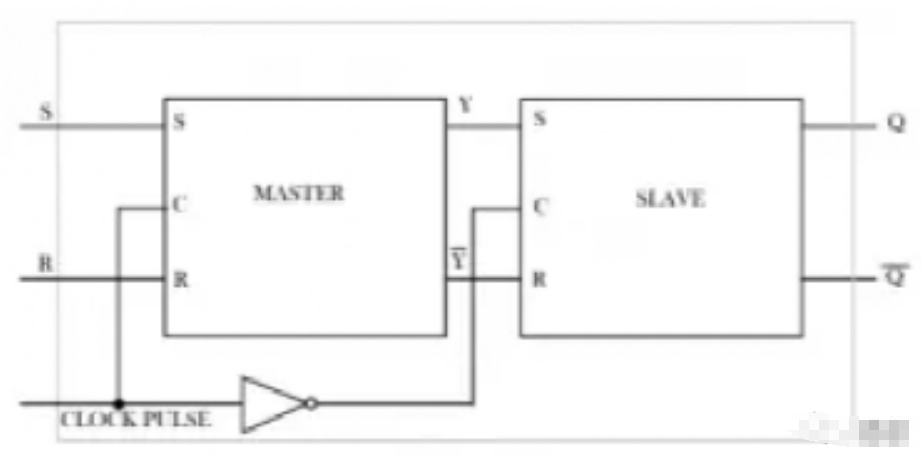

主從觸發器

主從是串聯連接的兩個觸發器的組合,其中一個充當主機,另一個充當從機。每個觸發器都連接一個互補的時鐘脈沖,即如果時鐘脈沖處于高電平狀態,則主觸發器處于使能狀態,從觸發器處于禁用狀態,如果時鐘脈沖為低電平,主觸發器處于禁用狀態,從觸發器處于啟用狀態。主從觸發器也稱為脈沖觸發器,因為在此操作模式下,觸發器可以通過 CLK 脈沖啟用或禁用。

圖9 主從觸發器

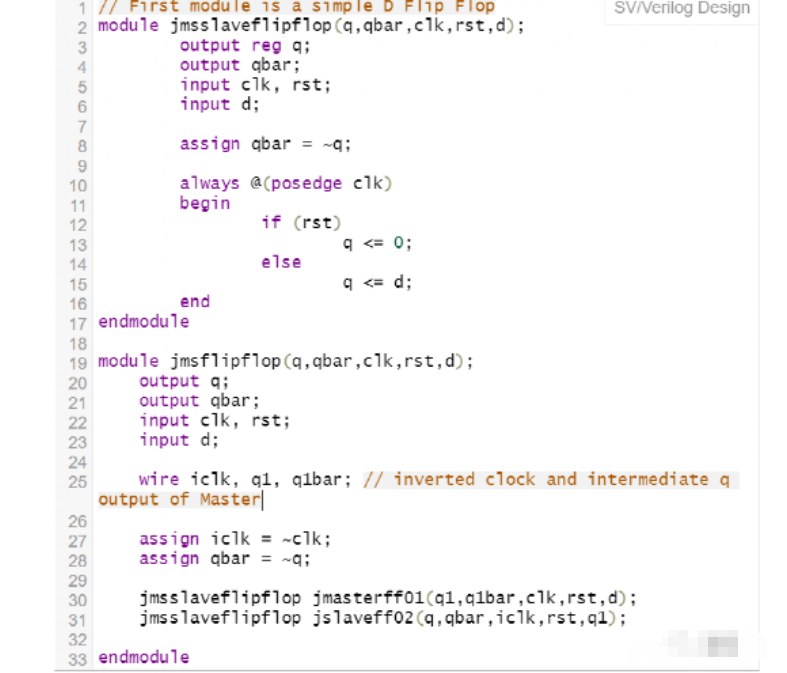

圖10 主從觸發器verilog描述

在主從觸發器中我們可以看到,verilog描述提前定義了一個基本D觸發器,并在描述中調用了兩次該module。主從觸發器中的主觸發器的輸入pin從module端口定義,從觸發器的輸入pin用wire變量定義。

-

Verilog

+關注

關注

28文章

1351瀏覽量

110391 -

JK觸發器

+關注

關注

1文章

43瀏覽量

15980 -

觸發器

+關注

關注

14文章

2003瀏覽量

61347 -

SR觸發器

+關注

關注

0文章

13瀏覽量

12669 -

異步復位

+關注

關注

0文章

47瀏覽量

13346

發布評論請先 登錄

相關推薦

jk觸發器是什么原理_jk觸發器特性表和狀態轉換圖

一文詳解帶復位的SR觸發器和JK觸發器

一文詳解帶復位的SR觸發器和JK觸發器

評論