聯(lián)華電子(NYSE:UMC;TWSE:2303)與楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日共同宣布,采用 Integrity 3D-IC 平臺的 Cadence 3D-IC 參考工作流程已通過聯(lián)電的芯片堆棧技術(shù)認(rèn)證,將進(jìn)一步縮短產(chǎn)品上市時間。

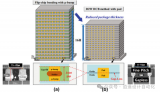

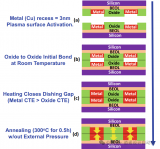

聯(lián)電的混合鍵合解決方案已經(jīng)做好支持廣泛技術(shù)節(jié)點(diǎn)集成的準(zhǔn)備,適用于邊緣 AI、圖像處理和無線通信應(yīng)用。采用聯(lián)電的 40nm 低功耗(40LP)工藝作為片上堆棧技術(shù)的展示,雙方合作驗(yàn)證了該設(shè)計(jì)流程中的關(guān)鍵 3D-IC 功能,包括使用 Cadence 的 Integrity 3D-IC 平臺實(shí)現(xiàn)系統(tǒng)規(guī)劃和智能橋突創(chuàng)建。Cadence Integrity 3D-IC 平臺是業(yè)界首款綜合解決方案,在單一平臺中集成了系統(tǒng)規(guī)劃、芯片和封裝實(shí)現(xiàn)以及系統(tǒng)分析。

聯(lián)華電子元件技術(shù)開發(fā)及設(shè)計(jì)支援副總經(jīng)理鄭子銘表示:“過去一年,我們的客戶在不犧牲設(shè)計(jì)面積或增加成本的情況下,尋求設(shè)計(jì)效能的提升方法,讓業(yè)界對 3D-IC 解決方案的興趣大為提升。成本效益和設(shè)計(jì)可靠度的提升是聯(lián)電混合鍵合技術(shù)的兩大主軸,同時也是此次與 Cadence 合作所創(chuàng)造的成果與優(yōu)勢,未來將可讓共同客戶享受 3D 設(shè)計(jì)架構(gòu)所帶來的優(yōu)勢,同時大幅減省設(shè)計(jì)整合所需時間。”

Cadence 數(shù)字與簽核事業(yè)部研發(fā)副總裁 Don Chan 表示:“隨著物聯(lián)網(wǎng)、人工智能和 5G 應(yīng)用設(shè)計(jì)復(fù)雜性的日益增加,片上技術(shù)自動化對芯片設(shè)計(jì)師越來越重要。Cadence 3D-IC 工作流程與 Integrity 3D-IC 平臺針對 UMC 的混合鍵合技術(shù)進(jìn)行了優(yōu)化,為客戶提供全面的設(shè)計(jì)、驗(yàn)證和實(shí)現(xiàn)解決方案,使他們能夠自信地創(chuàng)建并驗(yàn)證創(chuàng)新的 3D-IC 設(shè)計(jì),同時縮短產(chǎn)品推向市場的時間。”

該參考流程以 Cadence 的 Integrity 3D-IC 平臺為核心,圍繞高容量、多技術(shù)分層的數(shù)據(jù)庫構(gòu)建而成。該平臺在統(tǒng)一的管理平臺下提供 3D 設(shè)計(jì)完整的設(shè)計(jì)規(guī)劃、實(shí)現(xiàn)和分析。通過在設(shè)計(jì)初期執(zhí)行熱能、功耗和靜態(tài)時序分析,可以實(shí)現(xiàn) 3D 芯片堆棧中的多個晶粒的同步設(shè)計(jì)和分析。該流程還支持針對連接精度的系統(tǒng)級布局與原理圖(LVS)檢查,針對覆蓋和對齊的電氣規(guī)則檢查(ERC),以及在 3D 堆棧設(shè)計(jì)結(jié)構(gòu)中的熱分布分析。

除了 Integrity 3D-IC 平臺,Cadence 3D-IC 流程還包括 Innovus 設(shè)計(jì)實(shí)現(xiàn)系統(tǒng),Quantus 寄生提取解決方案,Tempus 時序簽核解決方案,Pegasus 驗(yàn)證系統(tǒng),Voltus IC 電源完整性解決方案和Celsius 熱求解器。

審核編輯:湯梓紅

-

IC

+關(guān)注

關(guān)注

36文章

5979瀏覽量

176219 -

3D

+關(guān)注

關(guān)注

9文章

2910瀏覽量

108005 -

封裝

+關(guān)注

關(guān)注

127文章

7993瀏覽量

143408 -

Cadence

+關(guān)注

關(guān)注

65文章

930瀏覽量

142454 -

聯(lián)華電子

+關(guān)注

關(guān)注

0文章

56瀏覽量

16744

原文標(biāo)題:聯(lián)華電子和 Cadence 共同合作開發(fā) 3D-IC 混合鍵合(hybrid-bonding)參考流程

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Cu-Cu Hybrid Bonding技術(shù)在先進(jìn)3D集成中的應(yīng)用

三維堆疊封裝新突破:混合鍵合技術(shù)揭秘!

先進(jìn)封裝技術(shù)激戰(zhàn)正酣:混合鍵合成新星,重塑芯片領(lǐng)域格局

混合鍵合的基本原理和優(yōu)勢

電子封裝 | Die Bonding 芯片鍵合的主要方法和工藝

Cadence與Samsung Foundry開展廣泛合作

混合鍵合技術(shù):開啟3D芯片封裝新篇章

Samsung 和Cadence在3D-IC熱管理方面展開突破性合作

Cadence與Intel Foundry的戰(zhàn)略合作取得重大成果

三星與海力士引領(lǐng)DRAM革新:新一代HBM采用混合鍵合技術(shù)

借助云計(jì)算加速3D-IC可靠性的機(jī)械應(yīng)力模擬

Cadence與臺積電深化合作創(chuàng)新,以推動系統(tǒng)和半導(dǎo)體設(shè)計(jì)轉(zhuǎn)型

3D-IC 以及傳熱模型的重要性

聯(lián)華電子和Cadence共同合作開發(fā)3D-IC混合鍵合(hybrid-bonding)參考流程

聯(lián)華電子和Cadence共同合作開發(fā)3D-IC混合鍵合(hybrid-bonding)參考流程

評論