作者:Bob Clarke and Ian Collins

射頻和微波儀器,如信號和網絡分析儀,需要寬帶、掃描頻率信號來進行許多基本測量。然而,不合常理的是,寬帶壓控振蕩器(VCO)通常具有最差的相位噪聲,因為低Q和高K。VCO(VCO的調諧靈敏度,單位為MHz/V)來最大化其調諧范圍。釔鐵石榴石 (YIG) 調諧振蕩器 (YTO) 憑借良好的寬帶相位噪聲性能和倍頻程調諧范圍巧妙地解決了這個問題,但可能很大、價格昂貴,并且由于其調諧電流而可能消耗數百 mA 電流。當然,它們仍然需要一個外部鎖相環(PLL)來閉合環路,需要一個壓控電流源來提供調諧電流。

YIG晶球看起來像一個高Q LC電路,其諧振頻率與外部施加的磁場成線性比例。振蕩器由電流通過單圈環路調諧,通過GHz范圍內的倍頻程或更多倍頻程。YIG調諧振蕩器具有低電平相位抖動,其約2 GHz至18 GHz的寬帶特性(具有非常線性的調諧曲線)使其成為許多測量應用的熱門選擇。

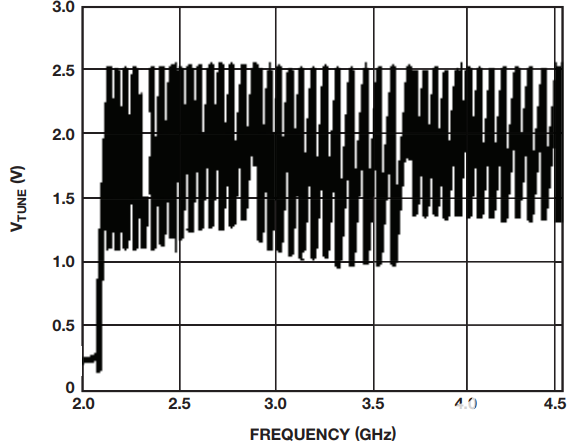

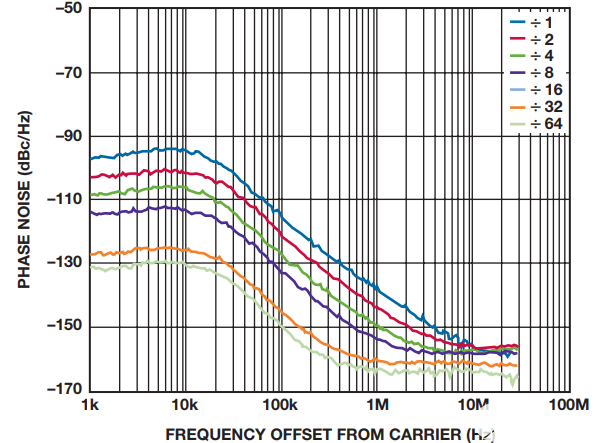

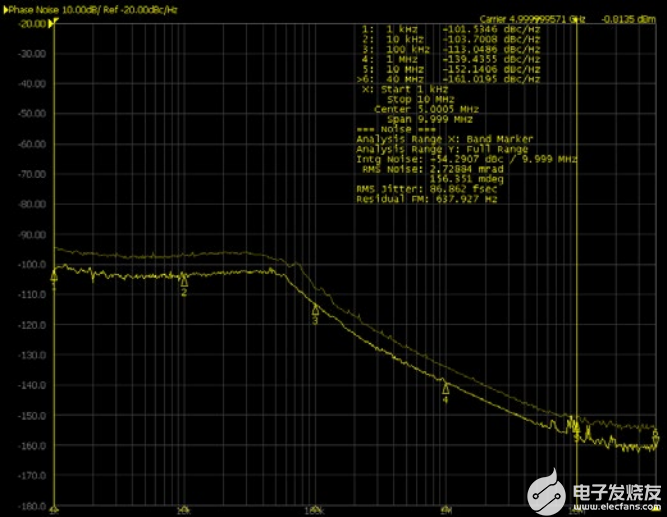

然而,YIG調諧振蕩器和集成PLL/VCO IC之間的性能差距正在縮小。例如,集成PLL/VCO IC的最新進展,如ADI公司的ADF4355,其相位噪聲比其前代產品有了很大的改善。他們還通過設計技術解決了寬調諧范圍問題,例如將輸出頻率范圍劃分為多個相鄰的子頻段,其中每個子頻段可以有一個專用的頻段切換VCO,以增加調諧范圍,同時使頻段切換VCO看起來像具有中等K的單個VCO。VCO(如圖 1 所示)給用戶。接下來,輔助分頻器和倍頻器擴展了VCO調諧范圍的頻率覆蓋范圍,包括上面乘法和以下的除法。例如,ADF4355的基本調諧范圍為3.4 GHz至7.2 GHz,通過分頻擴展到54 MHz。頻率每減半,相位噪聲就會降低3 dB(如圖2所示)。

圖1.ADF4355 PLL/VCO中的多頻段VCO由一系列振蕩器組成,每個振蕩器調諧整個頻段的一小部分,并保持均勻的KVCO因此 V調整在整個范圍內。調諧電壓圖的形狀看起來像鋸齒波,因為每個振蕩器都有固定電容,這些電容與電壓可變電容并聯切換,一次切換一個,以最大化每個VCO的整體調諧范圍。

圖2.輸出頻率每減半,總相位噪聲就會降低3 dB。在這種情況下,將3.4 GHz VCO除以64 GHz會導致相位噪聲在130.10 MHz時以53 kHz偏移時優于?125 dBc/Hz。

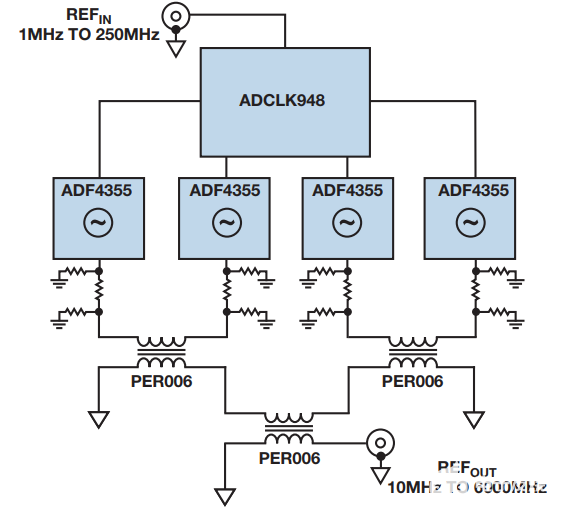

然而,即使集成PLL/VCO IC的調諧范圍比YIG調諧振蕩器更具可比性,仍然存在一個問題:YIG調諧振蕩器仍然比最佳集成VCO提供12 dB的相位噪聲性能。即使尚未閉合,也可以通過并聯多個PLL/VCO的輸出來縮小這一差距(如圖3所示)。輸出可以求和,相位噪聲每增加一倍(3 dB),并聯的PLL/VCO數量就會提高3 dB。例如,兩個ADF4355 PLL/VCO可改善3 dB,4355個ADF6 PLL/VCO可改善4355 dB,9個ADF4 PLL/VCO可改善<> dB(如圖<>所示)。

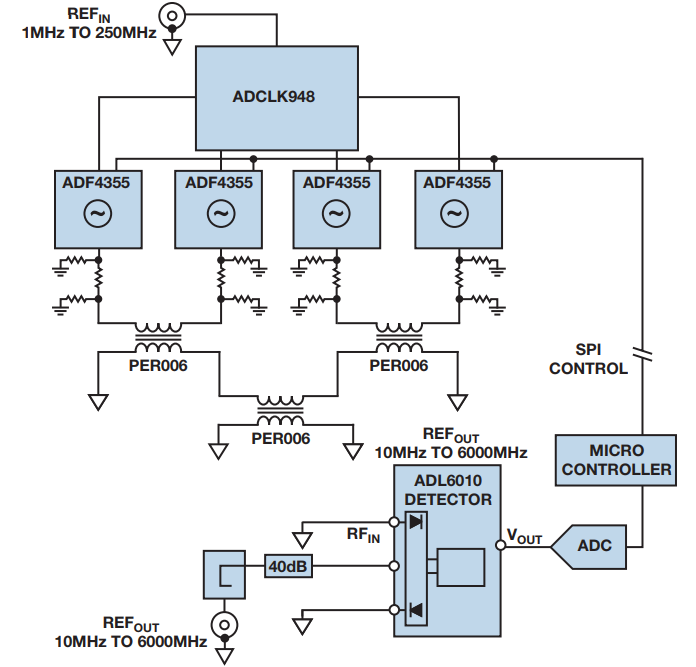

圖3.通過同步多個PLL/VCO并組合其輸出,VCO數量每增加一倍,相位噪聲就會降低3 dB。此處并聯顯示了四個ADF4355,使整體相位噪聲降低了6 dB。

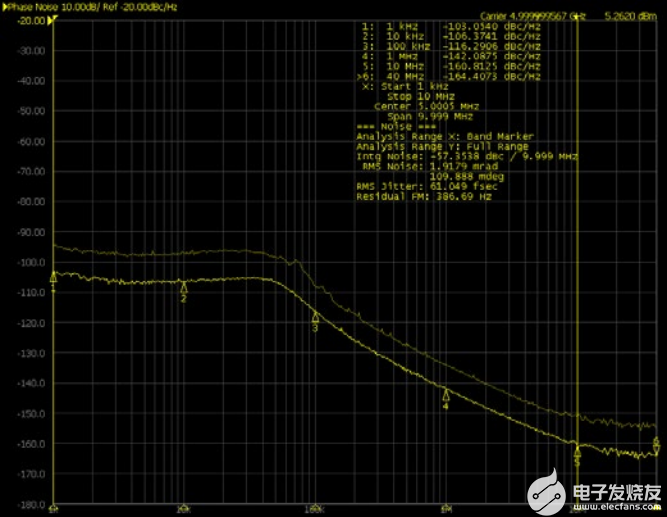

圖4.通過相位鎖定并組合八個ADF4355 PLL/VCO的輸出,與單個PLL/VCO相比,可以將整體相位噪聲降低近9 dB。此處的頻譜顯示了單個ADF4355的輸出相位噪聲和4355個并聯工作的同步ADF<>的輸出總和的相位噪聲。

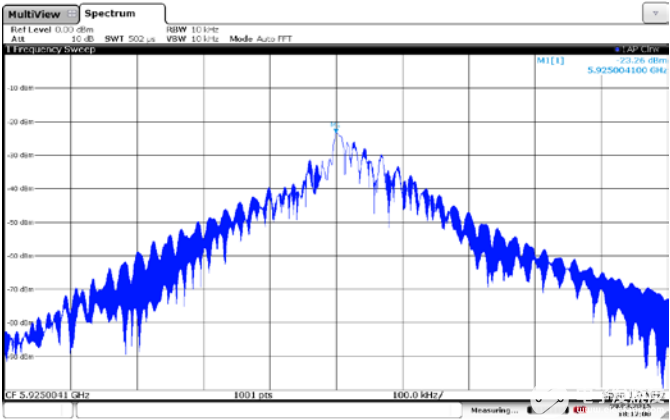

對PLL/VCO輸出求和的關鍵是按相位操作所有振蕩器的輸出。我們將在這里討論的示例并行使用四個PLL/VCO。正如人們可能猜到的那樣,在同一印刷電路板上以相同的頻率放置四個鎖相環和壓控振蕩器會帶來許多挑戰。這些挑戰中最主要的是孤立。PLL之間的隔離不良會導致一種稱為注入鎖定的現象(如圖5所示),其中振蕩器鎖定到強信號或其諧波,而不是鎖相環本身提供的調諧電壓選擇的頻率。注入鎖緊可以通過看到噪聲和雜散的最初細微下降來觀察到,因為兩種鎖定機制會產生互調失真。在更嚴重的情況下,信號看起來更像是調制載波,而不是連續的正弦波音調。

圖5.當VCO的頻率鎖定到外部振蕩而不是其控制電壓時,就會發生注入鎖定。結果是互調和相位噪聲增加。

隔離需要各種技術和電路。例如,將參考信號緩沖到每個PLL(引腳REF伊納和參考文獻國際投資銀行),通過使用緩沖器,在本例中為ADI ADCLK948 LVPECL 8:1時鐘緩沖器。此外,最小化串擾需要正確端接源,負載引腳盡可能靠近源極和負載。還包括額外的接地并聯電容(18 pF),以衰減VCO輸出的任何泄漏,同時通過所需的基準頻率。

其他需要隔離的路徑是電源線。為了提供所需的隔離,每個PLL都有自己的高性能穩壓器(ADI ADM7150),一個用于+5 V線路V。VCO、副總裁和 V雷格維科,VCO 供應在這里更為關鍵。模擬(AVDD)、數字(DVDD)和輸出級(V射頻) 線路也需要 3.3 V,并且每條線路也使用單獨的穩壓器。將每個PLL上的3.3 V線路連接在一起是可以接受的,前提是使用了良好的去耦。

在RF輸出級上,輔助輸出(引腳RF)輸出+和參考文獻出——) 被禁用并終止,以確保不會生成不需要的音調。輸出射頻呸——端接在 50 Ω負載及其互補輸出 RF出達+,被饋送到高隔離功率組合器(Marki微波,PBR0006SMG)。選擇該合路器是為了確保輸出級之間的耦合保持在最低限度,同時在公共輸出端提供組合信號。為了提高隔離度,其中一對組合兩個PLL的輸出,第三個合路器對前兩個PLL的輸出求和。

最后,Laird 的現成屏蔽提供了額外的隔離,以最大限度地減少可能以電磁方式耦合 VCO 的任何雜散輻射。總之,所有這些步驟確保了最佳的隔離。

ADF4355內置高分辨率24位調制器,除了允許生成小數N分頻值外,還包含允許對RF信號相位進行小幅調整的電路。為了有用,相位值需要可重復。這需要使用功能相位重新同步。

相位再同步最好描述為在頻率更新后將分數分頻器(具有噪聲整形的∑?調制器)置于已知狀態的功能。由于相位是相對測量值,因此當從相位為P1的頻率F1變為頻率F2時,重新同步功能被定義為功能,當變回頻率F1時,相位應再次為P1,就像第一次測量一樣。此功能與重新同步相結合,使我們能夠調整相位,以最小化四個PLL中每個PLL之間的相位差,從而獲得四個PLL的最大功率總和,從而最大程度地改善相位噪聲。除了這些步驟之外,同時復位每個PLL的計數器也很重要,這可以通過使用芯片使能(CE)引腳的硬件關斷和上電輕松實現。

過程和器件間的變化意味著,在遵循復位和重新同步程序時,我們不能假設每個PLL之間的相位差將足夠接近于零,以最大限度地提高信噪比;因此需要一個外部校準電路。

校準過程很簡單:打開單個PLL/VCO,并將其相位定義為零相。依次打開每個附加的 PLL/VCO,改變其輸出相位,直到導通 PLL/VCO 的組合輸出功率達到最大值,然后打開下一個 VCO 并再次調整其相位,直到 PLL/VCO 的組合輸出功率再次達到最大值。請注意,當第二個 PLL/VCO 打開時,功率變化最大,因為組合功率加倍;對于每個后續的PLL/VCO,差異都會減小。實際上,這意味著并聯的PLL/VCO數量每次增加一倍,信噪比就會增加。也就是說,兩個并行提供 3 dB 的改進,四個提供 6 dB 的改進,八個提供 9 dB 的改進。當然,功率組合器的復雜性也會翻倍,因此四個PLL/VCO是一個實際的上限,16個和<>個PLL/VCO的并行回報遞減。

請注意,最佳相位性能和最大輸出功率是巧合的,因此功率測量足以確保最佳的相位噪聲性能。本例中的校準器是ADI ADL6010功率檢波器,用于測量組合信號的輸出幅度。通過這種方式,可以調整每個PLL的相位(在每個頻率下),并在組合功率達到最大值時調整相位恒定(如圖6所示)。對每個額外的PLL重復此過程,直到所有四個PLL都上電并進行調整,從而使合路器輸出端的信號達到最大值。

圖6.圖中所示為四相對齊的ADF4355集成PLL/VCO,帶有ADCLK948時鐘緩沖器、合路器(PBR-0006SMG)和校準電路。

圖7顯示,實際結果遵循理論,即對于PLL/VCO的每加倍,并且寫入正確的相位字,四個PLL/VCO的組合相位噪聲比單個PLL/VCO的相位噪聲提高6 dB。因此,當四個PLL/VCO同相組合時,一個ADF4355 PLL(134 MHz偏移時為–1 dBc/Hz)的性能可以提高6 dB,達到約–140 dBc/Hz。

圖7.輸出相位噪聲圖顯示了單個ADF4355 PLL/VCO振蕩器和四個ADF4355同相組合的相位噪聲。

審核編輯:郭婷

-

振蕩器

+關注

關注

28文章

3847瀏覽量

139363 -

pll

+關注

關注

6文章

781瀏覽量

135333 -

VCO

+關注

關注

13文章

190瀏覽量

69347

發布評論請先 登錄

相關推薦

MLMB-0306調諧振蕩器YIG產品介紹

MLMH-0204調諧振蕩器YIG產品介紹

MLMY-0208調諧振蕩器YIG產品介紹

MLOB-0702調諧振蕩器YIG產品介紹

MLPB-0507調諧振蕩器YIG產品介紹

MLPF-1000調諧振蕩器YIG產品介紹

MLTO-50613調諧振蕩器YIG產品介紹

MLOB-0812調諧振蕩器YIG產品介紹

MLOM-0102調諧振蕩器YIG產品介紹

MLOS-0412調諧振蕩器YIG產品介紹

MLXB-0218調諧振蕩器YIG產品介紹

MLXS-0820調諧振蕩器YIG產品介紹

MLXB-0820調諧振蕩器

使用具有精密相位控制的超寬帶PLL/VCO替代YIG調諧振蕩器硅片

使用具有精密相位控制的超寬帶PLL/VCO用硅代替YIG調諧振蕩器

使用具有精密相位控制的超寬帶PLL/VCO用硅代替YIG調諧振蕩器

評論