1、IIC協(xié)議的誕生

IIC協(xié)議最早1982年由飛利浦公司設(shè)計(jì)開發(fā),是一種兩線制(SDA + SCL)的串行通行方式,提供了主從機(jī)之間通行的一種方案,在今天也是被廣泛的應(yīng)用在很多的產(chǎn)品設(shè)備上。

一個(gè)使用IIC協(xié)議進(jìn)行通信的設(shè)備,它既可以作為主機(jī)又可以作為從機(jī)(支持多主多從),并且它是一種半雙工的通信方式。

IIC可以支持的通信速率范圍較大,可以很好的滿足多種設(shè)備的不同的通信速度的要求,它支持的速率有如下幾個(gè):

1)普通模式(100kHz即100kbps)

2)快速模式(Fm)(400kHz)

3)快速模式+(Fs+)(1MHz)

4)高速模式(Hs)(3.4MHz)

5)超高速模式(UFm)(5MHz)

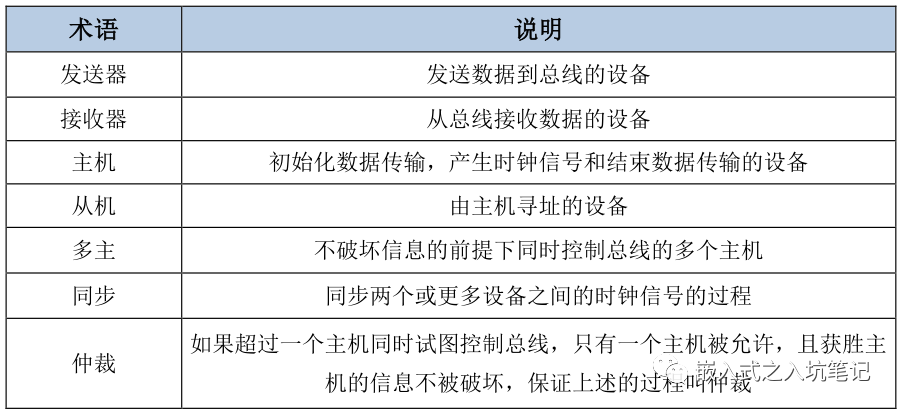

2、IIC總線的術(shù)語說明

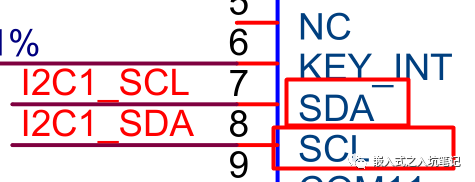

3、SDL 線和 SCL線

IIC設(shè)備有兩條接口線:串行數(shù)據(jù) SDA 線和串行時(shí)鐘 SCL 線。

連接到IIC總線上的設(shè)備通過這兩根線互相傳遞信息,SDA 和 SCL 都是雙向線,可以互相之間進(jìn)行信息的交互,但是是一種同步半雙工的通信方式,同一時(shí)刻只能有一個(gè)方向進(jìn)行數(shù)據(jù)的操作,不能同時(shí)進(jìn)行。

IIC設(shè)備上的兩根通信線一般示意如下:

4、IIC總線協(xié)議

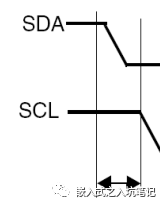

4.1、IIC總線的起始信號(hào)

IIC總線發(fā)送啟動(dòng)信號(hào)的時(shí)序如圖:

發(fā)送啟動(dòng)信號(hào)時(shí),時(shí)鐘線SCL需要穩(wěn)定的保持在高電位,SDA由高電位變化為低電位。啟動(dòng)信號(hào)發(fā)送完成之后就可以進(jìn)行數(shù)據(jù)的發(fā)送了。

如果在一次通信過程中,有兩臺(tái)以上的設(shè)備同時(shí)發(fā)出了起始信號(hào),都希望獲得總線控制權(quán)的話,那么第一個(gè)發(fā)出起始信號(hào)的設(shè)備將獲得總線控制權(quán),作為主設(shè)備開始傳輸數(shù)據(jù)。

注意:起始信號(hào)由主機(jī)負(fù)責(zé)產(chǎn)生。

4.2、停止信號(hào)

IIC總線發(fā)送停止信號(hào)的時(shí)序如圖:

停止信號(hào)是在時(shí)鐘線SCL為高電位的時(shí)候,數(shù)據(jù)線SDA由低電平變化為高電平。停止信號(hào)一般是在通信完成之后或者通信失敗退出之后發(fā)送的。

注意:停止信號(hào)由主機(jī)負(fù)責(zé)產(chǎn)生。

4.3、數(shù)據(jù)傳輸與有效性

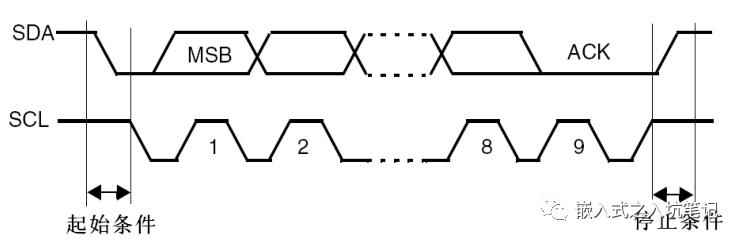

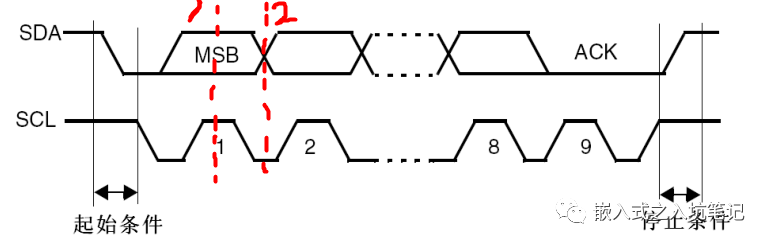

IIC數(shù)據(jù)傳輸?shù)膮f(xié)議如下:

數(shù)據(jù)的傳輸是在發(fā)送完成了啟動(dòng)信號(hào)之后便可以進(jìn)行數(shù)據(jù)的傳輸了。

IIC協(xié)議要求在時(shí)鐘信號(hào)SCL為高電位的期間,數(shù)據(jù)線SDA上的數(shù)據(jù)要保持穩(wěn)定,不能發(fā)生變化(上圖中1的位置)。只有在時(shí)鐘信號(hào)SCL電位變低的時(shí)候,數(shù)據(jù)線SDA上的電平狀態(tài)才能發(fā)生跳變。

每一個(gè)數(shù)據(jù)的bit位傳輸需要一個(gè)時(shí)鐘脈沖,一次傳輸最多是8bit。

一個(gè)完整的傳輸過程的通信時(shí)序如圖:

通信開始時(shí),最開始發(fā)送的都是地址幀。比如,一個(gè)7Bit的地址,首先發(fā)出的是最高位,即讀寫位(1-讀,0-寫),用于指示是讀操作還是寫操作。

幀的第9位是 **應(yīng)答位(ACK/NACK)** 。所有幀(數(shù)據(jù)或地址)都是一樣的。一旦發(fā)送幀的前8位,接收設(shè)備就可以控制數(shù)據(jù)線SDA。如果接收設(shè)備在第9個(gè)時(shí)鐘脈沖沒有將SDA線拉低進(jìn)行應(yīng)答,則可能是接收設(shè)備沒有接收到數(shù)據(jù),或者出現(xiàn)錯(cuò)誤。在這種情況下,主機(jī)需要決定該做什么樣的處理(一般考慮重發(fā)或者退出)。

注意:SCL時(shí)鐘信號(hào)由主機(jī)負(fù)責(zé)產(chǎn)生。數(shù)據(jù)的發(fā)送是高位先發(fā)的!

4.4、總線的仲裁

IIC總線支持多個(gè)主機(jī)同時(shí)在總線上發(fā)送數(shù)據(jù),但是同一時(shí)刻只能有一個(gè)主機(jī)傳送數(shù)據(jù)。因此必須要通過某些手段來決定哪個(gè)主機(jī)獲得總線的控制權(quán),其它的沒有獲得主機(jī)控制權(quán)的設(shè)備就只能進(jìn)行等待,直到獲得總線控制權(quán)才能進(jìn)行數(shù)據(jù)的傳輸。

IIC總線仲裁的方式有兩種:時(shí)鐘同步、仲裁。

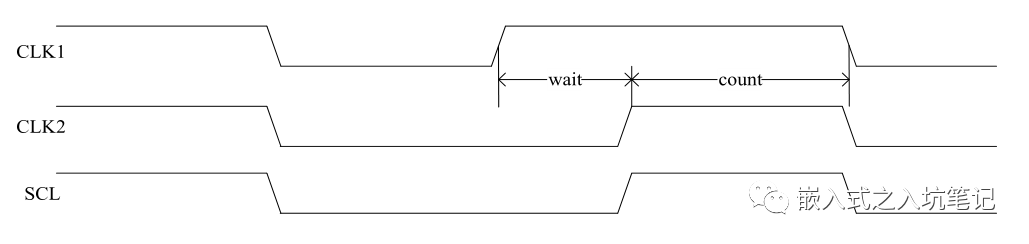

4.4.1、時(shí)鐘同步

時(shí)鐘同步是通過時(shí)鐘線SCL來實(shí)現(xiàn)的。在時(shí)鐘信號(hào)SCL由高到低的切換過程中,IIC器件會(huì)開始數(shù)自身的低電平周期。當(dāng)主器件的時(shí)鐘信號(hào)變?yōu)榈碗娖降臅r(shí)候,它會(huì)使SCL線保持這個(gè)電平狀態(tài)直到達(dá)到高電平。假如這個(gè)時(shí)候有另外一個(gè)器件的時(shí)鐘依然是處于低電平的周期,這個(gè)時(shí)鐘的低到高的變化不會(huì)改變SCL線的狀態(tài)。

因此,SCL線被有著最長(zhǎng)的低電平周期的器件占有總線的控制權(quán),而這個(gè)時(shí)候低電平周期短的器件會(huì)進(jìn)入高電平的等待狀態(tài),直到當(dāng)前的主器件釋放總線控制權(quán),自身能夠獲得總線控制權(quán)才會(huì)改變這些狀態(tài)。

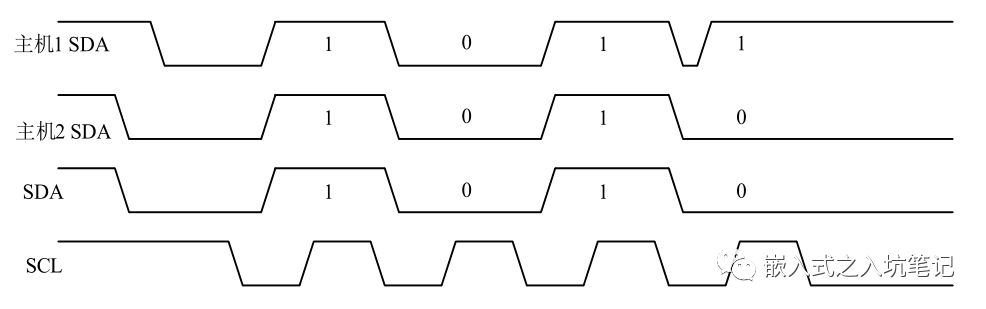

時(shí)鐘同步的時(shí)序示意圖如下:

4.4.2、仲裁

仲裁和同步一樣,都是為了解決多主機(jī)情況下的總線控制沖突。仲裁的過程與從機(jī)無關(guān)。

只有在總線空閑的時(shí)候主機(jī)才可以啟動(dòng)傳輸。兩個(gè)主機(jī)可能在比較短的時(shí)間內(nèi)在總線上同時(shí)產(chǎn)生一個(gè)有效的起始信號(hào),這種情況下需要仲裁來決定由哪個(gè)主機(jī)占有總線控制權(quán)來完成數(shù)據(jù)傳輸。

仲裁是逐位進(jìn)行,在每一位數(shù)據(jù)的仲裁期間,當(dāng)時(shí)鐘線SCL為高電平時(shí),每個(gè)主機(jī)都檢查數(shù)據(jù)總線SDA上的電平是否和自己要發(fā)送的相同。

這個(gè)過程需要持續(xù)很多位。理論上講,如果兩個(gè)主機(jī)所傳輸?shù)膬?nèi)容完全相同,那么他們能夠成功傳輸而不出現(xiàn)錯(cuò)誤。但是,如果一個(gè)主機(jī)發(fā)送高電平但檢測(cè)到SDA總線上的電平為低時(shí),則認(rèn)為自己仲裁失敗并關(guān)閉自己的SDA數(shù)據(jù)線上的數(shù)據(jù)傳輸,而另一個(gè)主機(jī)則繼續(xù)完成自己的傳輸。

IIC總線仲裁的時(shí)序示意圖如下:

5、IIC通信的流程

每個(gè)I2C設(shè)備都通過唯一的器件地址進(jìn)行識(shí)別,根據(jù)設(shè)備功能,他們既可以是發(fā)送器也可作為接收器。通信的流程如下:

1)IIC從機(jī)檢測(cè)到IIC總線上的起始信號(hào)之后,就開始從總線上接收地址,之后會(huì)把從總線接收到的地址和自身的器件地址(通過軟件編程)進(jìn)行比較,一旦兩個(gè)地址相同,IIC從機(jī)將發(fā)送一個(gè)確認(rèn)應(yīng)答(ACK),并響應(yīng)總線的后續(xù)命令;

2)發(fā)送或接收數(shù)據(jù);

3)發(fā)送或接收完成之后,在收到應(yīng)答信號(hào)ACK之后結(jié)束數(shù)據(jù)的傳輸。

此外,如果軟件開啟了廣播呼叫,則IIC從機(jī)始終對(duì)一個(gè)廣播地址 (0x00)發(fā)送確認(rèn)應(yīng)答。I2C模塊始終支持7位和10位的地址。

5.1、有關(guān)地址幀的發(fā)送

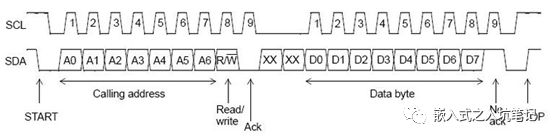

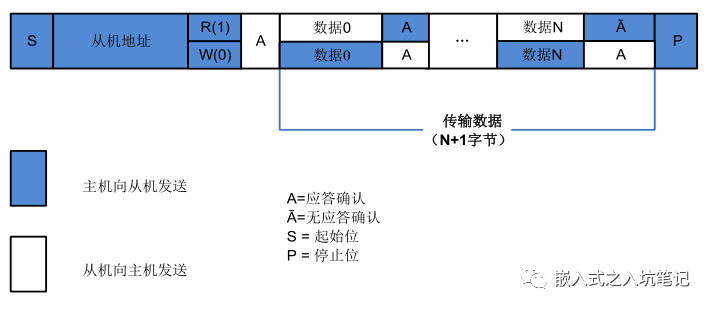

7 位地址的 IIC 通訊流程

7Bit地址的通信中,開始信號(hào)之后的第一幀是地址幀+讀寫位,剛好是8Bit的數(shù)據(jù),直接發(fā)送,等待從設(shè)備應(yīng)答之后便可以進(jìn)行數(shù)據(jù)的通信。

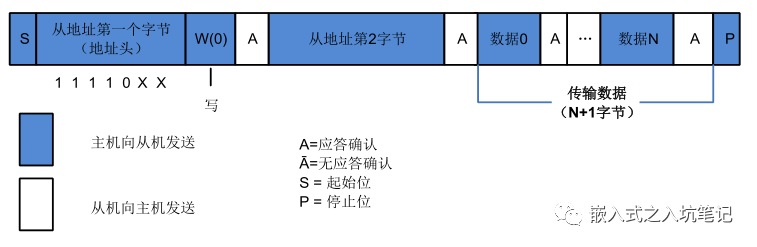

10 位地址的 IIC 通訊流程(主機(jī)發(fā)送)

對(duì)于10-bit地的址設(shè)備,需要使用兩個(gè)幀來傳輸10Bit的slave地址。

第一個(gè)幀的前5個(gè)bit固定為b11110xx,后接slave地址的高2位,第8位仍然是讀寫(R/W)位,接著是一個(gè)ACK位,由于總線上可能有多個(gè)10 Bit 從設(shè)備地址的高2bit相同,因此這個(gè)ACK可能由多有slave設(shè)備返回。

第二個(gè)幀緊接著第一幀發(fā)送,包含slave地址的低8位(7:0),接著該地址的slave回復(fù)一個(gè)ACK(或NACK)。

注意:10-bit地址的設(shè)備和7-bit地址的設(shè)備在總線中是可以并存的,因?yàn)?span id="ouf3lh1" class="hljs-number">7-bit地址的高5位不可能是b11110。

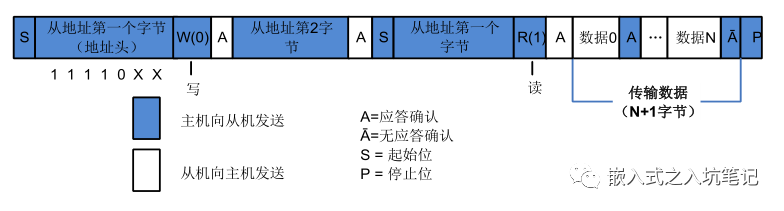

10 位地址的 I2C 通訊流程(主機(jī)接收)

-

SDA

+關(guān)注

關(guān)注

0文章

124瀏覽量

28266 -

SCL

+關(guān)注

關(guān)注

1文章

239瀏覽量

17177 -

IIC協(xié)議

+關(guān)注

關(guān)注

0文章

31瀏覽量

3968 -

串行通行

+關(guān)注

關(guān)注

0文章

2瀏覽量

1128

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA實(shí)現(xiàn)IIC協(xié)議的設(shè)計(jì)

IIC協(xié)議顯示屏

STM32的IIC協(xié)議

關(guān)于IIC協(xié)議

STM32的IIC協(xié)議簡(jiǎn)介

IIC協(xié)議的相關(guān)資料推薦

起始信號(hào)和停止信號(hào)在IIC協(xié)議中是如何規(guī)定的

IIC協(xié)議軟件模擬方法

IIC協(xié)議的相關(guān)資料下載

IIC協(xié)議是如何進(jìn)行通信的呢

如何使用代碼實(shí)現(xiàn)的IIC協(xié)議

IIC協(xié)議超詳細(xì)解釋(適合小白入門)

什么是IIC協(xié)議

什么是IIC協(xié)議

評(píng)論