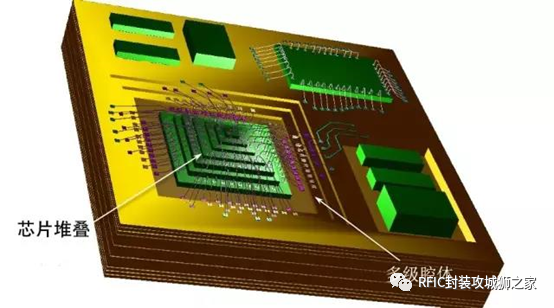

芯片堆疊技術(shù)在SiP中應(yīng)用的非常普遍,通過芯片堆疊可以有效降低SiP基板的面積,縮小封裝體積。目前來看,芯片堆疊的主要形式有四種:金字塔型堆疊,懸臂型堆疊,并排型堆疊,硅通孔TSV型堆疊。

為什么芯片可以進(jìn)行堆疊呢?這里面我們講的主要是未經(jīng)過封裝的裸芯片。曾經(jīng)有用戶問我,封裝好的芯片可不可以進(jìn)行堆疊呢?一般來說是不可以的,因?yàn)榉庋b好的芯片引腳在下表面直接焊接到基板上,而裸芯片的引腳一般在芯片上表面,通過鍵合的方式連接到基板。正是由于裸芯片引腳在上方,和基板的連接方式比較靈活,才有了芯片堆疊的可行性,參看下圖。

1金字塔型堆疊

金字塔型堆疊是指裸芯片按照至下向上從大到小的方式進(jìn)行堆疊,形狀像金字塔一樣,故名金字塔型堆疊,這種堆疊對(duì)層數(shù)沒有明確的限制,需要注意的是堆疊的高度會(huì)受封裝體的厚度限制,以及要考慮到堆疊中芯片的散熱問題。金字塔型堆疊參看下圖。

2懸臂型堆疊

懸臂型堆疊是指裸芯片大小相等,甚至上面的芯片更大的堆疊方式,通常需要在芯片之間插入介質(zhì),用于墊高上層芯片,便于下層的鍵合線出線。這種堆疊對(duì)層數(shù)也沒有明確的限制,同樣需要注意的是堆疊的高度會(huì)受封裝體的厚度限制,以及要考慮到堆疊中芯片的散熱問題。懸臂型堆疊參看下圖。

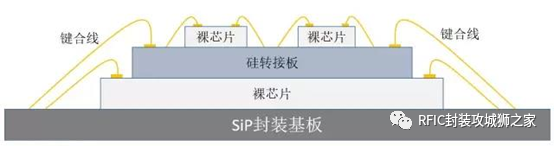

3并排型堆疊

并排堆疊是指在一顆大的裸芯片上方堆疊多個(gè)小的裸芯片,因?yàn)樯戏叫〉穆阈酒瑑?nèi)側(cè)無法直接鍵合到SiP封裝基板,所以通常在大的裸芯片上方插入一塊硅轉(zhuǎn)接板,小的裸芯片并排堆疊在硅轉(zhuǎn)接板上,通過鍵合線連接到硅轉(zhuǎn)接板,硅轉(zhuǎn)接板上會(huì)進(jìn)行布線,打孔,將信號(hào)連接到硅轉(zhuǎn)接板邊沿,然后再通過鍵合線連接到SiP封裝基板。并排型堆疊參看下圖。

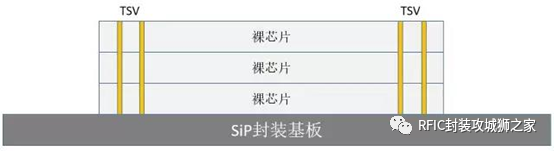

4 硅通孔TSV型堆疊

硅通孔TSV型堆疊一般是指將相同的芯片通過硅通孔TSV進(jìn)行電氣連接,這種技術(shù)對(duì)工藝要求較高,需要對(duì)芯片內(nèi)部的電路和結(jié)構(gòu)有充分的了解,因?yàn)楫吘挂谛酒洗蚩祝徊恍⌒木蜁?huì)損壞內(nèi)部電路。這種堆疊方式在存儲(chǔ)領(lǐng)域應(yīng)用比較廣泛,通過同類存儲(chǔ)芯片的堆疊提高存儲(chǔ)容量。目前也有將不同類芯片通過TSV連接,這類芯片需要專門設(shè)計(jì)才可以進(jìn)行堆疊。TSV型堆疊參看下圖。

上面介紹的是SiP設(shè)計(jì)中四種最基本的芯片堆疊方式。

在實(shí)際應(yīng)用的時(shí)候,這幾種堆疊方式可以組合起來形成更為復(fù)雜的堆疊。另外,還有通過將鍵合芯片和倒裝焊芯片進(jìn)行堆疊,通過柔性電路折疊的方式對(duì)芯片進(jìn)行堆疊,以及通過POP形式的堆疊等幾種,這些芯片堆疊方式在SiP設(shè)計(jì)中也比較常見。

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

456文章

51192瀏覽量

427317 -

SiP

+關(guān)注

關(guān)注

5文章

506瀏覽量

105464 -

封裝

+關(guān)注

關(guān)注

127文章

7997瀏覽量

143413

原文標(biāo)題:芯片堆疊技術(shù)在系統(tǒng)級(jí)封裝SiP中的應(yīng)用存?

文章出處:【微信號(hào):wc_ysj,微信公眾號(hào):旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

系統(tǒng)級(jí)封裝SiP在PCB的設(shè)計(jì)優(yōu)勢(shì)

一文看懂SiP封裝技術(shù)

系統(tǒng)級(jí)封裝(SiP)的發(fā)展前景(上)

SiP(系統(tǒng)級(jí)封裝)技術(shù)的應(yīng)用與發(fā)展趨勢(shì)

SiP的11個(gè)誤區(qū)盤點(diǎn)

系統(tǒng)級(jí)封裝(SiP)集成技術(shù)的發(fā)展與挑戰(zhàn)

SiP系統(tǒng)級(jí)封裝設(shè)計(jì)仿真技術(shù)

什么是系統(tǒng)級(jí)封裝(SiP)技術(shù)?

SiP系統(tǒng)級(jí)封裝、SOC芯片和合封芯片主要區(qū)別!合封和sip一樣嗎?

系統(tǒng)級(jí)封裝(SiP)技術(shù)介紹

一文讀懂系統(tǒng)級(jí)封裝(SiP)技術(shù):定義、應(yīng)用與前景

芯片堆疊技術(shù)在系統(tǒng)級(jí)封裝SiP中的應(yīng)用存?

芯片堆疊技術(shù)在系統(tǒng)級(jí)封裝SiP中的應(yīng)用存?

評(píng)論