摘要:

本文以 SOP008L 為例,通過對等離子清洗前后引線框架水滴角對比試驗,工藝實驗達到預期的效果,符合封裝工藝的實際情況。研究結論對提高封裝產品的可靠性提供了相應的參考依據。

0 引言

隨著 IC 制造技術的發展,傳統的封裝形式已經不能夠滿足現階段集成電路對于高性能、高集成度、高可靠性的要求。隨著電路框架結構尺寸的逐漸縮小,芯片集成與封裝工藝的不斷提高,對于高質量芯片的需求也在不斷提高,然而在整個封裝工藝過程中存在的污染物一直困擾著生產工程人員。

等離子是正離子和電子密度大致相同的電離氣體,等離子清洗機通過對氬氣進行電離,產生的等離子體通過電磁場加速,擊打在鍍銀層及芯片鋁墊表面,可以有效去除鍍銀層表面及鋁墊表面的有機物、環氧樹脂、氧化物、微顆粒物等沾污物,提高鍍銀層表面及鋁墊表面的活性,從而有利于壓焊鍵合。

1 等離子清洗介紹

采用 Ar 和 H 2 的混合氣體對引線框架表面進行等離子清洗,可以有效去除表面的雜質沾污、氧化層等,從而提高銀原子和銅原子活性,大幅提高焊線與引線框架的結合強度,提高產品良率,在實際生產中,等離子清洗已成為銅線工藝的必須工序。

1.1等離子清洗原理

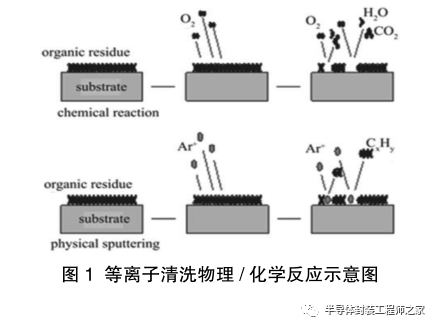

當等離子體與被清洗物體表面相互作用時,一方面利用等離子體或者是等離子激活的化學活性物質與材料表面污物進行化學反應,如用等離子體中的活性氧與材料表面的有機物進行氧化反應。等離子體與材料表面有機污物作用,把有機污物分解為二氧化碳、水等排出。另一方面利用等離子的高能粒子對污物轟擊等物理作用,如用活性氬等離子體清洗物件表面污物,轟擊使其形成揮發性污物被真空泵排出。

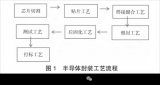

在實際生產中使用化學和物理方法同時進行清洗,其清洗速率通常比單獨使用物理清洗或化學清洗快。在引線框架封裝工藝中,采用氬氣與氫氣混合的物理化學清洗方法,但考慮到氫氣的易爆性,需嚴格控制混合氣體中氫氣的含量。其反應原理如圖 1所示。

1.2腔體式等離子清洗機

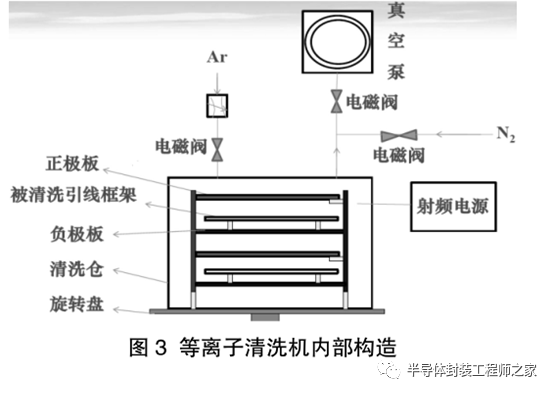

本文采用腔體式等離子清洗機進行工藝試驗。該設備為低溫低壓射頻等離子清洗設備,其原理是基于真空狀態下,利用射頻源激發形成的高壓交變電場將工藝氣體震蕩成等離子體,與有機污染物及微顆粒污染物反應或者碰撞,從而形成揮發性物質,最后由真空泵將揮發性物質排出去,從而達到表面清潔活化的目的。腔體式等離子清洗機的最大特點是可實現整體和局部以及復雜結構的清洗,同時該設備實現了引線框架的自動傳輸清洗,兩托盤相互交換接送料又提高了生產效率,單個引線框架清洗實現了對整體及局部位置的剝離式清洗,又無廢液,污染源產生。腔體式等離子清洗機結構及內部構造如圖 2、圖 3 所示。

(1)清洗機結構簡介

● 清洗倉:提供真空環境完成等離子體清洗。

● 射頻系統:提供高頻電壓,激發等離子體。

● 真空系統:用于抽真空,以提供 90 Pa 以下負壓工作條件。

● 物料傳輸系統:對產品提供物料旋轉傳輸。

● 控制系統:對整個系統進行控制,實現多種工作模式。

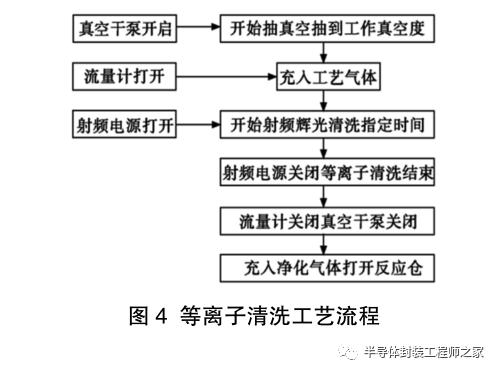

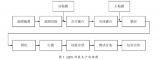

(2)等離子清洗工藝流程如圖 4 所示。

1.3等離子清洗的用途

(1)表面清洗:清洗金屬表面油脂、油污、以及肉眼看不到油脂顆粒等有機物及氧化層。

(2)表面刻蝕:通過處理氣體的作用,被刻蝕物會變成氣相排出。

(3)表面改性:以聚四氟乙烯(PTFE)為例,在其未做處理的情況下,不能印刷或粘合。使用等離子處理可以使表面最大化,同時在表面形成一個活性層,這樣 PTFE 就能進行粘合、印刷操作。

(4)表面活化:主要用于清理塑料、玻璃、陶瓷與聚乙烯(PE)、聚丙烯(PP)、聚四氟(PTFE)、聚甲醛(POM)等無極性材料的。

(5)表面涂鍍:在等離子涂鍍中,兩種氣體同時進入反應艙,氣體在等離子環境下會聚合。這種應用比活化和清洗要求嚴格得多。典型的應用是形成保護膜,用于燃料容器,防刮表層,類似聚四氟(PTFE)材質的涂鍍,防水鍍層等。

2 等離子清洗在封裝工藝中的應用

2.1 引線框架封裝工藝

在封裝行業的整個產業鏈中,封裝與測試芯片是走向市場的最后一個工藝環節,因此封裝與測試工藝的好壞直接決定了芯片質量可靠性及使用壽命,也對產品的市場占有率有很大的影響。從某種意義上講封裝是制造產業與市場需求之間的紐帶,只有封裝好才能成為終端產品。

2.2 等離子清洗在引線框架封裝中的應用

在電子封裝行業中,使用等離子清洗技術,目的是增強焊線 / 焊球的焊接質量及芯片與環氧樹脂塑封料之間的粘結強度。為了更好地達到等離子清洗的效果,需要了解設備的工作原理與構造,根據封裝工藝,設計可行的等離子清洗料盒及工藝。

封裝工藝直接影響引線框架芯片產品的成品率,而在整個封裝工藝環節中出現問題的最大來源就是芯片與引線框架上的顆粒污染物、氧化物及環氧樹脂等污染物。針對這些不同污染物出現環節的不同,在不同的工序前可增加不同的等離子清洗工藝,其應用一般分布在點膠前、引線鍵合前、塑封前等。

晶圓清洗:清除殘留光刻膠。

封裝點銀膠前:使工件表面粗糙度及親水性大大提高,有利于銀膠平鋪及芯片粘貼,同時可大大節省銀膠的使用量,降低成本。

壓焊前清洗: 清潔焊盤,改善焊接條件,提高焊線可靠性及良率。

塑封:提高塑封料與產品粘結的可靠性,減少分層風險。

BGA、PFC 基板清洗:在貼裝前對基板上的焊盤進行等離子體表面處理,可使焊盤表面達到清潔、粗化和活化的效果,極大地提高了貼裝的一次成功率。

引線框架清洗:經等離子體處理可達到引線框架表面超凈化和活化的效果,提高芯片的粘接質量。

2等離子清洗實驗

等離子清洗效果除與等離子清洗設備的參數設置有關外,也與樣品形狀及樣品的料盒有關。在料盒選擇方面,一般選用鏤空料盒,如圖 5 所示。

鏤空料盒可讓盡可能多的等離子氣體進入到料盒內部,并且不干擾等離子氣體的流動方向與流動速度。一般選用鋁合金材質,因為其具有良好的加工特性,同時質量輕,便于運輸。玻璃和陶瓷材質雖然在等離子清洗工藝中使用效果更佳,但在工廠批量生產中不利于運輸與操作。等離子清洗設備的反應室主要分為感應耦合“桶式”反應室、電容耦合“平行平板”反應室、“順流”反應室三種。目前,國內集成電路生產企業基本使用進口設備,采用第三種模式,其優點是具有均勻的等離子體區,射頻電源及匹配網絡不受負載影響,不損傷敏感器件。

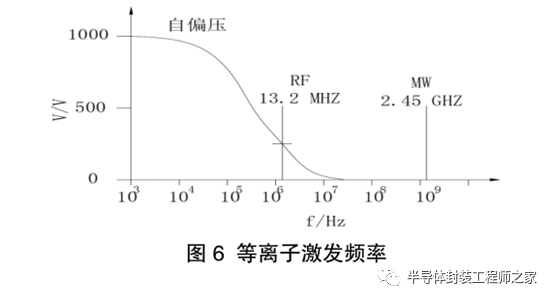

目前在微電子行業廣泛使用的是射頻等離子體,等離子按激發頻率分為射頻與微波,其頻率范圍的劃分如圖 6 所示。

3.1 實驗材料

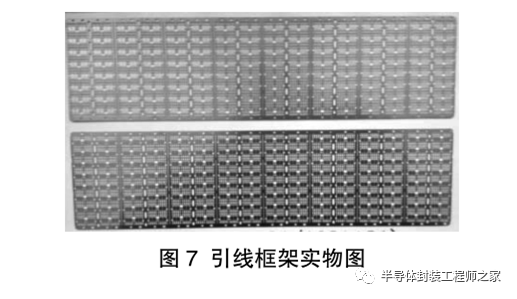

采用封裝領域廣泛使用的 SOP008L 引線框架為試驗材料,如圖 7 所示。

3.2 主要技術參數

射頻電源:13.56 MHz,功率自行設定;

真空泵:干泵,<40 Pa ;

清洗倉有效尺寸:長 480 mm,寬 300 mm,高330mm;

清洗層數:1~6 層,可根據產品規格定制清洗架;

射頻清洗時間:自行設定,連續可調;

清洗效果:單層式清洗,水滴角<30°。

3.3 清洗實驗

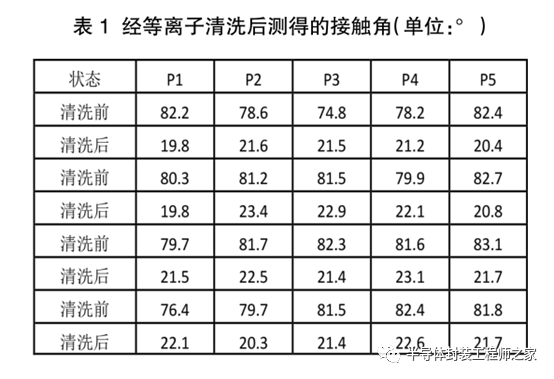

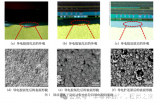

本次試驗采用芬蘭產的 THETA 型號接觸角測試儀對實驗材料進行水滴角的測量。

(1)在材料未進行等離子清洗前,對材料表面進行水滴角的測量,測得的接觸角為 80°左右;

(2)在線等離子清洗機實驗時采用的功率為300 W,真空度為 100 Pa,工藝氣體選擇氬氫混合氣,流量為 10 ml/min,清洗時間為 20 s。材料經過等離子清洗后,測得的接觸角均在 23°以下,如表 1所示。

通過接觸角實驗清洗前后測試結果可知,經過在線式等離子機清洗后,引線框架上的接觸角由未清洗前的 83°降低到了清洗后的 23°以下,這說明通過在線等離子機清洗能夠有效去除框架表面的各種污染物,從而提高焊線的強度,降低封裝過程中芯片分層現象。

4 結束語

通過對等離子清洗前后引線框架水滴角對比試驗的分析與研究,發現清洗后的引線框架水滴角會有明顯的減小,能有效地去除其表面的污染物及顆粒物,有利于提高引線鍵合的強度和降低封裝過程中芯片分層的發生,這對于提高芯片本身的質量和使用壽命提供了相應的參考依據,為提高封裝產品的可靠性提供了一定的借鑒。

-

IC

+關注

關注

36文章

5982瀏覽量

176224 -

等離子

+關注

關注

2文章

236瀏覽量

30006 -

封裝工藝

+關注

關注

3文章

58瀏覽量

8012

原文標題:等離子清洗在引線框架封裝工藝中的應用

文章出處:【微信號:半導體封裝工程師之家,微信公眾號:半導體封裝工程師之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

引線框架質量大起底:影響集成電路的關鍵因素

引線鍵合的基礎知識

功率模塊封裝工藝

等離子清洗技術原理??、分類???、特點、應用及發展趨勢

等離子清洗及點膠軌跡對底部填充膠流動性的影響

mos封裝工藝是什么,MOS管封裝類型

半導體封裝工藝面臨的挑戰

半導體封裝工藝的研究分析

等離子清洗在引線框架封裝工藝中的應用

等離子清洗在引線框架封裝工藝中的應用

評論